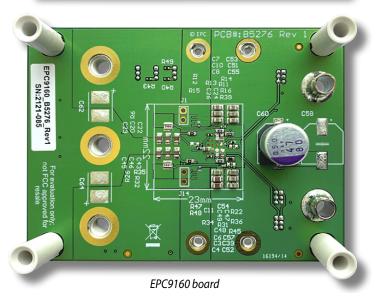

# EPC9160: 9 V–24 V to Dual Output 5 V/ 3.3 V Synchronous Buck Converter Evaluation Board Quick Start Guide

September 2, 2021

Version 1.0

#### **DESCRIPTION**

The EPC9160 is a 9–24 V to dual output 5 V/ 3.3 V 15 A synchronous buck converter. EPC9160 is designed with EPC2055 enhancement mode eGaN® FET and LTC7890 two phase analog buck controller with integrated GaN drivers. EPC9160 features:

- Wide V<sub>IN</sub> range: 9 V-24 V

- Analog controller with integrated driver optimized for eGaN® FET

- High efficiency: >93 % for 5 V output and 24 V input

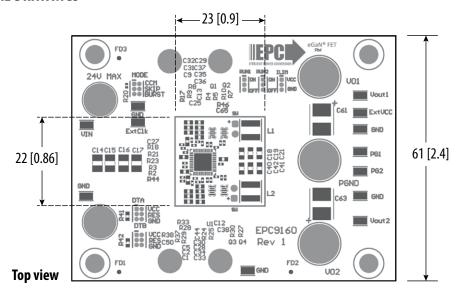

- High Switching frequency (2 MHz) and small size (23 mm x 22 mm power stage)

- · Reconfigurable light load operating mode and adjustable dead time

- Other functions:

- o UVLO

- o Over-current protection

- o Power good output

- o External synchronization

Table 1: Electrical Characteristics ( $T_a = 25$ )

| Symbol                   | Parameter                               | Conditions                   | Min | Тур  | Max               | Units |

|--------------------------|-----------------------------------------|------------------------------|-----|------|-------------------|-------|

| V <sub>IN</sub>          | Input Voltage                           |                              | 9   |      | 24                |       |

| V <sub>IN,on, rise</sub> | Input UVLO turn on voltage rising edge  |                              |     | 9    |                   | ٧     |

| V <sub>IN,on, fall</sub> | Input UVLO turn on voltage falling edge |                              |     | 8    |                   |       |

| I <sub>OUT</sub>         | Output Current                          | 400 LFM air flow recommended |     |      | 15 <sup>[1]</sup> | Α     |

| $f_S$                    | Switching<br>Frequency                  | Mode = CCM                   |     | 2000 |                   | kHz   |

[1] The maximum current capability is dependent on thermal conditions. The FET temperature should be monitored to ensure the maximum temperature does not exceed the rating in the datasheet, in particular when the input voltage is higher than 54 V, the maximum output current will be reduced.

#### REGULATORY INFORMATION

This power module is for evaluation purposes only. It is not a full-featured power module and cannot be used in final products. No EMI test was conducted. It is not FCC approved.

#### **QUICK START PROCEDURE**

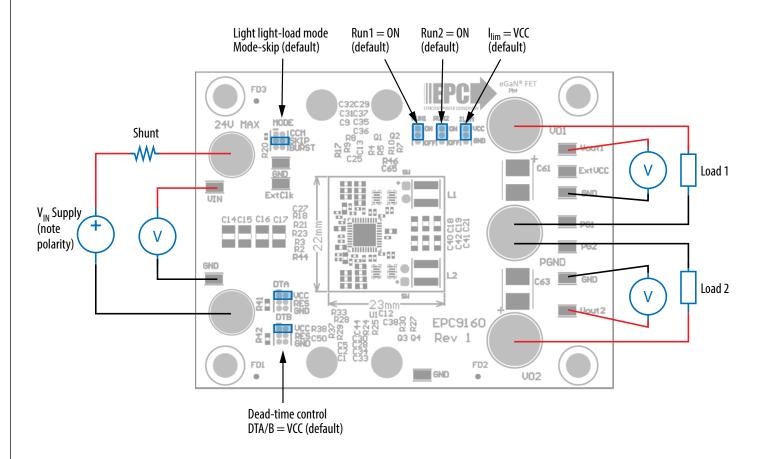

The evaluation board EPC9160 is easy to set up to evaluate the performance of the EPC2055 eGaN FETs and directly drive from the controller IC. Refer to figure 1 for proper connect and measurement setup and follow the procedure below:

- 1. Check if the jumpers are at its default location as shown in figure 1.

- 2. With power off, connect the input power supply between V<sub>IN</sub> (J9) and GND (J10) banana jacks as shown. A shunt can be inserted to measure input current.

- 3. With power off, connect a programmable load as needed between Vout1 and/or Vout2 (J4 and J8) and GND (J18) as shown in figure 1. **Note: Initial no load**.

- 4. Turn on the supply voltage beyond UVLO to the required value. The applied voltage should not exceed 24 V under any conditions.

- 5. Check the output voltages are regulated to 5 V and 3.3 V respectively and switching at no-load. If output voltage is not observed, please carefully re-examine the circuit connections.

- 6. Activate the programmable load and set to the desired current ensuring the current does not exceed the maximum ratings.

- 7. Once operational, adjust the bus voltage and load current within the allowed operating range and observe the output switching behavior, efficiency and other parameters as desired.

- 8. For measuring switch node waveforms, please use J1 and J14 without any ground lead to the scope. Please note polarity.

- 9. For shutdown, please follow steps in reverse of step 1-5. For custom configuration please refer the optional configuration section.

Figure 1: Proper connection set up and default jumper positions

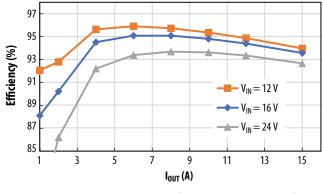

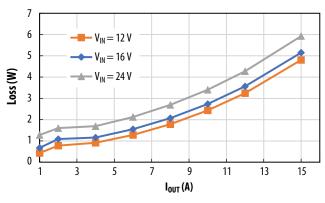

## **EXPERIMENTAL RESULTS**

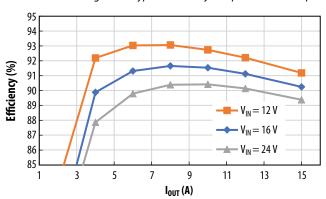

Figure 2a: Typical efficiency and power losses for phase 1: Vo1 = 5 V (mode = skip, DTA/B = VCC, Vo1 is ON, Vo2 is OFF)

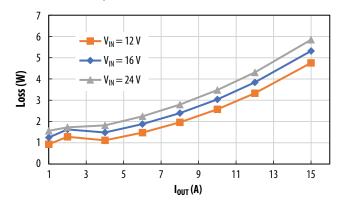

Figure 2b: Typical efficiency and power losses for phase 2: Vo2 = 3.3 V (mode=skip, DTA/B = VCC, both phase is ON)

## **Typical load transient response**

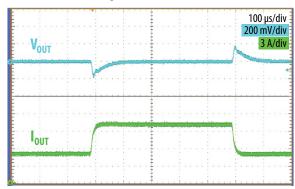

Figure 3: Typical load transient response:  $V_{IN} = 24 \text{ V}$ , Vo2 = 3.3 V, 5 A to 10 A load step,  $di/dt = 0.5 \text{ A}/\mu \text{s}$

# Startup waveform

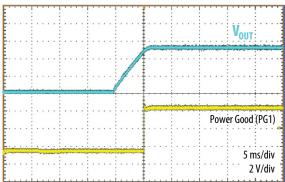

Figure 4: Startup waveform:  $V_{IN} = 24 \text{ V}$ ,  $V_{OUT1} = 5 \text{ V}$  ( $I_{lim} = VCC$ )

## **Typical load regulation**

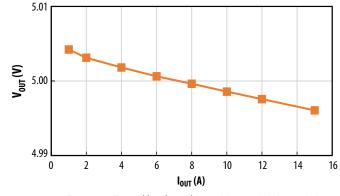

Figure 5a: Typical load regulation:  $V_{IN} = 24 \text{ V}$ ,  $V_{OUT1} = 5 \text{ V}$

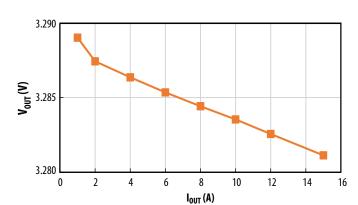

Figure 5b Typical load regulation:  $V_{IN} = 24 \text{ V}$ ,  $V_{OUT2} = 3.3 \text{ V}$

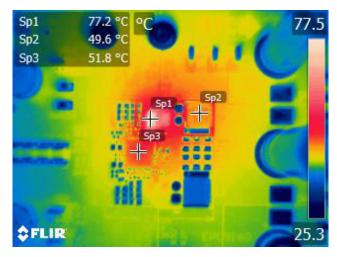

#### Thermal performance

Figure 6:  $V_{IN}$  = 24 V,  $V_{OUT2}$  = 3.3 V,  $I_{OUT}$  = 10 A, No forced air flow (natural convection)

## **CUSTOM CIRCUIT CONFIGURATIONS**

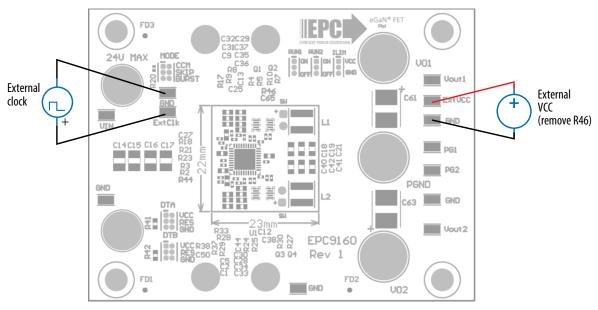

Figure 7: An example custom circuit connection with external VCC and clock

#### **Input UVLO adjustment**

The  $V_{\rm IN}$  UVLO threshold voltage can be set by R48 and R49. If needed, a UVLO voltage can be set by changing R48 and R49: Please refer to LTC7890 datasheet for more information.

$$UVLO \ rising = 1.2 \ V \left(1 + \frac{R48}{R49}\right)$$

$$UVLO \ falling = 1.1 \ V \left(1 + \frac{R48}{R49}\right)$$

### Switching frequency adjustment

If needed, switching frequency can be modified by changing the value of R21. Please refer to LTC7890 datasheet for more information.

$$f_{\rm S}$$

(MHz)  $pprox \frac{37 \, ({\rm MHz})}{{\rm R21} \, ({\rm k}\Omega)}$

#### **External VCC**

While the chip can be solely powered by the main power supply  $V_{IN}$ , the losses may be high for high input voltage. By default, Ext VCC is connected to phase 1 output (R46 = 0  $\Omega$ ). The user can also connect an external power supply (for e.g. 5 V) to Ext VCC (TP6) and GND as shown in figure 7 and test phase 2 only. Please remove R46 before doing so. Please refer to LTC7890 datasheet for more information.

#### **External clock synchronization**

Some system requires power supplies be synchronized. The user may install jumper R23, and an external clock can be connected to synchronize the PWM to an external clock as shown in figure 7. Please refer to the datasheet of LTC7890 for more details.

#### **Deadtime adjustment**

Dead time control is important for eGaN FETs, particularly at high frequencies and high current applications. The dead time is controlled by the resistance values of R41 and R42 for rising and falling edges respectively. Additionally, Jumper J21 and J13 can be used to enable adaptive and fixed dead time control as supported by the LTC7890 controller. Please refer to LTC7890 datasheet for more information.

#### THERMAL MECHANICAL DRAWINGS

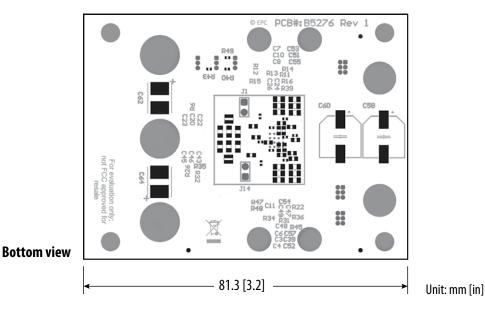

Figure 9: Mechanical dimensions

### THERMAL MANAGEMENT (optional)

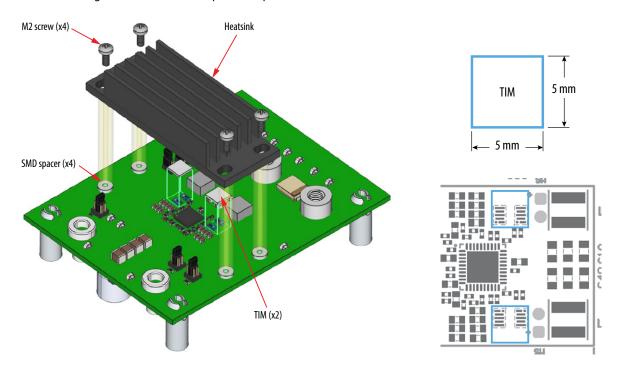

The EPC9160 is intended for bench evaluation at room temperature with forced air convection cooling. A heatsink is not required but will significantly improve convective heat dissipation from the topside of the FET and increase the current capacity of these devices.

The EPC9160 board is equipped with four mechanical SMD spacers that can be used to easily attach a standard eighth-brick converter heatsink using standard M2 screws (See Figure 10). Thermal interface material (TIM) pads (2x) are required for good thermal conductance between the FETs and the heatsink bottom surface. See Figure 10 for minimum required TIM pad size.

Figure 10: Exploded 3D assembly of heat sink installment and locations of TIM material

The following heat sink is recommended for EPC9160:

Wakefield P/N: 567-45AB

A TIM is required between the FETs and the heatsink. The choice of TIM needs to consider the following characteristics.

- Mechanical compliance During the attachment of the heat spreader, the TIM underneath is compressed from its original thickness to the vertical gap distance between the spacers and the FETs. This volume compression exerts a force on the FETs. A maximum compression of 2:1 is recommended for maximum thermal performance and to constrain the mechanical force which maximizes thermal mechanical reliability.

- Electrical insulation The backside of the eGaN FET is a silicon substrate that is connected to source and thus the upper FET in a half-bridge configuration is connected to the switch-node. To prevent short-circuiting the switch-node to the grounded thermal solution, the TIM must be of high dielectric strength to provide adequate electrical insulation in addition to its thermal properties.

- Thermal performance The choice of thermal interface material will affect the thermal performance of the thermal solution. Higher thermal conductivity materials is preferred to provide higher thermal conductance at the interface.

EPC recommends the following thermal interface materials (TIM) for EPC9160:

t-Global P/N: TG-A1780 x 0.5 mm (highest conductivity of 17.8 W/m·K)

t-Global P/N: TG-A6200 x 0.5 mm (moderate conductivity of 6.2 W/m·K)

**NOTE**. The EPC9160 evaluation board does not have any current or thermal protection on board. For more information regarding the thermal performance of EPC eGaN FETs, please consult: D. Reusch and J. Glaser, *DC-DC Converter Handbook, a supplement to GaN Transistors for Efficient Power Conversion,* First Edition, Power Conversion Publications, 2015.

For support files including schematic, Bill of Materials (BOM), and gerber files please visit the EPC9160 landing page at: https://epc-co.com/epc/products/demo-boards/epc9160

## **For More Information:**

Please contact **info@epc-co.com** or your local sales representative

Visit our website:

www.epc-co.com

Sign-up to receive EPC updates at bit.ly/EPCupdates

EPC Products are distributed through Digi-Key. **www.digikey.com**

#### **Evaluation Board Notification**

**The EPC9160 board is intended for product evaluation purposes only. It is not intended for commercial use nor is it FCC approved for resale**. Replace components on the Evaluation Board only with those parts shown on the parts list (or Bill of Materials) in the Quick Start Guide. Contact an authorized EPC representative with any questions. This board is intended to be used by certified professionals, in a lab environment, following proper safety procedures. Use at your own risk.

As an evaluation tool, this board is not designed for compliance with the European Union directive on electromagnetic compatibility or any other such directives or regulations. As board builds are at times subject to product availability, it is possible that boards may contain components or assembly materials that are not RoHS compliant. Efficient Power Conversion Corporation (EPC) makes no quarantee that the purchased board is 100% RoHS compliant.

The Evaluation board (or kit) is for demonstration purposes only and neither the Board nor this Quick Start Guide constitute a sales contract or create any kind of warranty, whether express or implied, as to the applications or products involved.

Disclaimer: EPC reserves the right at any time, without notice, to make changes to any products described herein to improve reliability, function, or design. EPC does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, or other intellectual property whatsoever, nor the rights of others.