# EPC GaN Transistor Application Readiness: Phase One Testing

#### Yanping Ma PhD, Director of Quality and Reliability, Efficient Power Conversion Corporation

Efficient Power Conversion Corporation's (EPC) enhancement mode Gallium Nitride (GaN) power transistors offer performance well beyond the realm of silicon-based MOSFETs. Standard power converter topologies can greatly benefit from the added performance and realize improved efficiency while maintaining the simplicity of older designs.

Although similar to standard power MOSFETs, enhancement mode GaN transistors are a relatively new technology. Operating life information is not yet at the level available to users of silicon power MOSFETs. EPC's risk-reduction results to date include the placement of over 380 devices, at their maximum operating ratings on a wide variety of stress tests. Over 275,000 total device hours support our product's readiness for commercial use. The conversion of power MOSFET-based systems can begin with acceptable levels of risk.

In this paper, the suitability for reliable and commercial use of EPC technology will be addressed in detail.

#### **GaN OVERVIEW**

The fundamental properties of GaN make it an ideal starting material for high power transistors. Some of these properties are derived from the crystal's wide band-gap of 3.4 eV. This wide band-gap creates an extremely high electric breakdown field (about 10 times of silicon), making GaN an outstanding material for high voltage transistors and for operation at elevated temperatures. The electron density resulting from the polarization-induced field in the GaN structure is very high (~10<sup>13</sup>/cm<sup>2</sup>). The high two-dimensional electron gas (2DEG) density and high electron mobility transistors (HEMTs)<sup>1</sup> very

attractive for low on-state resistance power transistors with high breakdown voltage and high current density capability.

# GaN Devices Have Been the Subject of Intense Research for the Past Decade

Research and development projects sponsored by the Defense Advanced Research Agency (DARPA) including teams from Triquint, Raytheon and Northrop Grumman have resulted in estimated transistor lifetime using single failure mode Arrhenius elevated temperature testing of >100,000 hours at a junction temperature of 150°C. This represents a five order of magnitude increase in transistor lifetime,

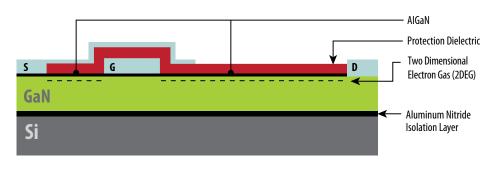

Figure 1: GaN on silicon devices have a very simple structure similar to a lateral DMOS device and are built in a standard CMOS foundry

taking GaN from a laboratory novelty to being able to compete with mature technologies<sup>2,4</sup>. Commercial GaN HEMTs are already available for the RF and microwave markets from companies such as Nitronex<sup>3</sup>, RFMD<sup>4</sup>, and Eudyna<sup>5</sup>.

Although the focus of research and development has been depletion-mode or d-mode (normallyon) HEMTs, enhancement-mode or e-mode (normally-off) HEMT's are strongly preferred. Enhancement-mode (normally-off) HEMTs offer safer operation, greater simplicity of circuit design, and lower energy consumption. There are numerous examples in the literature regarding enhancement-mode GaN HEMTs (HEMT can be used interchangeably with HFET, heterostructure field effect transistors) including but not limited to:

- Recessed etching of the AlGaN barrier in cojunction with a Schottky gate electrode<sup>30</sup>

- Fluoride-based plasma treatment of the gate<sup>31</sup>

- E-mode HFET using p-n junction gate contact<sup>6</sup>

- E-mode HFET utilizing conductivity modulation<sup>9,10</sup>

#### **EPC PRODUCT INTRODUCTION**

Efficient Power Conversion enhance-mode HFETs were commercialized in June of 2009. Figure 1 shows a schematic structure of an EPC device which is similar to a lateral DMOS silicon device and fabricated on silicon substrates, employing standard silicon processes. The cost of EPC products is therefore comparable to silicon technologies<sup>11</sup>.

During 2009, EPC introduced ten part numbers covering 40, 60, 100, 150 and 200 volt enhancement-mode GaN power transistors. The voltage ratings, maximum  $R_{DS(on)}$ , and

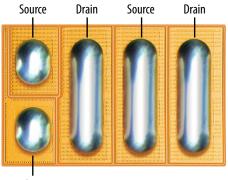

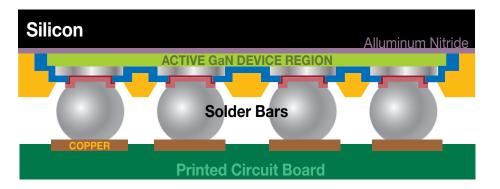

product dimensions are listed in Appendix I. EPC's GaN transistors are lateral devices with all three terminals: gate, drain, and source on the front side of the chip. The active device is isolated from the substrate and fully encapsulated by passivation layers on the front side as shown in Figure 2. This configuration allows EPC's GaN transistors to be used as bare die without additional packaging<sup>28</sup>. The advantages include: the elimination of plastic packages and the related performance issues, improved reliability, and cost reduction. EPC GaN transistors employ wafer-level solder line-grid-arrays as shown in Figure 3.

Gate

Figure 3: Front side view of EPC 1014, 40 V, 16 m $\Omega$  GaN transistor showing the solder line-grid-array bump design with alternating source and drain solder bars.

#### **RELIABILITY PROGRAM OVERVIEW**

The conversion of Power MOSFET-based systems to enhancement-mode GaN technology requires evidence of reliable performance. In Phase One, EPC stressed more than 380 devices for a total of more than 275,000 hours under conditions similar to power MOSFET reliability stress testing.

"Dynamic  $R_{DS(on)}$ ", specifically those conditions causing minimal shifting in device resistance, is extensively discussed in the literature and was a particular focus of the EPC Phase One reliability program<sup>12–27</sup>. EPC's devices have been designed to mitigate dynamic  $R_{DS(on)}$  and data show significantly greater stability than devices reported in the literature.

#### Dynamic R<sub>DS(on)</sub>

Dynamic  $R_{DS(on)}$  is a phenomenon whereby a device's on-resistance increases after being subjected to a drain bias. The magnitude of the increase depends on the drain-side gate edge electric field, under which electrons are accelerated and a small number remained trapped in the

Figure 2: GaN on silicon can be used as a "flip chip". The active device is isolated from the silicon substrate and can be completely encapsulated prior to singulation. When compared to plastic packages, this design reduces cost and requires less space.

EPI layer, or at the EPI surface. As the trapped electrons deplete the 2DEG,  $R_{DS(on)}$  is increased. The higher the drain pre-bias voltage, the higher the  $R_{DS(on)}$  becomes post-bias. Over time, the trapped electrons de-trap (relax) and  $R_{DS(on)}$  gradually returns to the pre-bias value.

Several companies and institutions have reported suppression of dynamic  $R_{DS(on)}$  by surface passivation<sup>20,21</sup>. Proper field-plating can also reduce the peak electric field, thereby suppressing dynamic  $R_{DS(on)}$ <sup>17</sup>. It was reported that dynamic  $R_{DS(on)}$  was much improved with GaN devices built on conductive silicon substrates compared to GaN devices built on non-conductive sapphire substrates<sup>29</sup>. This improvement is due to the conductive substrate acting as a field plate on the back side. With GaN on a conductive substrate, dynamic  $R_{DS(on)}$  was reported being influenced by the GaN EPI layer thickness.

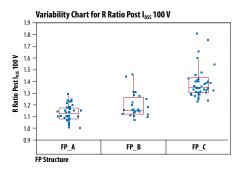

EPC products use an optimized EPI structure and EPI thickness on conductive silicon substrates to minimize dynamic  $R_{DS(on)}$ . The EPI surface is passivated with a high quality  $Si_3N_4$  layer. Field plate structures are also optimized. Figure 4 shows an example comparing field-plate structure A, B, and C that were studied during EPC product

Figure 4: Field plate has big impact on dynamic  $R_{DS(on)}$ . An example is shown comparing field-plate structure A, B, and C that were studied during product development.

development. Field-plate structure A is superior in terms of dynamic  $R_{DS(on)}$ .

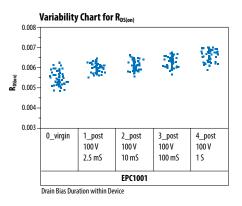

Dynamic  $R_{DS(on)}$  was evaluated on a TESEC tester.  $R_{DS(on)}$  was measured pre and post stress whilst the drain-source voltage was stepped from low

Figure 5: R<sub>DS(on)</sub> values after 100 V bias for various durations.

voltage to 30% above the rated maximum drainsource voltage. The effect of drain bias duration was also evaluated. Figure 5 shows  $R_{DS(on)}$  values after 100 V bias for various durations. Increasing drain bias duration from 2.5 mS to 1 Sec results in minimal increase in  $R_{DS(on)}$ .

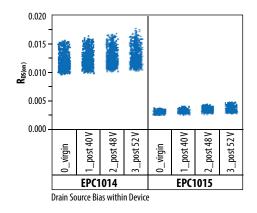

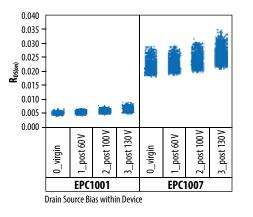

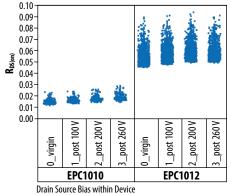

The  $R_{DS(on)}$  values post various drain biases for duration of 2.5 mS are shown in Figures 6, Figure 7, and Figure 8 for 40 V, 100 V, and 200 V product, respectively. Two device types are shown in each figure for each of the voltage ratings. The 40 V devices, EPC1014 and EPC1015, were biased to 40 V, 48 V and 52 V sequentially. The 100 V devices, EPC1001 and EPC1007, were biased to 60 V, 100 V, and 130 V sequentially. The 200 V devices, EPC1010 and EPC1012, were biased to 100 V, 200 V, and 260 V sequentially. The degree of dynamic  $R_{DS(on)}$  was similar for all product types. The increase in  $R_{DS(on)}$  for the main population was approximately 10% with a tail at higher or lower values.

Figure 6: The R<sub>DS(on)</sub> values post various drain biases are shown for EPC1014 and EPC1015, the two 40 V products.

#### RELIABILITY TESTING OVERVIEW AND RESULTS

Long term stability under high drain-source bias was evaluated by subjecting devices to DC voltage equal to the maximum drain-source rated voltage and temperature (high temperature reverse bias, or HTRB). Gate reliability was evaluated by subjecting devices to various gate stresses at elevated temperature (high temperature gate bias, or HTGB). Environmental reliability was evaluated with temperature cycling (TC) and temperature-humidity-with-bias (THB). Devices were also subjected to operating life tests involving devices in actual power supplies running at high voltage and high current.

A list of the reliability tests performed, the applicable standards, the device types evaluated, and the stress conditions are listed in Appendix II. All devices tested were soldered onto Arlon 85N printed circuit boards.

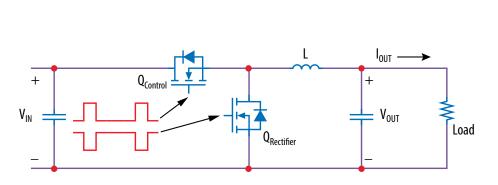

### High Temperature Reverse Bias Test (HTRB)

The impact of high drain bias on device parameters, applied for long periods of time, was evaluated with maximum rated drain-source bias applied at an ambient temperature of 125°C. Whereas there were no parametric failures out of the parts tested, there was some degree of dynamic R<sub>DSON</sub> post stress test (A 20% increase in R<sub>DSON</sub> was observed for some devices).

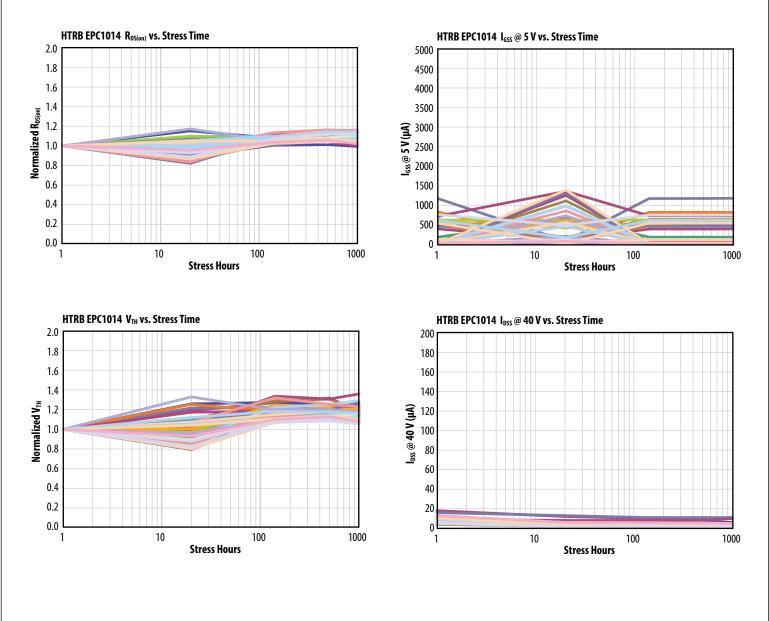

All electric parameters remained relatively constant throughout the entire stress period of 1000 hours for EPC1001 and EPC1014. Appendix IV graphically presents the stability of various device parameters during test.

Figure 7: The R<sub>DS(on)</sub> values post various drain biases are shown for EPC1001 and EPC1007, the two 100 V products.

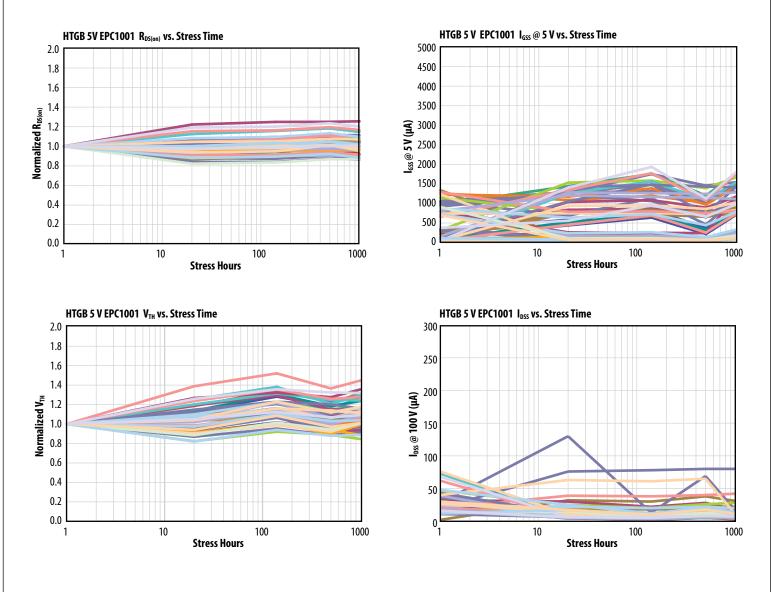

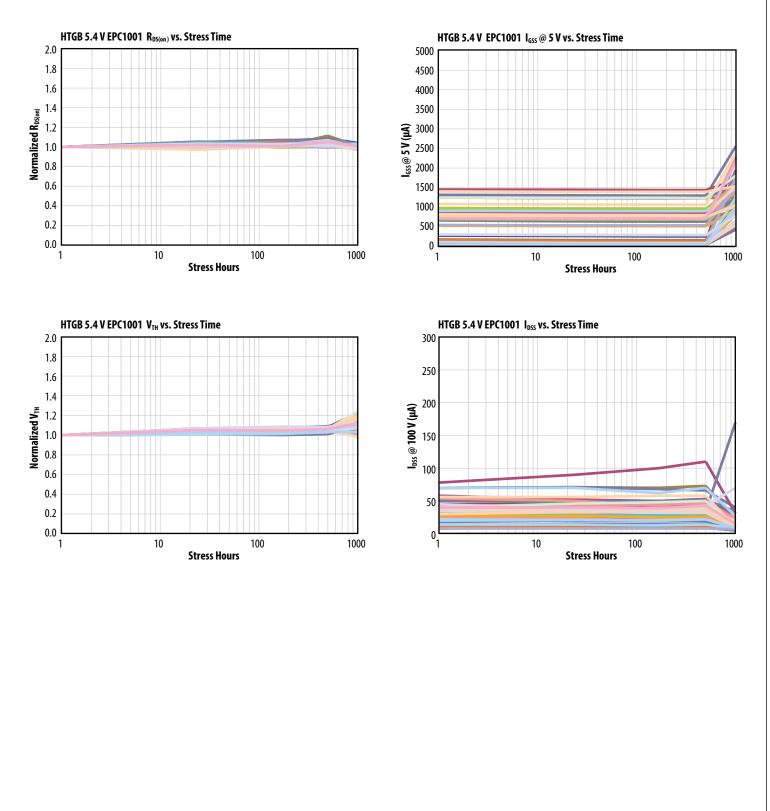

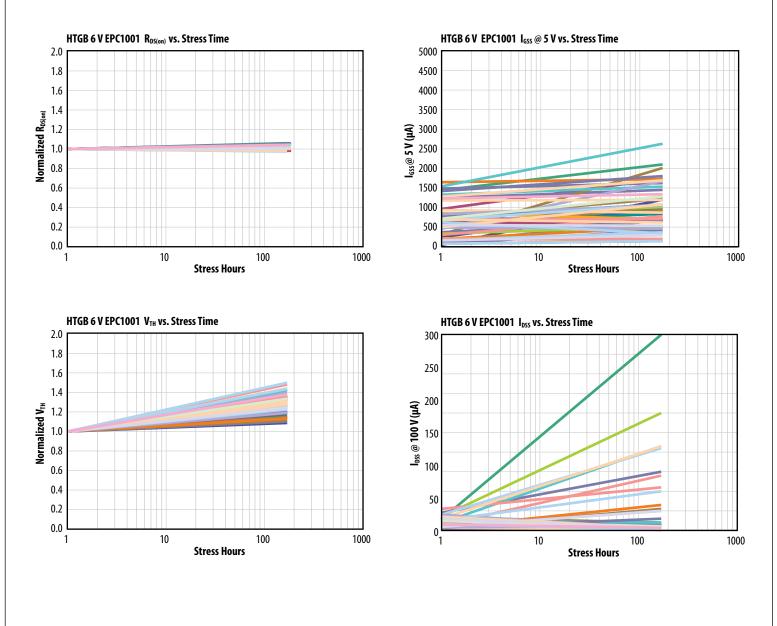

### High Temperature Gate Bias Test (HTGB)

The gate stability of EPC GaN transistors was evaluated under various gate bias conditions at 5 V, 5.4 V, and 6 V at 125°C. EPC1001 parts were used for each of the three tests. At 5  $V_{GS}$  and 5.4  $V_{GS}$  bias, all device electric parameters stayed relatively constant over the entire burn-in period of 1000 hours. It was observed though that the drain leakage increased with 6  $V_{GS}$  bias. Five parts showed higher than the datasheet limit at the 168 hours pulling point (Appendix III\*). These parts were put back on burn-in, and will be analyzed after the stress test is finished. Complete test results are presented in Appendix V.

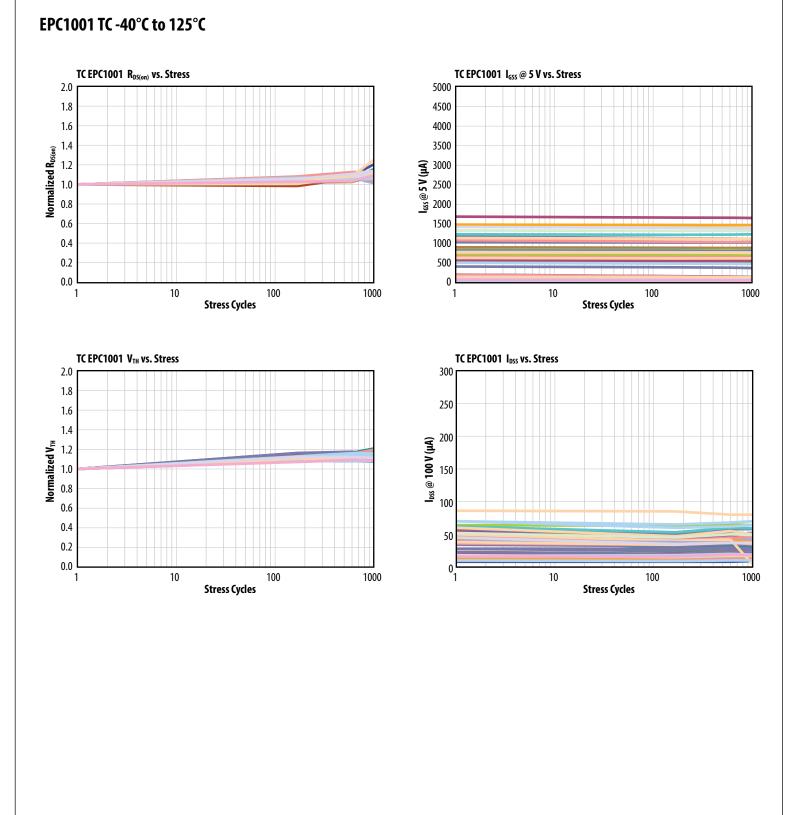

### Temp Cycle (TC)

Temperature cycling was conducted on EPC1001, a large device, and on EPC1014, a small device. These two part numbers have different bump designs and were used to check the bump joint reliability. Parts were all mounted on Arlon 85N printed circuit board material. Temperatures varied between -40°C to 125°C at a rate of two cycles per hour. No on-state resistance degradation was observed over the stress period of 1000 cycles. All electrical parameters remained constant during stress. Complete test results are shown in Appendix VI.

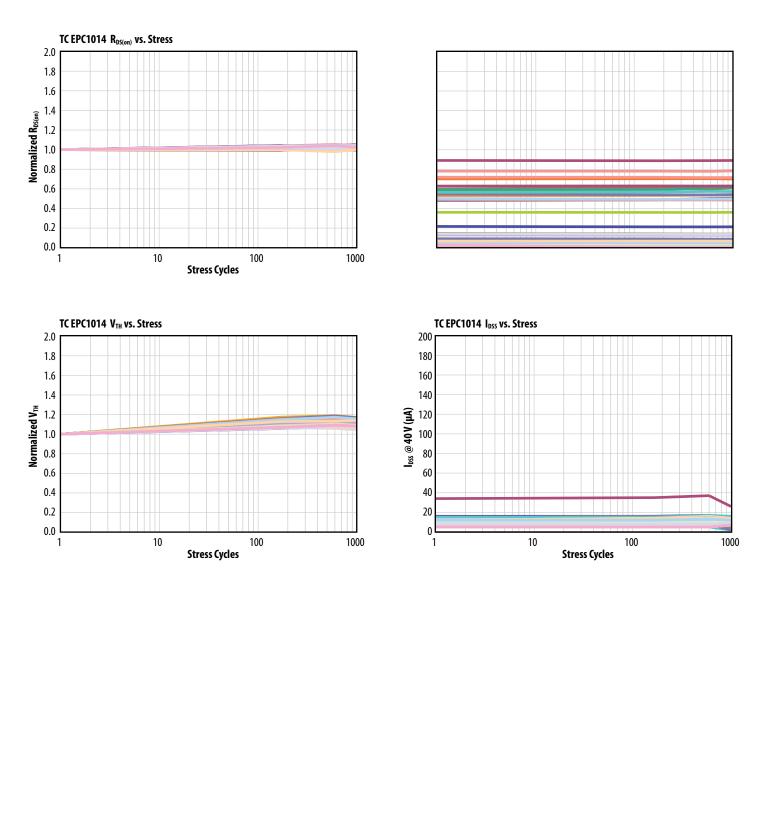

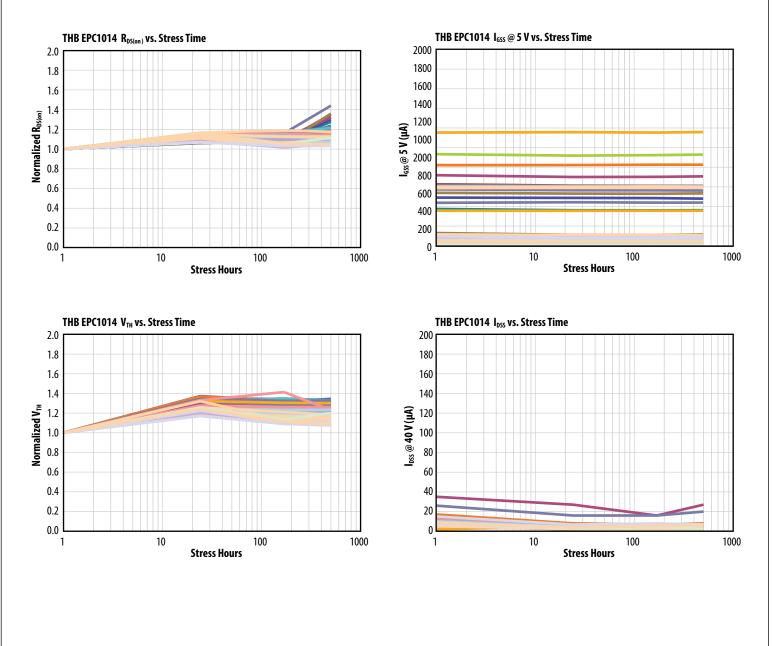

#### Temperature Humidity Bias Test (THB)

Device performance was also characterized with temperature and humidity with drain-source bias (THB). THB tests were conducted at 85°C and with 85% relative humidity. EPC1014 was on test with drain biased to the rated 40 volt.

Figure 8: The R<sub>DS(on)</sub> values post various drain biases are shown for EPC1010 and EPC1012, the two 200 V products.

At time of this writing, parts have completed 500 hours stress, and are continuing on test for 1000 hours. All device electric parameters remained relatively constant over the stress period. Complete test results are shown in Appendix VII.

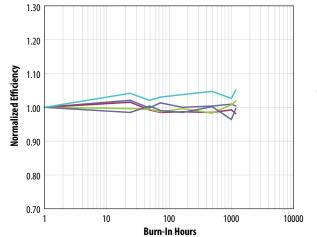

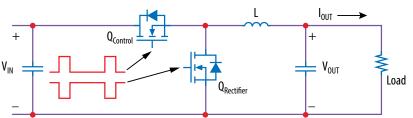

#### **Power Supply Operating Life Test**

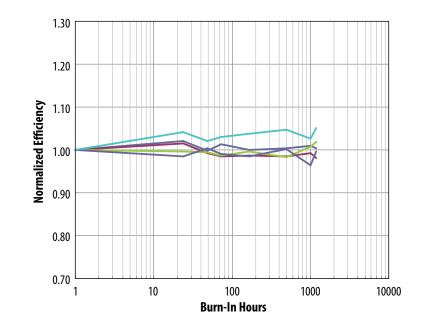

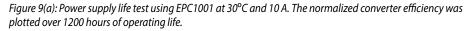

To demonstrate the performance of the GaN transistors in-circuit, and to test the reliability under high-stress operating life, EPC built 48 V to 1 V power supply boards using a "buck converter" topology (see figure 9). For the burn-in test, EPC1001 (100 V, 7 m $\Omega$ ) transistors were used for both the control transistor and rectifier switches. This kind of test is particularly useful because, in a standard "buck" topology DC-DC converter operated at the high  $V_{IN}/V_{OUT}$  ratio of 48 V to 1 V, the control transistor is turned ON at a very low duty cycle (~2%). Conversely, the rectifier transistor is turned ON with a very high duty cycle (~98%). This test therefore stresses devices both at high drain-source voltage and high drain current under actual, fast-switching conditions. The converter was operated at 48 V input voltage, 1 V output voltage, 10 A output current, and at a switching frequency of 250 kHz. The circuit efficiency was measured at time-zero hour, 24, 48, 72, 168, 500, 1000, and 1200 hours. The normalized efficiency vs. burn-in hours is plotted in Figure 9(a), and the power supply test circuit is shown in Figure 9(b). The efficiency of all the power supply boards stayed virtually unchanged over the entire burn-in period.

#### **FUTURE WORK**

EPC has plans for a much broader and deeper study of the reliability of enhancement mode GaN power transistors. In Phase 2, EPC will complete the 1000 hour/1000 cycle testing on all product types. Further work will also be done to develop acceleration factors and models that allow users to determine suitability for various applications beyond basic commercial use.

Dynamic  $R_{DS(on)}$  will continue to be investigated with the goal of further minimizing this characteristic of EPC GaN devices.

EPC will convert to lead free solder in the second half of 2010. This conversion will be accompanied by additional testing at 150°C to verify this change does not degrade device characteristics under stress. At that time, EPC will also conduct temperature cycling tests on a wide variety of substrate materials to validate compatibility.

#### **SUMMARY**

EPC's enhancement mode Gallium Nitride transistors bring tremendous performance and size advantages over silicon power MOSFETs. These advantages can be used to improve system efficiency, reduce system cost, reduce size, or a combination of all three. Because EPC's products were designed as power MOSFET replacements, designers can use their existing building blocks, skills and knowledge with only minor changes. Reliability testing has also demonstrated that the technology is now ready for general commercial use.

#### The future of GaN transistors is now.

Figure 9(b): Power supply test circuit

### References

- 1. M. Asif Khan, A. Bhattarai, J.N. Kuznia, and D.T. Olson, "High Electron Mobility Transistor Based on a GaN-AlxGa1-xN Heterojunction," Appl. Phys. Lett., vol. 63, no. 9, 1993, pp. 1214-1215.

- 2. M.J. Rosker, "The Present State of the Art of Wide-Bandgap Semiconductors and Their Future," in Proc. IEEE Radio Freq. Integr. Circuit Symp., 2007, pp. 159-162.

- 3. http://www.nitronex.com

- 4. http://ir.rfmd.com/releasedetail.cfm?ReleaseID=412122

- 5. http://www.mwrf.com/Article/ArticleID/13434/13434.html

- 6. X. Hu, J. Simin, J. Yang, M. Asif Khan, R. Gaska, and M.S. Shur, "Enhancement Mode AlGaN/GaN HFET with Selectively Grown PN Junction Gate," Electronics Letters, 2000, vol. 36, no. 8, pp. 753-754.

- 7. N. Tsuyuchi, K. Nagamatsu, Y. Hirose, M, Iwaya, S. Kamiyama, H. Amano, and I. Akasaki, "Low-Leakage-Current Enhancement-Mode AlGaN/GaN Heterostructure Field-Effect Transistor Using p-Type Gate Contact," Jpn. J. Appl. Phys., vol. 45, 2006, pp. L319-L321.

- 8. T. Fujii, N. Tsuyukuchi, M. Iwaya, S. Kamiyama, H. Amano, and I. Akasaki, "High on/off Ratio in Enhancement –Mode AlxGa1-xN/GaN Junction Heterostructure Field-Effect Transistors with p-Type GaN Gate Contact," Jpn J. Appl. Phys., vol. 45, no. 39, 2006, pp. L1048-L1050.

- 9. Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagihar, T. Ueda, T. Tanaka, and D. Ueda, "Gate Injection Transistor (GIT) A Normally-off AlGaN/GaN Power Transistor Using Conductivity Modulation," IEEE Transactions on Electron Devices, vol. 54, no. 12, 2007, pp. 3393-3399.

- 10. Y. Uemoto, T. Ueda, T. Tanaka, D. Ueda, "Recent Advances of High Voltage AlGaN/GaN Power HFETs," in Proc. of SPIE Vol. 7216, 721606, 2009, pp.1-11.

- 11. A. Lidow, "Is it the End of the Road for Silicon in Power Conversion?" CIPS 2010 Conference Proceedings, March 2010, Nurnberg, Germany.

- 12. W. Saito, M. Kuraguchi, Y. Takada, K. Tsuda, T. Domon, I. Omura, and M. Yamaguchi, "380 V/1.9A GaN power-HEMT: Current collapse phenomena under high applied voltage and demonstration of 27.1 MHz class-E amplifier," in IEDM Tech. Dig., 2005, pp. 597-600.

- 13. S. Singhal, J.C. Roberts, P. Rajagopal, T. Li, A.W. Hanson, R. Therrien, J.W. Johnson, I.C. Kizilyalli, K.J. Linthicum, "GaN-on-Si failure mechanisms and reliability improvements," in Proc. IEEE Int. Rel. Phys. Symp., 2006, pp. 95-98.

- 14. S. Singhal, T. Li, A., Chaudhari, A.W. Hanson, R. Theerien, J.W. Johnson, W. Nagy, J. Marquart, P. Rajagopal, J.C. Roberts, E.L. Piner, I.C. Kizilyalli, K.J. Linthicum, "Reliability of Large Periphery GaN-on-Si HFETs," Microelectronics Reliability 46, 2006, pp. 1247-1253.

- 15. P. Saunier, C. Lee, A. Galistreri, D. Dumka, J. Jimenez, H.Q. Tserng, M.Y. Kao, P.C. Chao, K. Chu, A. Souzis, I. Eliashevich, S. Guo, J. del Alama, J. Joh, M. Shur, "Progress in GaN Performances and Reliability," in Proc. Device Res. Conf., 2007, pp. 35-36.

- 16. G. Meneghesso, G. Verellesi, F. Danesin, F. Rampazzo, F. Zanon, A. Tazzoli, M. Meneghini, and E. Zanoni, "Reliability of GaN high-electron-mobility transistors: state of the art and perspectives," IEEE Transactions on Device and Materials Reliability, vol. 8, no. 2, 2008, pp. 332-343.

- 17. W. Saito, T. Nitta, Y. Kakiuchi, Y. Saito, K. Tsuda, I. Omura, and M. Yamaguchi, "On-Resistance Modulation of High Voltage GaN HEMT on Sapphire Substrate Under High Applied Voltage," IEEE Electron Device Letters, vol. 28, no. 8, 2007, pp. 676-678.

- 18. D. Marcon, A. Lorenz, J. Derluyn, J. Das, F. Medjdoub, K. Cheng, S. Degroote, M. Leys, R. Mertens, M. Germain, and G. Borghs, "GaN-on-Si HEMT stress under high electric field condition," Phys. Status Solidi C, vol. 6, 2009, pp. S1024-S1028.

- 19. R. Vetury, N.Q. Zhang, S. Keller, U.K. Mishra, "The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs," IEEE Transactions on Electron Devices, vol. 48, no. 3, 2001, pp. 560-566.

- 20. L. Ma, Y. Wang, T.Y. Guo, J. Lu, Z.B. Hao, Y. Luo, and Z.P. Yu, "Trap Related Current Collapse Effects in GaN HEMTs," IEEE Conf. on Electron Devices and Solid State Circuits, 2005, pp. 795-798.

- 21. T. Mizutani, Y. Ohno, M. Akita, S. Kishimoto, and K. Maezawa, "A Study on Current Collapse in AlGaN/GaN HEMTs Inducted by Bias Stress," IEEE Transactions on Electron Devices, Vol. 50, No. 10, 2003, pp. 2015-2020.

- 22. L. Shen, S. Heikman, B. Moran, et al., "AlGaN/AIN/GaN High-Power Microwave HEMT," IEEE Electron Device Letters., vol. 22, 2001, pp.457-459.

- 23. Y.C. Chou, D. Leung, I Smorchkova, M, Wojtowicz, R. Grundbacher, L. Callejo, Q. Kan, R. Lai, P.H. Liu, D. Eng, A. Oki, "Degradation of AlGaN/GaN HEMTs Under Elevated Temperature Life testing," Microelectronics Reliability, vol. 44, 2004, pp. 1033-1038.

- 24. N. Shgaier, M. Trabelsi, N. Yacoubi, J.M. Bluet, A. Souifi, G. Guillot, C. Gaquiere, J.C. DeJaeger, "Traps Centers and Deep Defects Contribution in Current Instabilities for AlGaN/GaN HEMT's on Silicon and Sapphire Substrates," Microelectronics Journal 37, 2006, pp. 363-370.

- 25. J. Joh, and J. del Alamo, "Mechanism for Electrical Degradation of GaN High-Electron Mobility Transistors," in IEDM Tch. Dig., 2006, pp. 415-418.

- 26. S.Y. Park, C. Floresca, U. Chowdhury, J.L. Jimenez, C. Lee, E. Beam, P. Saunier, T. Balistreri, M.J. Kim, "Physical Degradation of GaN HEMT Devices Under Drain Bias Reliability Testing," Microelectronics Reliability, vol. 49, 2009, pp. 478-483.

- 27. D. Kumar Sahoo, R.K. Lal, H. Kim, V. Tilak, and L.F. Eastman, "High-field effects in silicon nitride passivated GaN MODEFTs," IEEE Transactions on Electron Devices, vol. 50, no. 5, 2003, pp. 1163-1170.

- 28. A.M. Conway, M. Chen, P. Hashimoto, P.J. Willadsen, and M. Micovic, "Failure Mechanisms in GaN HFETs under Accelerated RF Stress," CS MANTECH Conference, May 14-17, 2007, Austin Texas.

- 29. N. Ikeda, S. Kaya, J. Li, Y. Sato, S. Kato, S. Yoshida, "High power AlGaN/GaN HFET with a high breakdown voltage of over 1.8KV on 4 inch Si substrate and suppression of current collapse," Proceedings of the 20th International Symposium on Power Semiconductor Devices and IC's, 2008, pp. 287-290.

- 30. V. Kumar, A. Kuliev, T. Tanaka, Y. Otoki, I. Adesida, "High transconductance enhancement-mode AlGaN/GaN HEMTs on SiC substrate," Electronics Letters, vol. 39, no. 24, 2003, pp. 1758-1760.

- 31. Y. Cai, Y. Zhou, K. J. Chen, K. M. Lau, "High Performance Enhancement-Mode AlGaN/GaN HEMT Using Fluoride-Based Plasma Treatment," IEEE Electron Device Letters, vol. 26, no. 7, 2005, pp. 435-437.

# Appendix

| APPENDIX I:    |                                     |

|----------------|-------------------------------------|

| APPENDIX II:   | Reliability Test Table              |

| APPENDIX III:  | Reliability Results Table           |

| APPENDIX IV:   |                                     |

| APPENDIX V:    |                                     |

| APPENDIX VI:   |                                     |

| APPENDIX VII:  | THB Results                         |

| APPENDIX VIII: | Power Supply Operating Life Results |

I

## Appendix I: Product Matrix Table

| Part Number   | Voltage Rating | R <sub>DS(on)</sub> Max | Package Dimensions |  |

|---------------|----------------|-------------------------|--------------------|--|

| rait Nulliber | (V)            | (mΩ)                    | (mm x mm)          |  |

| EPC1014       | 40             | 16                      | LGA 1.7 x 1.1      |  |

| EPC1015       | 40             | 4                       | LGA 4.1 x 1.6      |  |

| EPC1009       | 60             | 30                      | LGA 1.7 x 1.1      |  |

| EPC1005       | 60             | 7                       | LGA 4.1 x 1.6      |  |

| EPC1007       | 100            | 30                      | LGA 1.7 x 1.1      |  |

| EPC1001       | 100            | 7                       | LGA 4.1 x 1.6      |  |

| EPC1013       | 150            | 100                     | LGA 1.7 x 0.9      |  |

| EPC1011       | 150            | 25                      | LGA 3.6 x 1.6      |  |

| EPC1012       | 200            | 100                     | LGA 1.7 x 0.9      |  |

| EPC1010       | 200            | 25                      | LGA 3.6 x 1.6      |  |

# Appendix II: Reliability Test Table

| Reliability Stress Test              | Applicable Standard   | Product          | Stress Conditions                                    |

|--------------------------------------|-----------------------|------------------|------------------------------------------------------|

| High Temperature Reverse Bias (HTRB) | JEDEC Std JESD22-A108 | EPC1001, EPC1014 | 100% rated drain bias, 125°C                         |

| High Temperature Gate Bias (HTGB)    | JEDEC Std JESD22-A108 | EPC1001          | 5 V, 5.4 V, 6 V gate bias, 125°C                     |

| Temperature Cycling (TC)             | JEDEC Std JESD22-A104 | EPC1001, EPC1014 | -40°C to 125°C, 2 cycles per hour                    |

| Temperature Humidity Bias (THB)      | JEDEC Std JESD22-A101 | EPC1014          | 85°C/85 RH, rated drain bias or max 100 V drain bias |

| Power Supply Operating Life          |                       | EPC1001          | 10 A, 250 kHz, 30°C                                  |

# Appendix III: Reliability Results Table

|                         | De t Nevel en                       |                | # of Fail at Read Point |         |         |          |

|-------------------------|-------------------------------------|----------------|-------------------------|---------|---------|----------|

| Stress Test             | Test Part Number Sample Size        | 24 HR          | 168 HR                  | 500 HR  | 1000 HR |          |

| HTRB                    | EPC1001                             | 45             | 0                       | 0       | 0       | 0        |

| HTRB                    | EPC1014                             | 50             | 0                       | 0       | 0       | 0        |

| Stress Test Part Number | Derthert                            | Committe Circo | # of Fail at Read Point |         |         |          |

|                         | Sample Size                         | 24 HR          | 168 HR                  | 500 HR  | 1000 HR |          |

| HTGB 5 V                | EPC1001                             | 45             | 0                       | 0       | 0       | 0        |

| HTGB 5.4 V              | EPC1001                             | 45             | 0                       | 0       | 0       | 0        |

| HTGB 6 V                | EPC1001                             | 50             | 0                       | 5*      |         |          |

|                         | Deut Nous hau                       | Comula Cina    | # of Fail at Read Point |         |         |          |

| Stress lest             | Stress Test Part Number             | Sample Size    | 48 cys                  | 168 cys | 500 cys | 1000 cys |

| TC                      | EPC1001                             | 45             | 0                       | 0       | 0       | 0        |

| TC                      | EPC1014                             | 50             | 0                       | 0       | 0       | 0        |

|                         | Deut Nous hau                       |                | # of Fail at Read Point |         |         |          |

| Stress lest             | Stress Test Part Number Sample Size | 24 HR          | 168 HR                  | 500 HR  | 1000 HR |          |

| THB                     | EPC1014                             | 45             | 0                       | 0       | 0       |          |

| Stress Test             | Part Number                         | Sample Size    | # of Fail at Read Point |         |         |          |

|                         |                                     |                | 24 HR                   | 168 HR  | 500 HR  | 1000 HR  |

| ower Supply Life Test   | EPC1001                             | 10             | 0                       | 0       | 0       | 0        |

# Appendix IV: HTRB Maximum Rated Voltage at 125°C

### EPC1001 HTRB 100 V at 125°C

# Appendix IV: HTRB Maximum Rated Voltage at 125°C

### EPC1014 HTRB 40 V at 125°C

## Appendix V: HTGB @ 125°C

### EPC1001 HTGB 5 V at 125°C

# Appendix V: HTGB @ 125°C

### EPC1001 HTGB 5.4 V at 125°C

# Appendix V: HTGB @ 125°C

### EPC1001 HTGB 6 V at 125°C

### **Phase One Testing**

# Appendix VI: Temperature Cycling -40°C to 125°C

### EPC – THE LEADER IN GaN TECHNOLOGY | WWW.EPC-CO.COM | COPYRIGHT 2019

# Appendix VI: Temperature Cycling -40°C to 125°C

### EPC1014 TC -40°C to 125°C

### Appendix VII: THB 85°C, 85% RH

### EPC1014 THB 85°C / 85 RH 40 V

### **Appendix VIII: Operating Life Tests**

### EPC1001 Power Supply Operating Life

$48\,V_{\text{IN}}-1\,V_{\text{OUT}},\,10$  A Load, 250 kHz

Power supply test circuit

## **For More Information:**

Please contact info@epc-co.com or your local sales representative

Visit our website: www.epc-co.com

Sign-up to receive EPC updates at bit.ly/EPCupdates or text "EPC" to 22828

EPC Products are distributed through Digi-Key. <u>www.digikey.com</u>