How2AppNote 018 eGaN®技術

# eGaN<sup>®</sup> FETを使った48 V入力、12 V、9 V、5 V 出力で、300 Wのデジタル制御<sup>1</sup>/<sub>16</sub>ブリック DC-DCコンバータの設計方法

### 概要

ブリックDC-DCコンバータは、データセンター、電気通信、および自動車の用途で広く採用されており、公称48 V 入力を、他にも出力電圧はありますが、公称12 V出力の分配バスに変換します。

形状が決まっているので、トレンドは主に、より高い電力密度へと向かっています。このアプリケーション・ノートでは、48 V 入力、12 V、9 V、5 V 出力の用途にGaN FETを使って、出力電流が最大25 A、出力電力300W、ピーク効率95.8%、最大電力密度730 W /立方インチ(1インチは2.54 cm)のデジタル制御の $^1/_{16}$ ブリック・コンバータの設計について説明します。

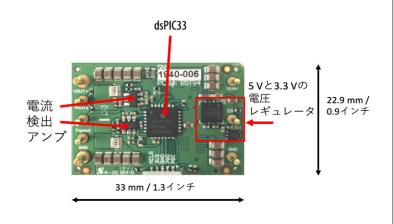

1/16ブリック・コンバータの標準的な寸法は33×22.9 mm (1.3×0.9インチ) です。この設計の高さ制限は10 mm (0.4インチ) に設定しました。

#### 設計の課題

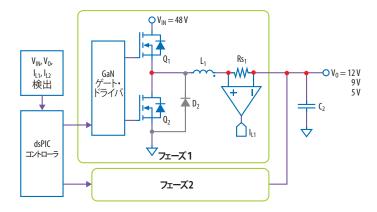

高電力密度の1/16ブリックの主な課題は磁気部品です。スペースと寸法の制約によって、磁気部品はサイズと形状に制限があります。さらに、大出力電流(最大25A)には高い飽和電流定格が必要ですが、通常、飽和電流が大きいコイルは、かさばります。2相同期バック(降圧型)構成にすると、2つのコイルが出力電流を共有するため、ピーク電流への要件を軽減できます。これの簡略化した回路図が図1です。

2番目の課題は、スイッチング・トランジスタの選択です。磁気部品は基板スペースのかなりの部分を占めるため、非常に優れたハード・スイッチングの性能指数FOM (figure-of-merit) [2]と、小さい実装面積が求められます。これらの理由から、この設計ではチップスケール・パッケージに封止したGaN FETを選びました。

次の課題は、GaN対応コントローラが少ないことです。市販のMOSFETコントローラは通常、デッドタイムが長く(20 ns以上)、ゲート・ドライバが遅くて減衰し、スイッチ・ノードでー2~-3 Vの負電圧を処理できません。この結果、効率を犠牲にして適切な動作を保証するために、MOSFETコントローラの回路を適応させなければなりません。この設計では、GaN FETの高性能を十分に活用するために、米マイクロチップ・テクノロジーのマイクロコントローラdsPIC33を使いました。

# パワー段の設計

この設計の基本構成として、同期バック・コンバータを選びました。25 A の最大出力電流を考慮して、単一のコイルを使う場合、その電流定格は、ピーク値から平均値までの電流リップルを30%と仮定して、少なくとも33 A でなければなりません。この条件を満たすコイルは、高さの制限に適合しません。代わりに2相同期バック・コンバータを使う場合、各コイルは直流電流12.5 A だけを導通します。リップルが30%のとき、ピーク電流は16.25 Aになります。

コンバータのサイズと導通損失を削減するために、オン抵抗  $R_{DS(on)}$ が $3.2\,\mathrm{m}\,\Omega$ の $GaN\,FET$ であるEPC2053を使いました。台湾

図1.1/16ブリック・コンバータの簡略化した回路図

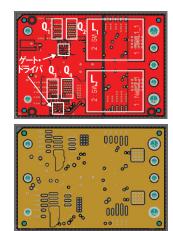

図2. 対称の2相レイアウトを示すプリント回路基板の最初の2層

$\mu$ PI semiconductorのディスクリートGaN対応ゲート・ドライバ  $\mu$ P1966Aも選びました。これによって、逆並列ダイオード(図1の  $D_2$ )が不要になり、損失が減少します。

GaN FETの高速スイッチングを利用するには、電力ループのインダクタンスを最小限に抑える必要があります。最適なレイアウト [1,2] 技術を採用すると、図2に示すように、プリント回路基板の2番目の層がグラウンド面になります。この6層プリント回路基板には、放熱性を高めるために、この他の2層のグラウンド面も含まれています。.

コイルの場合、TDKのB82559シリーズ [3]は、面積 $13\times10.7~\text{mm}$  ( $0.51\times0.42$ インチ)で、高さ5 mmまたは6 mmの優れたオプションです。高い飽和電流定格と低いDCR (直流抵抗) も備えています。 $2.4~\mu$  Hのコイルの飽和電流定格は16.5~Aです。したがって、この設計にはスイッチング周波数に500~kHzを選び、飽和電流の要件を満たす公称動作条件の下でピーク電流16.25~Aが得られました。

How2AppNote 018 eGaN®技術

# デジタル制御

コントローラの互換性の問題に対処するために、マイクロチップ・テクノロジーのデジタル・コントローラ**dsPIC33CK**[4]を使いました。CPUの最大速度が100 MIPSの16ビットのプロセッサです。パルス幅変調(PWM)モジュールは、高分解能モードで構成できるため、デューティ比とデッドタイムで0.25 nsの分解能が得られ、デッドタイムを正確に調整すれば、GaN FETの高性能を十分に活用することができます。

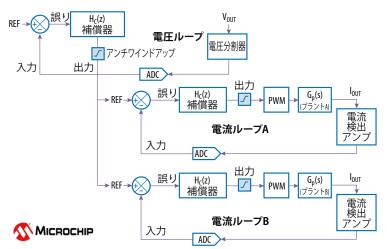

デジタル制御ループには2つのオプションがあります:a) 電流の平衡化ができる単一電圧ループ、または、b) マルチループ・コントローラです。どちらのオプションにも、検出抵抗と差動アンプで構成される電流検出回路が必要です。この設計では、マルチループ・コントローラを選びました。さらに、1 m $\Omega$ の検出抵抗と低雑音アンプMCP6C02を使いました。制御回路ブロック図が図3です。同じ電流の基準 $I_{REF}$ を2つの独立した電流ループに使いました。この結果、両方のコイルの電流は同じ値に安定化されます。2つの内部電流ループの帯域幅は10kHzに設定され、外部電圧ループの帯域幅は2kHzに設定しました。

図3. マルチループの2相コンバータの制御回路ブロック図

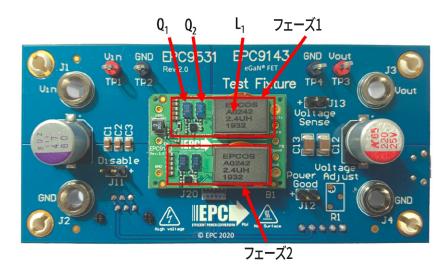

図4. 試験装置EPC9531に実装された1/16ブリック・コンバータEPC9143

# 設計検証のセットアップ

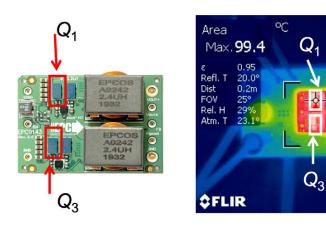

図4は、試験装置EPC9531に実装した1/16ブリック・コンバータ (**EPC9143**) の写真です。図5に示すように、パワー段の部品 (ゲート・ドライバ、GaN FET、コイル) が表面にあり、制御部品 (電流検出アンプ、デジタル・コントローラ) が裏面にあります。

この設計の最も高いスタンドオフは $9.1 \, \text{mm}$ で、内訳はコイルが $6 \, \text{mm}$ 、プリント回路基板の厚さが $1.6 \, \text{mm}$ 、裏面の部品 ( $0805 \, \text{サイズのコンデンサ}$ ) が $1.5 \, \text{mm}$ です。

試験装置EPC9531には、47 μFの入力コンデンサと200 μFの出力コンデンサを追加しました。これらの追加のコンデンサは、コントローラの安定性を維持することに役立ちます。試験装置は、プログラミング・ポートとUSB通信も備えています。

図5.1/16ブリック・コンバータの裏面

How2AppNote 018 eGaN®技術

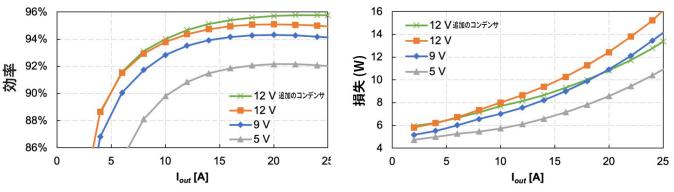

図6.1/16ブリック・コンバータの効率と損失の測定

図7. 熱定常状態で動作する $^{1}$ / $_{16}$ ブリック・コンバータの熱画像。 $V_{IN}$ =48 V,  $V_{OUT}$ =12 V, 出力電流25 A, エアフロー800 LFMのとき

# 設計の結果

エアフロー800 LFMで、最大25 Aまでの出力電流範囲で、出力電圧が 異なる (5 V、9 V、12 V) ときの熱定常状態で測定した効率と損失を図 6に示します。12 V出力で出力電流が20 A~25 Aのときのピーク効率 は95%です。図7の熱画像に示すように、最高デバイス温度は100℃に 達しました。

スペースの制限によって、このブリック・コンバータは入力容量が合計で8.2  $\mu$ Fしか対応できません。2  $\mu$ Fの容量が追加されると、ピーク効率は95.8%に向上し、損失は2.7 W (15%) 減少します。

#### 結論

このアプリケーション・ノートでは、大電力の1/16ブリック・コンバータの設計上の課題を評価し、eGaN FETを使うと、最先端のMOSFETの設計よりも最大負荷電流を増やすことができることを示しました。最大25 A の出力電流能力を備えた48 V 入力、最大出力12 V

で300 W のコンバータを設計しテストしたところ、コンバータのピーク効率は95%が得られました。 容量を2 µF追加することによって、ピーク効率95.8%が得られます。

99.4

22.9

06/02/20

#### 参考文献

[1] A. Lidow, M. De Rooij, J. Strydom, D. Reusch, and J. Glaser, GaN transistors for efficient power conversion, 3rd ed. John Wiley & Sons, 2019. ISBN: 978-1119594147.

[2] D. Reusch and J. Glaser, "DC-DC Converter Handbook - A Supplement to GaN Transistors for Efficient Power Conversion," 1st ed. Power Conversion Publications, 2015, ISBN 978-0-9966492-0-9.

[3] TDK. (2012). SMT power inductors, [Online]. Available: https://www.tdk-electronics.tdk.com/inf/30/db/ind\_2008/b82559\_a013.pdf.

[4] Microchip Technology Inc. (2019). 16-bit PIC Microcontrollers Family, [Online]. Available: https://www.microchip.com/design-centers/16-bit.

# IIEPC EFFICIENT POWER CONVERSION

#### 詳細については、

info@epc-co. comに電子メールで、またはお近く の販売代理店にお尋ねください EPCのウエブサイト: epc-co. com/epc/jp/

eGaNは、Efficient Power Conversion Corporation. Inc.の登録商標です