How2AppNote 020 eGaN®技術

# モノリシックGaNのePower™ Stageを使った48 V入力、12 V出力で双方向の¹/<sub>16</sub>ブリック・コンバータの設計方法

### はじめに

ブリックDC-DCコンバータは、データセンター、電気通信、自動車の各アプリケーションで広く使われており、公称48 Vのバスを公称12 Vのバス(または、12 Vから48 Vへの昇圧)に変換します。GaN集積回路(IC)技術の進歩によって、ハーフブリッジとゲート・ドライバの集積化が可能になり、この結果、レイアウトが簡素化され、面積が最小化され、コストが削減されるワン・チップ・ソリューションが実現できます。

このアプリケーション・ノートでは、最大出力電力300 W、ピーク効率95%で、48 V 入力、12 V 出力のアプリケーション向けの集積化したGaNパワー段を使ったデジタル制御の双方向 $^1/_{16}$ ブリック・コンバータの設計について説明します。

1/16ブリック・コンバータの標準的な面積は、 $33 \times 22.9$  mm  $(1.3 \times 0.9$  インチ)です。この設計の高さ制限は10 mm (0.4 インチ)に設定されています。

# モノリシックGaNのePower™ Stage

GaN FETとゲート駆動のモノリシック集積化によって、性能が向上し、基板レイアウトが簡素化されます。さらに、寄生のインダクタンスと容量、および関連する損失も低減します。

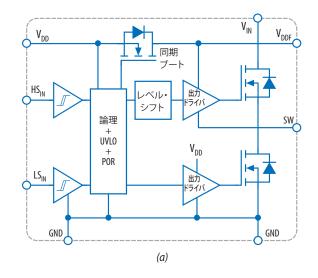

図1 (a) は、GaNのePower<sup>™</sup> StageであるEPC2152の回路ブロックの概略図です [1]。主なパワーFETは、集積されたゲート・ドライバによって制御されます。このICには、3.3 V~5 Vの論理レベルを入力できる入力バッファも含まれています。パワー・オン・リセット(POR)機能や、低電圧ロックアウト(UVLO)機能、高電圧信号のレベル・シフト回路、同期ブートストラップFETなどの標準的な回路も搭載されています [2]。モノリシックGaNパワー段の写真が図1 (b) です。パワーGaN FETは両方とも、定格80 Vで、オン抵抗は10 m $\Omega$ です。

# 双方向DC-DCコンバータの設計

大電力の1/16ブリックを設計する際の重要な課題の1つは、スペースが限られていることです。集積化されたEPC2152の面積は、わずか  $18~\rm mm^2$ で済み、高効率を達成することに貢献する適切なデカップリング・コンデンサのための余地を残せます。

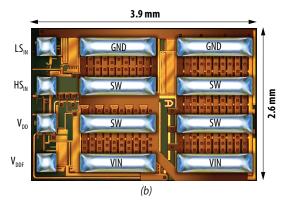

双方向対応の<sup>1</sup>/<sub>16</sub>ブリックDC-DCコンバータEPC9151の概略図を図2に示します。これには、2相同期整流用バックのパワー段、デジタル・コントローラ、電流検出器、およびハウスキーピング電源が搭載されています。ピーク電流要件が軽減され、より小さな磁気部品を使えるように、2相のアプローチを選択しました。

図1. (a) は回路ブロック図、(b) はモノリシック GaNのePower StageであるEPC2152の写真 [1]

図2. 1/16ブリックの双方向DC-DCコンバータの回路図

EPC:電力変換技術のリーダー | EPC-CO.COM/EPC/JP | ©2020

How2AppNote 020 eGaN®技術

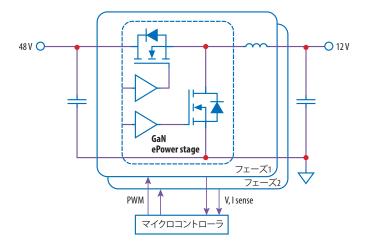

集積されたパワー段を使うと、パワー・ループのインダクタンスを簡単に最小化できます。 高周波デカップリング・コンデンサは、最適なレイアウト [4] 手法を使って、ICの隣に配置され、図3に示すように、プリント回路基板の2番目の層は、グラウンド面です。この6層プリント回路基板には、この他、グラウンド面が2層あり、電圧と電流のフィードバック信号のシールド、および、放熱特性の向上のために使っています。

TDKのB82559シリーズのコイル [5] を使い、面積は $13\times10.7$ mm ( $0.51\times0.42$ インチ)、高さは5 mmまたは6 mmです。2.4  $\mu$ Hのコイルの飽和電流定格は16.5 Aです。したがって、スイッチング周波数を500 kHzにし、飽和電流要件を満たす48 Vから12 Vへ (または、その逆)の変換時にピーク電流16.25 Aが得られます。

# デジタル制御

米マイクロチップ・テクノロジーのデジタル・コントローラdsPIC33CK32MP102 [6] を使います。これは、CPUの最大速度が100 MIPSの16ビット・プロセッサです。パルス幅変調(PWM)モジュールは、高分解能モードで構成できるため、デューティ比とデッドタイムで250 psの分解能が得られ、デッドタイムを正確に調整してGaNFETの高性能を十分に活用できます。

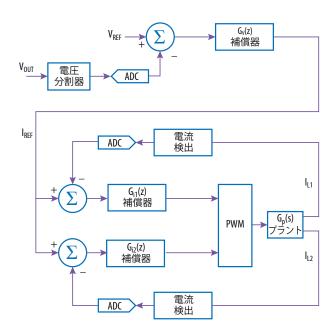

デジタル平均電流モード制御は、降圧モードと昇圧モードの両方に実装されています。電流検出回路は、検出抵抗と差動アンプで構成されています。この設計では、低損失の $1 \, \mathrm{m}\Omega$ の検出抵抗と低雑音アンプMCP6C02を使っています。制御回路のブロック図が図4です。2つの独立した電流ループに同じ電流リファレンス $1_{REF}$ を使います。この結果、両方のコイルの電流が同じ値に安定化されます。2つの内部電流ループの帯域幅は、 $10 \, \mathrm{kHz}$ に設定され、外部電圧ループの帯域幅は $2 \, \mathrm{kHz}$ に設定されています。

#### 実験結果

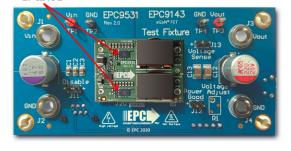

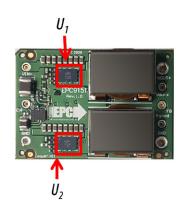

図5は、テスト回路EPC9531に取り付けた $^{1}/_{16}$ ブリック・コンバータ EPC9151の表面とその裏面の写真です。設計のスタンドオフの高さの合計は $^{9.1}$  mmで、コイルが $^{6}$  mm、プリント回路基板が $^{1.6}$  mm、裏面の部品 ( $^{0805}$ サイズのコンデンサ)が $^{1.5}$  mmです。

図5 (上図) のテスト回路EPC9531には、 $47 \mu$ Fの入力容量と200  $\mu$ F の出力容量が追加されています。これらの追加の容量は、コントローラの安定性を維持する助けになります。このテスト回路は、プログラミング・ポートとUSB通信も提供します。

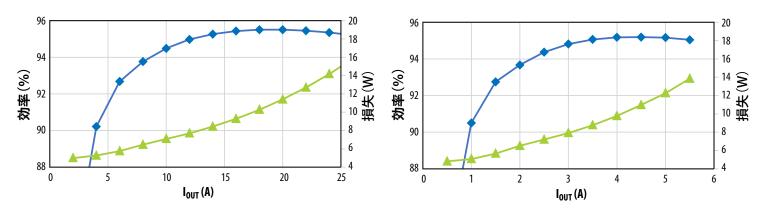

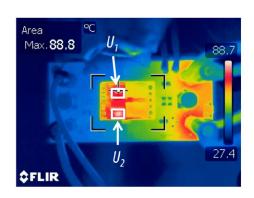

ヒートシンクがなく、1700 LFMのエアフローがある場合、測定された熱定常状態の効率と損失は、降圧モードのときが図6(a)、昇圧モードが図6(b)です。ピーク効率は、降圧モードで95.5%、昇圧モードで95.1%です。図7の熱画像に示すように、デバイスの最大温度は、最大出力電力で89°Cに達しました。400~800 LFMなどの緩やかなエアフローのある環境では、ヒートシンクが必要です。

図3. EPC2152を搭載し、簡素化したレイアウトを示すプリント 回路基板の最初の2層

図4. マルチループ2相コンバータの制御回路ブロック図

#### EPC2152

図5. 1/16ブリック・コンバータEPC9151の表面と裏面

How2AppNote 020 eGaN®技術

図6. 1/16 ブリック・コンバータで測定された効率と損失: (a)  $V_{IN}$  = 48 V、 $V_{OUT}$  = 12 V (降圧); (b)  $V_{IN}$  = 12 V,  $V_{OUT}$  = 48 V (昇圧)

図7. 熱定常状態で動作する $^{1}/_{16}$ ブリック・コンバータの熱画像;  $V_{IN}$ =48 V、 $V_{OUT}$ =12 V、出力電流25 A、エアフロー1700 LFMのとき

## 結論

このアプリケーション・ノートでは、2個のモノリシック集積化した GaNパワー段EPC2152を使った双方向の大電力<sup>1</sup>/16ブリック・コンバータEPC9151を紹介しました。これは、最先端のMOSFET設計と比べて、よりシンプルなレイアウトと、より高い電力密度を実証しています。300 Wで48 V入力、12 V出力(または、その逆)のコンバータ設計では、ピーク効率95%が得られました。

# 参考文献

[1] "EPC2152 – 80 V, 10 A Integrated ePower™ Stage," Efficient Power Conversion Preliminary Datasheet, Jan. 2020.

[2] M.A. de Rooij, J.T. Strydom, D.C. Reusch, "High Voltage Zero QRR bootstrap Supply," United States Patent US9,667,245 B2, May 30, 2017.

[3] Y. Zhang and M. de Rooij, "300 W 48V-12V Digitally Controlled 1/16<sup>th</sup> Brick DC-DC Converter Using GaN FETs," PCIM - Europe, July 2020.

[4] A. Lidow, M. De Rooij, J. Strydom, D. Reusch, and J. Glaser, GaN transistors for efficient power conversion, 3rd ed. John Wiley & Sons, 2019. ISBN: 978-1119594147.

[5] TDK. (2012). SMT power inductors, [Online]. Available: https://www.tdk-electronics.tdk.com/inf/30/db/ind 2008/b82559\_a013.pdf.

[6] Microchip Technology Inc. (2019). 16-bit PIC Microcontrollers Family, [Online]. Available: https://www.microchip.com/design-centers/16-bit.

# IIEPCI EFFICIENT POWER CONVERSION

#### 詳細については、

info@epc-co.comに電子メールで、またはお近く の販売代理店にお尋ねください EPCのウエブサイト:epc-co.com/epc/jp/ bit.ly/EPCupdates に登録、または22828に「EPC」とテ

キスティングすれば、EPCの最新情報を受信できます

eGaNは、Efficient Power Conversion Corporation, Inc. の登録商標です