## EPC23101

Halogen-Free

# EPC23101 – ePower™ Chipset

V<sub>IN</sub> , 100 V I<sub>Load</sub> , 65 A

EPC's ePower<sup>TM</sup> Stage and Chipset integrate input logic interface, level shifting, bootstrap charging and gate drive buffer circuits along with eGaN output FETs. Integration is implemented using EPC's proprietary GaN IC technology. The end result is a Power Stage that translates logic level input to high voltage and high current power output that is smaller in size, easier to manufacture, simpler to design and more efficient to operate.

| Key Parameters                   |        |      |  |  |  |

|----------------------------------|--------|------|--|--|--|

| PARAMETER                        | VALUE  | UNIT |  |  |  |

| Power Stage Load Current (1 MHz) | 65 [1] | А    |  |  |  |

| Operating PWM Frequency Range    | 3 [2]  | MHz  |  |  |  |

| Absolute Maximum Input Voltage   | 100    |      |  |  |  |

| Operating Input Voltage Range    | 80     | V    |  |  |  |

| Nominal Bias Supply Voltage      | 5      |      |  |  |  |

Output Current and PWM Frequency Ratings are functions of Operating Conditions. Appropriate derating should be applied to keep  $T_J$  at less than 125 °C. See Notes 1 & 2.

| Chipset Information |                                   |                       |  |  |  |

|---------------------|-----------------------------------|-----------------------|--|--|--|

| PART NUMBER         | Rated R <sub>DS(on)</sub> at 25°C | QFN Package Size (mm) |  |  |  |

| EPC23101            | 3.3 mΩ                            | 3.5 x 5               |  |  |  |

| EPC2302             | 1.8 mΩ                            | 3 x 5                 |  |  |  |

All exposed pads feature wettable flanks that allow side wall solder inspection. High voltage and low voltage pads are separated by 0.6 mm spacing to meet IPC rules. Recommended to use EPC2302 as companion low side FET for the chipset.

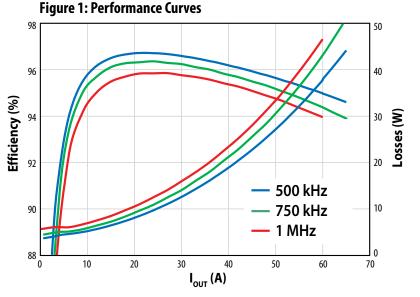

Buck Converter,  $V_{IN} = 48$  V,  $V_{OUT} = 12$  V, Deadtime = 10 ns, L = 2.2 µH, DCR = 700 µΩ, EPC23101 + EPC2302, Airflow = 1000 LFM. See See **EPC90142 Quick Start Guide** for details.

EPC23101 ePower<sup>™</sup> Chipset

RoHS 🕅

#### Applications

- Buck, Boost, Half-Bridge, Full Bridge or LLC Converters

- Motor Drive Inverter

#### Features

- Integrated high side eGaN® FET with internal gate driver and level shifter

- 5 V external bias supply

- 3.3 V or 5 V CMOS input logic levels

- Independent high side and low side control inputs

- Cross conduction lockout logic keeps both FETs off when logic inputs are both high at same time

- External resistors to tune SW switching times and over-voltage spikes above rail and below ground

- Robust level shifter operating for hard and soft switching conditions

- False trigger immunity from fast switching transients

- Synchronous charging for high side bootstrap supply

- + Low quiescent current mode from external  $V_{\text{DRV}}$  supply when  $V_{\text{DD}}$  Disable Input pin is pulled up

- Undervoltage lockout for internal low side and high side bias supplies

- Active gate pull-down for HS FET and LS gate drive with loss of  $V_{\text{DRV}}$  supply

- Chipset of compatible high and low side devices in QFN packages with optimized pinouts between the two devices

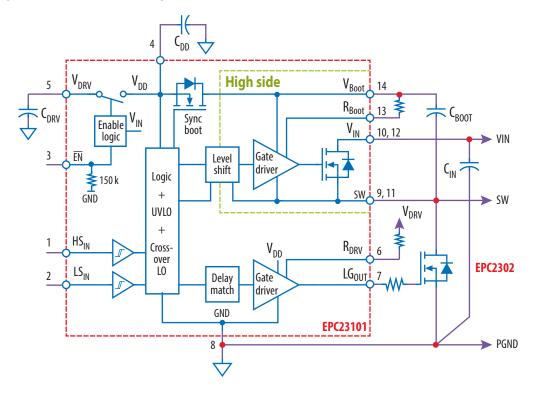

#### **Figure 2: Functional Block Diagram**

#### **General Description**

The EPC23101 ePower<sup>™</sup> IC integrates a half-bridge gate driver with an internal high side FET. It is designed as part of a chipset with a companion low side eGaN<sup>®</sup> FET such as the EPC2302. Integration is implemented using EPC's proprietary GaN IC technology. The high side monolithic chip integrates input logic interface, level shifting, bootstrap charging and gate drive buffer circuits along with a high side eGaN output FET. The low side output FET is driven by the gate driver output of the GaN IC to configure a half-bridge power stage.

The on-chip gate drive buffers practically eliminate effects of common source inductance and gate drive loop inductance. Power loop inductance is minimized by compatible high side to low side pinout configuration that facilitates optimal layout technique. Switching times are tuned by external resistors to achieve 1–3 ns rise and fall times from 0–48 V at full load current. Over-voltage spikes can be controlled to less than +10 V above rail and –10 V below ground during hard switching transitions by choosing the tuning resistors,  $R_{BOOT}$  and  $R_{DRV}$ .

The EPC23101 IC only requires an external  $5 V V_{DRV}$  power supply. Internal low side and high side power supplies,  $V_{DD}$  and  $V_{BOOT}$ , are generated from the external supply via a series connected switch. The internal supplies can be cut off to save quiescent power by turning off the switch with 5 V applied to the  $\overline{EN}$  pin.

The charging path for the floating bootstrap supply is activated with  $L_{SIN}$  logic. It uses eGaN FET as the series switch that minimizes power losses by eliminating reverse recovery. This synchronous bootstrap charging circuit also minimizes voltage drop in the charging path.

Robust level shifters from low side to high side channels are designed to operate correctly even at large negative clamped voltage and to avoid false trigger from fast dv/dt transients including those driven by external sources or other phases.

Protection is provided by high side and low side under-voltage lockout to keep both FETs off at low supply voltages. If the supply voltages drop even lower or are lost while  $V_{\rm IN}$  is active at greater than 10 V, another active pull-down circuit is used with biasing from  $V_{\rm IN}$  to prevent destructive turn-on of both FETs from gate to drain leakage.

The EPC23101 IC is capable of interfacing to digital controllers that use standard 3.3 V or 5 V CMOS logic levels. Separate and independent high side and low side logic control inputs allow external controllers to set fixed or adaptive dead times for optimal operating efficiency. Cross conduction prevention logic keeps both FETs off when logic inputs are both high at the same time.

The FET gate drive voltages are derived from the internal low side and high side power supplies. Full gate drive voltages are only available after the  $HS_{IN}$  and  $LS_{IN}$  PWM inputs start to operate for a few cycles.

# Figure 3: EPC23101 Transparent Top View

| Pin       | Pin Name          | Pin Type | Description                                                                                                                                                                                                                                                                        |

|-----------|-------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | HS <sub>IN</sub>  | I        | High side PWM logic input, level referenced to GND. Internal pull-down resistor is connected between ${\rm HS}_{\rm IN}$ and GND.                                                                                                                                                  |

| 2         | LS <sub>IN</sub>  | I        | Low side PWM logic input, level referenced to GND. Internal pull-down resistor is connected between $\rm LS_{\rm IN}$ and GND.                                                                                                                                                     |

| 3         | ĒN                | I        | $V_{DD}$ disable input, level referenced to GND. Internal VDD will be disabled when $\overline{EN}$ is connected to $V_{DRV}$ . $V_{DD}$ will follow $V_{DRV}$ when $\overline{EN}$ is connected to GND. Internal pull-down resistor is connected between $\overline{EN}$ and GND. |

| 4         | V <sub>DD</sub>   | S        | Internal power supply referenced to GND, connect a bypass capacitor from $\rm V_{\rm DD}$ to GND.                                                                                                                                                                                  |

| 5         | V <sub>DRV</sub>  | S        | External 5 V nominal power supply referenced to GND, connect a bypass capacitor from $V_{\text{DRV}}$ to GND.                                                                                                                                                                      |

| 6         | R <sub>drv</sub>  | 0        | Insert resistor between $R_{\text{DRV}}$ to $V_{\text{DRV}}$ to control the turn-on slew rate of the driven low side FET.                                                                                                                                                          |

| 7         | LG <sub>out</sub> | 0        | Low side gate drive output to driven low side FET. Maintain short loop between $LG_{OUT}$ and kelvin source connection of low side FET to minimize common mode inductance.                                                                                                         |

| 8         | GND               | S, 0     | Logic ground. Connect bypass capacitors between operating bias supplies, $V_{\text{DRV}}$ and $V_{\text{DD}}$ to GND. Low side output gate driver is also referenced to same GND pin.                                                                                              |

| 9,<br>11  | SW                | P, S     | Output switching node. Connected to output of half-bridge power stage. The floating bootstrap power supply, $V_{BOOT}$ , is also referenced to SW.                                                                                                                                 |

| 10,<br>12 | V <sub>IN</sub>   | Р        | Power bus input. Connected to drain terminal of internal high side FET. Connect power loop capacitors from $\rm V_{\rm IN}$ to PGND or power source terminals of low side FET.                                                                                                     |

| 13        | R <sub>BOOT</sub> | 0        | Insert resistor between $\rm R_{B00T}$ to $\rm V_{B00T}$ to control the turn-on slew rate of the internal high side FET.                                                                                                                                                           |

| 14        | V <sub>BOOT</sub> | S        | Floating bootstrap power supply referenced to SW, connect an external bypass capacitor from $\rm V_{BOOT}$ to SW.                                                                                                                                                                  |

Pin Type: P = Power, S = Bias Supplies, I = Logic Inputs, O = Gate Drive Output

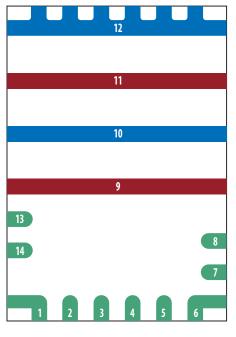

## Figure 4: EPC2302 Transparent Top View

| Pin | Description |  |  |  |

|-----|-------------|--|--|--|

| 1   | Gate        |  |  |  |

| 2   | Source      |  |  |  |

| 3   | Drain       |  |  |  |

| 4   | Source      |  |  |  |

| 5   | Drain       |  |  |  |

| 6   | Source      |  |  |  |

| 7   | Drain       |  |  |  |

#### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur and device reliability may be affected. All voltage parameters are absolute voltages referenced to GND unless indicated otherwise.

|                                     | Absolute Maximum Ratings                                    |     |     |       |  |  |

|-------------------------------------|-------------------------------------------------------------|-----|-----|-------|--|--|

| SYMBOL                              | PARAMETER                                                   | MIN | MAX | UNITS |  |  |

| V <sub>IN</sub>                     | Input Voltage (V <sub>IN</sub> to GND)                      |     | 100 |       |  |  |

| V <sub>SW(continuous)</sub>         | Output Switching Node (SW to GND), Continuous               |     | 100 | ]     |  |  |

| V <sub>DRV</sub>                    | External Bias Supply (V <sub>DRV</sub> to GND)              |     | 6   |       |  |  |

| V <sub>DD</sub>                     | Internal Low Side Supply Voltage (V <sub>DD</sub> to GND)   |     | 6   | v     |  |  |

| V <sub>BOOT</sub> – V <sub>SW</sub> | Internal High Side Supply Voltage (V <sub>BOOT</sub> to SW) |     | 6   |       |  |  |

| LG <sub>OUT</sub>                   | Low Side Gate Drive Output (LG <sub>OUT</sub> to GND)       |     | 6   |       |  |  |

| HS <sub>IN</sub> , LS <sub>IN</sub> | PWM Logic Inputs                                            |     | 5.5 | ]     |  |  |

| ĒN                                  | V <sub>DD</sub> Disable Input                               |     | 5.5 |       |  |  |

| رT                                  | Junction Temperature                                        |     | 150 | •C    |  |  |

| T <sub>STG</sub>                    | Storage Temperature                                         | -55 | 150 |       |  |  |

#### **ESD Ratings**

| ESD Ratings |                                          |         |     |       |  |

|-------------|------------------------------------------|---------|-----|-------|--|

| SYMBOL      | PARAMETER                                | MIN     | MAX | UNITS |  |

| НВМ         | Human-body model (JEDEC JS-001)          | +/-1000 |     | V     |  |

| CDM         | Charged-device model (JEDEC JESD22-C101) | +/-500  |     |       |  |

#### **Thermal Characteristics**

$R_{\theta JA\_JEDEC}$  is measured using JESD51-2 standard setup with 1 cubic foot enclosure with no forced air cooling, heat dissipated only through natural convection. The test used JEDEC Standard 4-layers PCB with 2oz top and bottom surface layers and 1oz buried layers.  $R_{\theta JA\_EVB}$  is measured using EPC90142 EVB with no forced air cooling, this rating is more indicative of actual application environment.

| Thermal Characteristics |                                                                                             |     |       |  |  |

|-------------------------|---------------------------------------------------------------------------------------------|-----|-------|--|--|

| SYMBOL                  | PARAMETER                                                                                   | TYP | UNITS |  |  |

| R <sub>0JC_Top</sub>    | Thermal Resistance, Junction-to-Case (Top surface of exposed die substrate)                 | 0.4 |       |  |  |

| R <sub>0JB_Bottom</sub> | Thermal Resistance, Junction-to-Board (At solder joints of V <sub>IN</sub> and SW PCB pads) | 3   | °c/w  |  |  |

| R <sub>0JA_JEDEC</sub>  | Thermal Resistance, Junction-to-Ambient (using JEDEC 51-2 PCB)                              | 43  | _ C/W |  |  |

| R <sub>0JA_EVB</sub>    | Thermal Resistance, Junction-to-Ambient (using EPC90142 EVB)                                | 25  |       |  |  |

#### **Recommended Operating Conditions**

For proper operation the device should be used within the recommended conditions. All voltage parameters are absolute voltages referenced to GND unless indicated otherwise.

| Recommended Operating Conditions    |                                                             |        |     |                       |       |  |

|-------------------------------------|-------------------------------------------------------------|--------|-----|-----------------------|-------|--|

| SYMBOL                              | PARAMETER                                                   | MIN    | ТҮР | MAX                   | UNITS |  |

| V <sub>IN</sub>                     | Input Voltage (V <sub>IN</sub> to GND)                      | 10 [3] |     | 80                    |       |  |

| V <sub>SW(Q3 Mode)</sub>            | Output Switch Node, 3rd Quadrant Mode <sup>[4]</sup>        | -2.5   |     | V <sub>IN</sub> + 2.5 |       |  |

| V <sub>SW(pulse2ns)</sub>           | Output Switch Node, Transient PW<2 ns [5]                   | -10    |     | V <sub>IN</sub> +10   |       |  |

| V <sub>DRV</sub>                    | External Bias Supply (V <sub>DRV</sub> to GND)              | 4.75   | 5   | 5.5                   |       |  |

| V <sub>DD</sub>                     | Internal Low Side Supply Voltage (V <sub>DD</sub> to GND)   | 4.75   | 5   | 5.5                   | V     |  |

| V <sub>BOOT</sub> – V <sub>SW</sub> | Internal High Side Supply Voltage (V <sub>BOOT</sub> to SW) | 4.75   | 5   | 5.5                   |       |  |

| LG <sub>OUT</sub>                   | Low Side Gate Drive Output (LG <sub>OUT</sub> to GND)       | 4.75   | 5   | 5.5                   |       |  |

| HS <sub>IN</sub> , LS <sub>IN</sub> | PWM Logic Inputs <sup>[6]</sup>                             | 0      |     | 5                     |       |  |

| EN                                  | V <sub>DD</sub> Disable Input <sup>[3]</sup>                | 0      |     | 5                     |       |  |

| Tj                                  | Operating Junction Temperature                              | -40    |     | 125                   | °C    |  |

| PW_min                              | Minimum input On or Off Pulse Duration, 50% to 50% width    | 20     |     |                       | ns    |  |

| PW_max                              | Maximum input On or Off Pulse Duration, 50% to 50% width    |        |     | 200                   | μs    |  |

## **Electrical Characteristics**

Nominal  $V_{IN} = 48 \text{ V}$ ,  $V_{DRV} = V_{DD} = 5 \text{ V}$  and  $(V_{BOOT} - VSW) = 5 \text{ V}$ . CL = 4000 pF. All typical ratings are specified at  $T_A = 25^{\circ}$ C unless otherwise indicated. All voltage parameters are absolute voltages referenced to GND unless indicated otherwise.

|                            |                                                            | Electrical Characteristics                                                                        |     | I         |          |          |

|----------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|-----------|----------|----------|

| SYMBOL                     | PARAMETER                                                  | TEST CONDITIONS                                                                                   | MIN | TYP       | MAX      | UNITS    |

| Low Side Pow               | ver Supply                                                 |                                                                                                   |     |           |          |          |

| IDRV <sub>Q</sub>          | Off State Total Quiescent Current                          | $HS_{IN}/LS_{IN}/EN = 0 V, V_{DRV} = V_{DD} = 5 V$                                                |     | 10        |          |          |

| IDRV <sub>100kHz</sub>     | Total Operating Current @100 kHz                           | PWM = 100 kHz, 50% On-Time                                                                        |     | 18        |          | mA       |

| IDRV <sub>1MHz</sub>       | Total Operating Current @1 MHz                             | PWM = 1 MHz, 50% On-Time                                                                          |     | 37        |          |          |

| IIN <sub>disable</sub>     | V <sub>IN</sub> Quiescent Current at Disable Mode          | $\overline{\text{EN}} = \text{V}_{\text{DRV}} = 5 \text{ V}, \text{V}_{\text{IN}} = 48 \text{ V}$ |     |           | 600      |          |

| IDRV <sub>disable</sub>    | V <sub>DRV</sub> Quiescent Current at Disable Mode         | $\overline{\text{EN}} = \text{V}_{\text{DRV}} = 5 \text{ V}, \text{V}_{\text{IN}} = 48 \text{ V}$ |     |           | 50       | - μΑ     |

| Bootstrap Po               | wer Supply                                                 |                                                                                                   |     |           |          |          |

| IBOOT <sub>Q</sub>         | Off State Bootstrap Supply Current                         | $HS_{IN} = 0 V, (V_{BOOT} - V_{SW}) = 5 V$                                                        |     | 6         |          |          |

| IBOOT <sub>100kHz</sub>    | Bootstrap Supply Current @100 kHz                          | HS PWM = 100 kHz, 50% On-Time                                                                     |     | 8         |          | mA       |

| IBOOT <sub>1MHz</sub>      | Bootstrap Supply Current @1 MHz                            | HS PWM = 1 MHz, 50% On-Time                                                                       |     | 20        |          | 1        |

| V <sub>SYNC_BOOT</sub>     | Sync Boot Generated (V <sub>BOOT</sub> -V <sub>SW</sub> )  | ISYNC_BOOT = 20 mA                                                                                |     | 4.75      |          | V        |

| Undervoltage               | e Lockout                                                  |                                                                                                   |     |           |          |          |

| VDD <sub>UVLO+</sub>       | UVLO Trip Level V <sub>DD</sub> Rising                     | LS <sub>IN</sub> = 5 V, V <sub>DD</sub> Ramps Up                                                  |     | 4.0       |          |          |

| VDD <sub>HYST</sub>        | UVLO V <sub>DD</sub> Falling Hysteresis                    | LS <sub>IN</sub> = 5 V, V <sub>DD</sub> Ramps Down                                                |     | 0.5       |          | 1        |

| VBOOT <sub>UVLO+</sub>     | UVLO Trip Level (V <sub>BOOT</sub> - VSW) Rising           | HS <sub>IN</sub> = 5 V, V <sub>BOOT</sub> Ramps Up                                                |     | 4.0       |          | - V      |

| VBOOT <sub>HYST</sub>      | UVLO (V <sub>BOOT</sub> - VSW) Falling Hysteresis          | HS <sub>IN</sub> = 5 V, V <sub>BOOT</sub> Ramps Down                                              |     | 0.5       |          | 1        |

| Logic Input Pi             |                                                            |                                                                                                   |     | 1         | 1        | 1        |

| V <sub>IH</sub>            | High-level Logic Threshold                                 | HS <sub>IN</sub> , LSIN Rising                                                                    | 2.4 |           |          |          |

| V <sub>IL</sub>            | Low-level Logic Threshold                                  | HS <sub>IN</sub> , LSIN Falling                                                                   |     |           | 0.8      | v        |

| V <sub>IHYST</sub>         | Logic Threshold Hysteresis                                 | V <sub>IH</sub> Rising – V <sub>IL</sub> Falling                                                  |     | 0.3       |          | 1        |

| R <sub>IN</sub>            | HS <sub>IN</sub> and LS <sub>IN</sub> Pull-Down Resistance | HS <sub>IN</sub> , LS <sub>IN</sub> = 5 V                                                         |     | 6.5       |          | kΩ       |

| V <sub>DD</sub> Disable In |                                                            | 1187 118                                                                                          |     |           | <u> </u> | 1        |

| V <sub>TH_EN</sub>         | EN Input Threshold                                         | V <sub>DRV</sub> = 5 V                                                                            | 3.3 |           |          | v        |

| R <sub>EN</sub>            | EN Pull-Down Resistance                                    | $\overline{EN} = 5 V$                                                                             |     | 150       |          | kΩ       |

|                            | e Drive Output                                             |                                                                                                   |     |           |          |          |

| R <sub>DS(on)_PU</sub>     | Gate Output Pull-Up FET R <sub>DS(on)</sub>                | R <sub>DRV</sub> = V <sub>DRV</sub>                                                               |     | 0.4       |          |          |

|                            | Gate Output Pull-Down FET R <sub>DS(on)</sub>              |                                                                                                   |     | 0.4       |          | Ω        |

| R <sub>DS(on)_PD</sub>     | Short Circuit Pull-Up Current                              | $R_{DRV} = V_{DRV}, LG_{OUT} = 0 V$                                                               |     | 5         |          |          |

| I <sub>PD</sub>            | Short Circuit Pull-Down Current                            | $LG_{OUT} = V_{DRV}$                                                                              |     | 5         |          | A        |

|                            | ernal Power FET                                            | LSOUT - VDRV                                                                                      |     |           |          | <u> </u> |

|                            | High Side FET R <sub>DS(on)</sub>                          | I <sub>DS</sub> = +/-10 A, HS <sub>IN</sub> = 5 V, LS <sub>IN</sub> = 0 V                         |     | 2.6       | 3.3      | mΩ       |

| R <sub>DS(on)_HS</sub>     | High Side 3rd Quadrant Clamp                               | $I_{DS} = -10 \text{ A}, \text{HS}_{IN} \otimes \text{LS}_{IN} = 0 \text{ V}$                     |     | -1.5      | 5.5      | V        |

| V <sub>HS_DS_Clamp</sub>   | Leakage Current (V <sub>IN</sub> to SW)                    | $H_{S_{IN}} = 0 V, V_{IN} = 100 V, SW = 0 V$                                                      |     | -1.5      | 100      | μΑ       |

| LEAK_VIN-SW                | Output Capacitance (SW to GND)                             | $HS_{IN} = 0 V, V_{IN} = 48 V, SW = 48 V$                                                         |     | 82        | 100      |          |

| C <sub>SW</sub>            |                                                            |                                                                                                   |     |           |          | - pF     |

| C <sub>OSS_HSFET</sub>     | Output Capacitance (V <sub>IN</sub> to SW)                 | $HS_{IN} = 0 V, V_{IN} = 48 V, SW = 0 V$                                                          |     | 630<br>50 |          | nC       |

|                            | Output Charge (V <sub>IN</sub> to SW)                      | $HS_{IN} = 0 V, V_{IN} = 48 V, SW = 0 V$                                                          |     |           |          |          |

| E <sub>QOSS</sub>          | Output Capacitance Stored Energy                           | $HS_{IN} = 0 V, V_{IN} = 48 V, SW = 0 V$                                                          |     | 0.9       |          | -        |

| E <sub>ON_HS_0</sub>       | Turn-On Switching Energy (HS_FET)                          | HS Turn-On, SW = 0 V to 48 V, $R_{BOOT} = 0 \Omega$ , $I_{LOAD} = 10 A$                           |     | 5         |          | - μJ     |

| E <sub>ON_HS_1</sub>       |                                                            | HS Turn-On, SW = 0 V to 48 V, $R_{BOOT} = 2.2 \Omega$ , $I_{LOAD} = 10 A$                         |     | 9         |          | -        |

| E <sub>OFF_HS</sub>        | Turn-Off Switching Energy (HS_FET)                         | HS Turn-Off, SW = 48 V to 0 V, $I_{LOAD}$ = 10 A                                                  |     | 0.3       |          | <u> </u> |

| lectrical Characteristics (continued)  |                                                      |                                                                                 |          |     |     |       |  |

|----------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------|----------|-----|-----|-------|--|

| Electrical Characteristics (continued) |                                                      |                                                                                 |          |     |     |       |  |

| SYMBOL                                 | PARAMETER                                            | TEST CONDITIONS                                                                 | MIN      | TYP | MAX | UNITS |  |

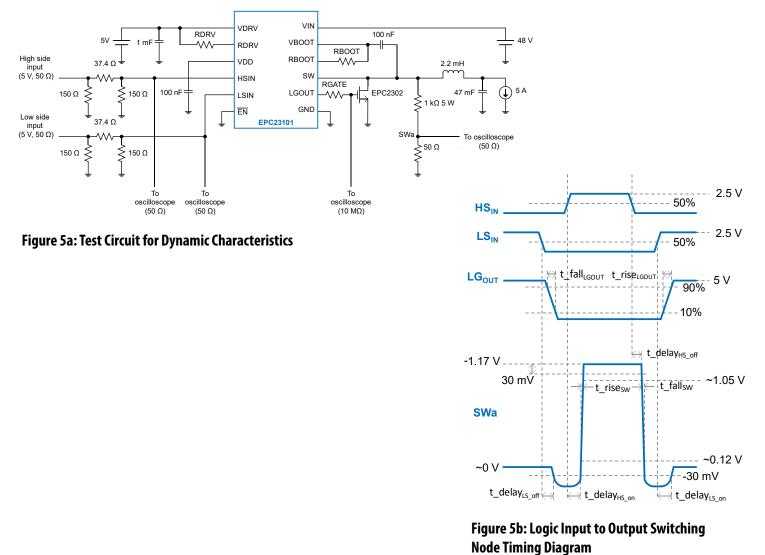

| Dynamic Chara                          | cteristics (Logic Input to Output Switching I        | Node) See Figure 6. Timing Diagram and Test Circuit EPC23101 +                  | EPC2302) |     |     |       |  |

| t_delay <sub>HS_on</sub>               | High-Side On Propagation Delay                       | SW = 0 V and HS FET Turn-On                                                     |          | 20  |     |       |  |

| t_delay <sub>LS_on</sub>               | Low-Side On Propagation Delay                        | SW = 48 V and LS FET Turn-On                                                    |          | 20  |     |       |  |

| t_delay <sub>HS_off</sub>              | High-Side Off Propagation Delay                      | SW = 48 V and HS FET Turn-Off                                                   |          | 20  |     |       |  |

| t_delay <sub>LS_off</sub>              | Low-Side Off Propagation Delay                       | SW = 0 V and LS FET Turn-Off                                                    |          | 20  |     |       |  |

| t_match <sub>on</sub>                  | Delay Matching LS <sub>off</sub> to HS <sub>on</sub> | LS Turn-Off to HS Turn-On                                                       |          | 0   |     |       |  |

| t_match <sub>off</sub>                 | Delay Matching HS <sub>off</sub> to LS <sub>on</sub> | HS Turn-Off to LS Turn-On                                                       |          | 0   |     |       |  |

| t_rise <sub>SW_HS0</sub>               | SW Rise Time at High Side FET Turn-On                | HS Turn-On Buck Mode, 0 V to 48 V, $R_{BOOT} = 0 \Omega$ , $I_{Load} = 5 A$     |          | 1.5 |     | ns    |  |

| t_rise <sub>SW_HS1</sub>               | (Buck Mode, Hard Switching)                          | HS Turn-On Buck Mode, 0 V to 48 V, $R_{BOOT} = 2.2 \Omega$ , $I_{Load} = 5 A$   |          | 3   |     |       |  |

| $t_{SW_{LS0}}$                         | SW Fall Time at Low Side FET Turn-On                 | LS Turn-On Boost Mode, 48 V to 0 V, $R_{DRV} = 0 \Omega$ , $I_{Load} = 5 A$     |          | 1.5 |     |       |  |

| $t_{fall_{SW_{LS1}}}$                  | (Boost Mode, Hard Switching)                         | LS Turn-On Boost Mode, 48 V to 0 V, $R_{DRV}$ = 2.2 $\Omega$ , $I_{Load}$ = 5 A |          | 3   |     |       |  |

| t_rise <sub>LGOUT_0</sub>              | Low Side Gate Drive Rise Time                        | $LG_{OUT}$ Turn-On, $R_{DRV} = 0 \Omega$ , $CL = 4000 pF$                       |          | 4.5 |     |       |  |

| t_rise <sub>LGOUT_1</sub>              |                                                      | $LG_{OUT}$ Turn-On, $R_{DRV}$ = 2.2 $\Omega$ , CL = 4000 pF                     |          | 9   |     |       |  |

| $t_{GOUT_0}$                           | Low Side Gate Drive Fall Time                        | $LG_{OUT}$ Turn-Off, $R_{GATE} = 0 \Omega$ , $CL = 4000 pF$                     |          | 3   |     |       |  |

# **Dynamic Characteristics Parameter Definition**

| Truth Table                                                                 |                                                                      |                  |                  |        |        |  |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------|------------------|------------------|--------|--------|--|

| V <sub>DD</sub>                                                             | V <sub>BOOT</sub> –V <sub>SW</sub>                                   | HS <sub>IN</sub> | LS <sub>IN</sub> | HS FET | LS FET |  |

| <uvlo< td=""><td>-</td><td>-</td><td>-</td><td>OFF</td><td>OFF</td></uvlo<> | -                                                                    | -                | -                | OFF    | OFF    |  |

| >UVLO                                                                       | <uvlo< td=""><td>-</td><td>0</td><td>OFF</td><td>OFF</td></uvlo<>    | -                | 0                | OFF    | OFF    |  |

| >UVLO                                                                       | <uvlo< td=""><td>-</td><td>1</td><td>OFF</td><td>ON [7]</td></uvlo<> | -                | 1                | OFF    | ON [7] |  |

|                                                                             |                                                                      | 0                | 0                | OFF    | OFF    |  |

|                                                                             |                                                                      | 0                | 1                | OFF    | ON     |  |

| >0                                                                          | VLO                                                                  | 1                | 1 0 ON OFF       |        | OFF    |  |

|                                                                             |                                                                      | 1                | 1                | OF     | F [8]  |  |

#### **NOTES:**

- Note 1: Power Stage load current rating is measured using a buck converter application circuit with V<sub>IN</sub> = 48 V, V<sub>OUT</sub> = 13.8 V, PWM frequency = 500 kHz, PCB mounted using EPC90142 Evaluation Board, EPC23101 as high side FET and EPC2302 as low side FET, top side heat sink for both devices, 800 LFM airflow, operating at ambient temperature of 25°C with T<sub>J</sub> not to exceed 125°C. The rated Power Stage load current specification depends on the application circuit topology, driven low side FET characteristics, duty cycle, power dissipation, maximum allowed junction temperature and thermal management techniques and mechanical stress limit imposed by electromigration.

- Note 2: Operating PWM switching frequency range is a function of the characteristics of the driven low side FET, power dissipation, maximum allowed junction temperature and minimum duty cycle. The EPC23101 device is capable of operating above 3 MHz PWM switching frequency given appropriate cooling but users need to derate the maximum output current depending on thermal management technique not to exceed  $T_1 = 125^{\circ}C$ .

- Note 3: The minimum input voltage ( $V_{IN}$ ) should be >= 10 V for the IC to be enabled. Below the minimum  $V_{IN}$  the pass-transistor between  $V_{DRV}$  and  $V_{DD}$  will be off. Same condition when  $V_{DD}$  disable pin,  $\overline{EN}$ , is connected to 5 V.

- Note 4: The output switching node (SW) is clamped above V<sub>IN</sub> by the HS FET or below GND by the LS FET at their respective source drain voltage in the 3rd quadrant. This is an operating condition when both HS and LS FETs are in the off states during the dead time period which is set by the application circuit with typical value of 15 ns. The Absolute Minimum Rating is determined by LS FET 3rd quadrant clamp voltage below GND. Conversely the Absolute Maximum Rating is determined by HS FET 3rd quadrant clamp voltage above V<sub>IN</sub>. The time duration that the device can stay in the negative clamp voltage region is subjected to the amount of load current, power dissipation and maximum allowed junction temperature.

- Note 5: During HS FET or LS FET turn-on transitions with hard switching conditions, the fast di/dt of the HS FET or LS FET coupled with the power loop inductance (V<sub>Peak</sub> = L<sub>Power loop</sub> · di/dt) would cause a transient over-voltage spike above V<sub>IN</sub> or below GND. The Absolute Minimum Rating is amount of peak voltage spike, caused by LS FET di/dt, below GND for less than 2 ns pulse duration. Conversely the Absolute Maximum Rating is amount of peak voltage spike, caused by HS FET di/dt, above VIN, for less than 2 ns pulse duration.

- Note 6: For interfacing with analog controller operating from 12 V<sub>CC</sub> and outputting a 12 V drive signal, a resistor network in series should be inserted to divide the voltage to acceptable V<sub>IH</sub> level and limit the input current into the logic input pins H<sub>IN</sub> and L<sub>IN</sub> which is clamped to the V<sub>DD</sub> supply by ESD protection network.

- Note 7: L<sub>IN</sub> commands LS FET to turn-on to charge bootstrap supply through sync boot.

- Note 8: Internal logic follows HS<sub>IN</sub>, LS<sub>IN</sub> respectively but cross conduction lockout logic prevents both HS and LS FETs to turn on together as commanded if both HS<sub>IN</sub> and LS<sub>IN</sub> are set to logic "high".

## EPC23101

## EPC23101

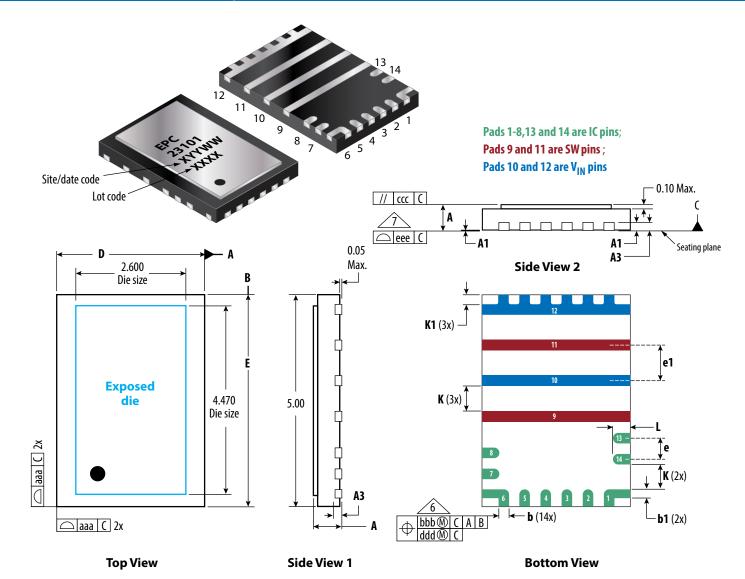

| SYMBOL |      | Dimension | (mm) |      |

|--------|------|-----------|------|------|

| STMBUL | MIN  | Nominal   | MAX  | Note |

| Α      | 0.60 | 0.65      | 0.70 |      |

| A1     | 0.00 | 0.02      | 0.05 |      |

| A3     |      | 0.20 Ref  |      |      |

| b      | 0.20 | 0.20 0.25 |      | 6    |

| b1     | 0.15 | 0.20      | 0.25 | 6    |

| D      |      | 3.50 BSC  |      |      |

| E      |      | 5.00 BSC  |      |      |

| е      |      | 0.50 BSC  |      |      |

| e1     |      | 0.85 BSC  |      |      |

| K      | 0.55 | 0.60      | 0.65 |      |

| K1     | 0.15 | 0.20      | 0.25 |      |

| SYMBOL | Dimension (mm) |         |      |      |  |

|--------|----------------|---------|------|------|--|

|        | MIN            | Nominal | MAX  | Note |  |

| L      | 0.30           | 0.40    | 0.50 |      |  |

| aaa    |                | 0.05    |      |      |  |

| bbb    |                | 0.10    |      |      |  |

| ccc    |                | 0.10    |      |      |  |

| ddd    |                | 0.05    |      |      |  |

| eee    |                | 0.08    |      |      |  |

| N      |                | 14      |      | 3    |  |

| ND     |                | 6       |      | 5    |  |

| NE     |                | 7       |      | 5    |  |

| Notes  |                | 1, 2    |      |      |  |

#### Notes:

- 1. Dimensioning and tolerancing conform to ASME Y14.5-2009

- 2. All dimensions are in millimeters

- 3. N is the total number of terminals

- A. Dimension **b** applies to the metallized terminal. If the terminal has a radius on the other end of it, dimension **b** should not be measured in that radius area.

- ND and NE refer to the number of terminals on each D and E side respectively.

- Dimension b applies to the metallized terminal and is measured between 0.15 mm and 0.30 mm from the terminal tip. If the terminal has a radius on the other end of it, dimension b should not be measured in that radius area.

- A Coplanarity applies to the terminals and all the other bottom surface metallization.

## Errata Sheet

| STATUS | VERSION | DATE       | REMARK                                                                                                                                                                                                                                       |

|--------|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENGRT  | 1.1     | 12/09/2022 | The following features and parameters do not meet the datasheet description and specifications:                                                                                                                                              |

|        |         |            | 1) The maximum operating VIN voltage should not exceed 64 V                                                                                                                                                                                  |

|        |         |            | 2) The maximum transient voltage at the output switch node SW, should not exceed 70 V. Recommend to use at least 4.7 $\Omega$ for $R_{BOOT}$ and $R_{DRV}$ to module the over-voltage spike above VIN rail and below PGND to less than 10 V. |

Efficient Power Conversion Corporation (EPC) reserves the right to make changes without further notice to any products herein to improve reliability, function or design. EPC does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

$eGaN^{\bullet} \ is a registered trademark of Efficient Power Conversion Corporation. \\ EPC Patent Listing: epc-co.com/epc/AboutEPC/Patents.aspx$

Information subject to change without notice. December, 2022