eGaN® FET DATASHEET EPC7003

# **EPC7003 – Enhancement Mode Power Transistor**

$V_{DS}$  , 100 V  $R_{DS(on)}$  , 30 m $\Omega$  max  $I_D$  , 42 A  $95\% \ Pb \ / \ 5\% \ Sn \ Solder$

Rad Hard eGaN® transistors have been specifically designed for critical applications in the high reliability or commercial satellite space environments. GaN transistors offer superior reliability performance in a space environment because there are no minority carriers for a single event, and as a wide band semiconductor there is less displacement for protons and neutrons, and additionally, there is no oxide to breakdown. These devices have exceptionally high electron mobility and a low-temperature coefficient resulting in very low  $R_{DS(on)}$  values. The lateral structure of the die provides for a very low gate charge ( $Q_G$ ) and extremely fast switching times. These features enable faster power supply switching frequencies resulting in higher power densities, higher efficiencies, and more compact designs.

| Maximum Ratings  |                                                            |            |      |  |

|------------------|------------------------------------------------------------|------------|------|--|

|                  | PARAMETER                                                  | VALUE      | UNIT |  |

| \ \/             | Drain-to-Source Voltage (Continuous)                       | 100        | V    |  |

| V <sub>DS</sub>  | Drain-to-Source Voltage (up to 10,000 5ms pulses at 150°C) | 120        |      |  |

|                  | Continuous                                                 | 10         | Α    |  |

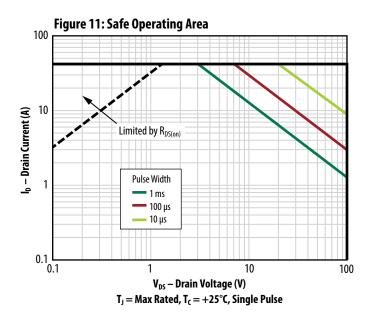

| I <sub>D</sub>   | Pulsed (25°C, $T_{PULSE} = 300 \mu s$ )                    | 42         |      |  |

| .,               | Gate-to-Source Voltage                                     | 6          |      |  |

| $V_{GS}$         | Gate-to-Source Voltage                                     | -4         | V    |  |

| TJ               | Operating Temperature                                      | -55 to 150 | °C   |  |

| T <sub>STG</sub> | Storage Temperature                                        | -55 to 150 |      |  |

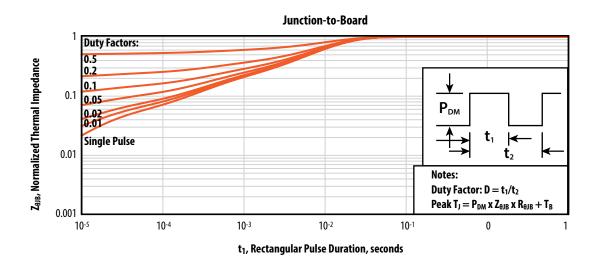

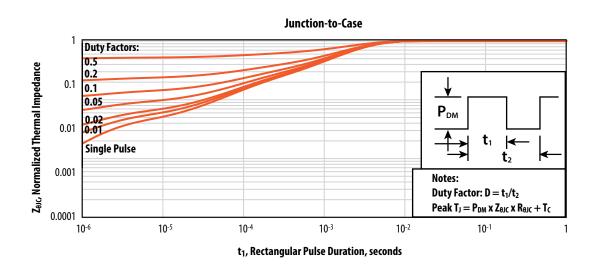

| Thermal Characteristics |                                                                |     |      |  |

|-------------------------|----------------------------------------------------------------|-----|------|--|

|                         | PARAMETER                                                      | TYP | UNIT |  |

| $R_{\theta JC}$         | Thermal Resistance, Junction-to-Case (Case TOP)                | 2.8 |      |  |

| $R_{\theta JB}$         | Thermal Resistance, Junction-to-Board (Case BOTTOM)            | 5.6 | °C/W |  |

| R <sub>0JA_JEDEC</sub>  | Thermal Resistance, Junction-to-Ambient (using JEDEC 51-2 PCB) | 130 | C/VV |  |

| $R_{\theta JA\_EVB}$    | Thermal Resistance, Junction-to-Ambient (EPC9006C EVB)         | 88  |      |  |

EPC7003 eGaN® FETs are supplied only in passivated die form with solder bumps

Die Size: 1.7 x 1.1 mm

#### **Applications**

- Space Applications: DC-DC power, motor drives, lidar, ion thrusters

- Commercial satellite EPS & avionics

- Deep space probes

- · High frequency rad hard DC-DC conversion

- · Rad hard motor drives

#### **Benefits**

- Ultra high efficiency

- Ultra low  $R_{DS(on)}$ ,  $Q_G$ ,  $Q_{GD}$ ,  $Q_{OSS}$ , and  $Q_{RR}$

- Ultra small footprint

- · Light weight

- Total dose

- Rated > 1 Mrad

- Single event

- SEE immunity for LET of 85 MeV/(mg/cm²) with V<sub>DS</sub> up to 100% of rated breakdown

- Neutron

- Maintains pre-rad specification for up to 3 x 10<sup>15</sup> neutrons/cm<sup>2</sup>

- Superior radiation and electrical performance vs. rad hard MOSFETs: smaller, lighter, and greater radiation hardness

| Static Characteristics ( $T_j = 25^{\circ}$ C unless otherwise stated) |                                  |                                                   |     |       |     |      |

|------------------------------------------------------------------------|----------------------------------|---------------------------------------------------|-----|-------|-----|------|

| PARAMETER                                                              |                                  | TEST CONDITIONS                                   | MIN | TYP   | MAX | UNIT |

| $BV_DSS$                                                               | Drain-to-Source Voltage          | $V_{GS} = 0 \text{ V, I}_{D} = 100 \mu\text{A}$   | 100 |       |     | V    |

| $I_{DSS}$                                                              | Drain-Source Leakage             | $V_{DS} = 100 \text{ V}, V_{GS} = 0 \text{ V}$    |     | 0.5   | 100 | μΑ   |

|                                                                        | Gate-to-Source Forward Leakage   | $V_{GS} = 5 V$                                    |     | 0.001 | 0.6 | m A  |

| $I_{GSS}$                                                              | Gate-to-Source Forward Leakage#  | $V_{GS} = 5 \text{ V}, T_J = 125^{\circ}\text{C}$ |     | 0.1   | 1.3 | mA   |

|                                                                        | Gate-to-Source Reverse Leakage   | $V_{GS} = -4 V$                                   |     | 0.5   | 100 | μΑ   |

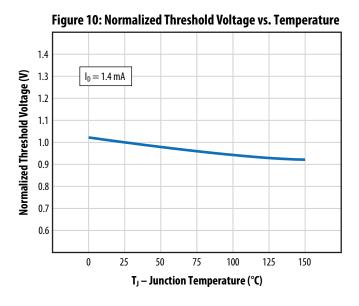

| $V_{GS(TH)}$                                                           | Gate Threshold Voltage           | $V_{DS} = V_{GS}$ , $I_D = 1.4 \text{ mA}$        | 0.8 | 1.4   | 2.5 | V    |

| $R_{DS(on)}$                                                           | Drain-Source On Resistance       | $V_{GS} = 5 \text{ V, } I_D = 6 \text{ A}$        |     | 18    | 30  | mΩ   |

| $V_{SD}$                                                               | Source-to-Drain Forward Voltage# | $I_S = 0.5 \text{ A, } V_{GS} = 0 \text{ V}$      |     | 1.7   |     | V    |

<sup>#</sup> Defined by design. Not subject to production test.

eGaN® FET DATASHEET **EPC7003**

| Dynamic Characteristics <sup>#</sup> (T <sub>J</sub> = 25°C unless otherwise stated) |                                                       |                                                                  |     |     |     |      |

|--------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------|-----|-----|-----|------|

|                                                                                      | PARAMETER                                             | TEST CONDITIONS                                                  | MIN | TYP | MAX | UNIT |

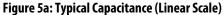

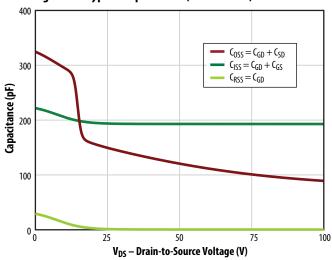

| $C_{ISS}$                                                                            | Input Capacitance                                     |                                                                  |     | 230 | 313 |      |

| $C_{RSS}$                                                                            | Reverse Transfer Capacitance                          | $V_{DS} = 50 \text{ V}, V_{GS} = 0 \text{ V}$                    |     | 0.6 |     |      |

| Coss                                                                                 | Output Capacitance                                    |                                                                  |     | 119 | 143 | pF   |

| C <sub>OSS(ER)</sub>                                                                 | Effective Output Capacitance, Energy Related (Note 1) | V -0+0 F0 V V -0 V                                               |     | 144 |     |      |

| $C_{OSS(TR)}$                                                                        | Effective Output Capacitance, Time Related (Note 2)   | $V_{DS} = 0$ to 50 V, $V_{GS} = 0$ V                             |     | 188 |     |      |

| $R_{G}$                                                                              | Gate Resistance                                       |                                                                  |     | 1.3 |     | Ω    |

| $Q_{G}$                                                                              | Total Gate Charge                                     | $V_{DS} = 50 \text{ V}, V_{GS} = 5 \text{ V}, I_D = 6 \text{ A}$ |     | 1.8 | 2.5 |      |

| $Q_{GS}$                                                                             | Gate-to-Source Charge                                 |                                                                  |     | 0.6 |     |      |

| $Q_{GD}$                                                                             | Gate-to-Drain Charge                                  | $V_{DS} = 50 \text{ V}, I_D = 6 \text{ A}$                       |     | 0.3 |     |      |

| $Q_{G(TH)}$                                                                          | Gate Charge at Threshold                              |                                                                  |     | 0.4 |     | nC   |

| Q <sub>OSS</sub>                                                                     | Output Charge                                         | $V_{DS} = 50 \text{ V}, V_{GS} = 0 \text{ V}$                    |     | 9.4 | 11  |      |

| Q <sub>RR</sub>                                                                      | Source-Drain Recovery Charge                          |                                                                  |     | 0   |     |      |

All measurements were done with substrate connected to source.

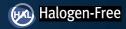

Figure 1: Typical Output Characteristics at 25 °C

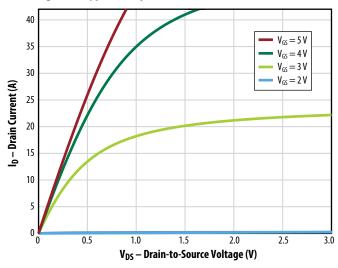

**Figure 2: Typical Transfer Characteristics**

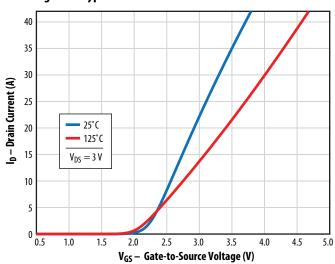

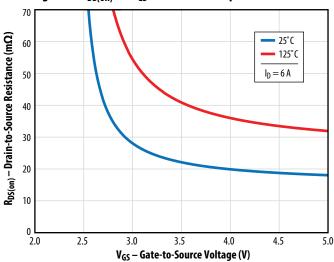

Figure 4: R<sub>DS(on)</sub> vs. V<sub>GS</sub> for Various Temperatures

<sup>#</sup> Defined by design. Not subject to production test.

Note 1:  $C_{OSS(ETB)}$  is a fixed capacitance that gives the same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 50% BV<sub>DSS</sub>. Note 2:  $C_{OSS(TTB)}$  is a fixed capacitance that gives the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 50% BV<sub>DSS</sub>.

eGaN® FET DATASHEET EPC7003

Figure 5b: Typical Capacitance (Log Scale)

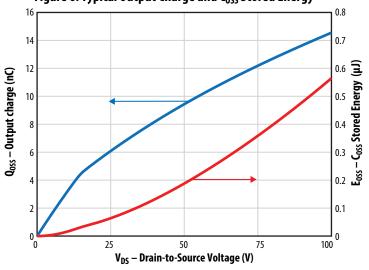

Figure 6: Typical Output Charge and Coss Stored Energy

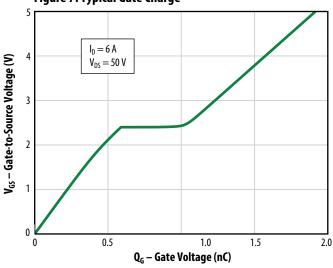

Figure 7: Typical Gate Charge

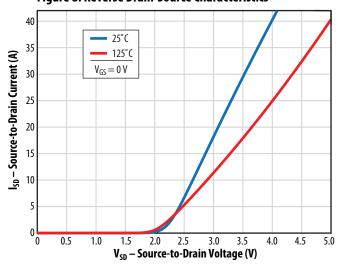

**Figure 8: Reverse Drain-Source Characteristics**

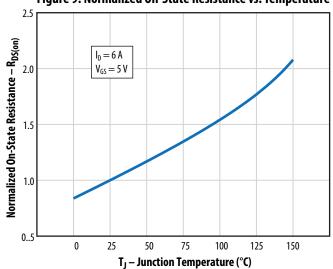

Figure 9: Normalized On-State Resistance vs. Temperature

**Note:** Negative gate drive voltage increases the reverse drain-source voltage. EPC recommends 0 V for OFF.

eGan® FET DATASHEET EPC7003

**Figure 12: Transient Thermal Response Curves**

**EPC7003** eGaN® FET DATASHEET

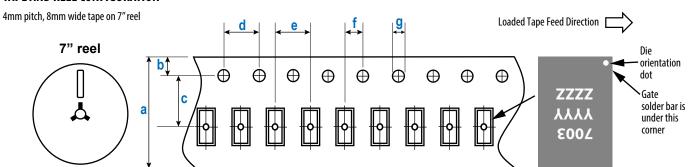

### **TAPE AND REEL CONFIGURATION**

|                  | Dimension (mm) |      |      |

|------------------|----------------|------|------|

| EPC7003 (Note 1) | Target         | MIN  | MAX  |

| a                | 8.00           | 7.90 | 8.30 |

| b                | 1.75           | 1.65 | 1.85 |

| (Note 2)         | 3.50           | 3.45 | 3.55 |

| d                | 4.00           | 3.90 | 4.10 |

| е                | 4.00           | 3.90 | 4.10 |

| f (Note 2)       | 2.00           | 1.95 | 2.05 |

| g                | 1.50           | 1.50 | 1.60 |

Note 1: MSL 1 (moisture sensitivity level 1) classified according to IPC/

Die is placed into pocket solder bar side down (face side down)

JEDEC industry standard. Note 2: Pocket position is relative to the sprocket hole measured as true position of the pocket, not the pocket hole.

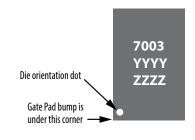

## **DIE MARKINGS**

| Part    |                               | Laser Markings                  |                                 |

|---------|-------------------------------|---------------------------------|---------------------------------|

| Number  | Part Number<br>Marking Line 1 | Lot_Date Code<br>Marking Line 2 | Lot_Date Code<br>Marking Line 3 |

| EPC7003 | 7003                          | YYYY                            | ZZZZ                            |

eGaN® FET DATASHEET **EPC7003**

(685)

87 +/- 17

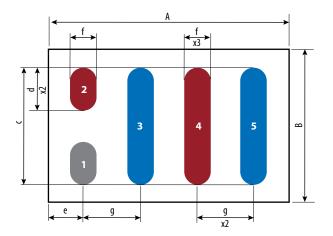

# **DIE OUTLINE**

Solder Bar View

Side View

| DIM | MICROMETERS |         |      |  |

|-----|-------------|---------|------|--|

| DIM | MIN         | Nominal | MAX  |  |

| A   | 1672        | 1702    | 1732 |  |

| В   | 1057        | 1087    | 1117 |  |

| C   | 829         | 834     | 839  |  |

| d   | 311         | 316     | 321  |  |

| e   | 235         | 250     | 265  |  |

| f   | 195         | 200     | 205  |  |

| q   | 400         | 400     | 400  |  |

Pad no. 1 is Gate;

Pads no. 2 and 4 are Source;

Pads no. 3 and 5 are Drain

Substrate (top side) connected to Source

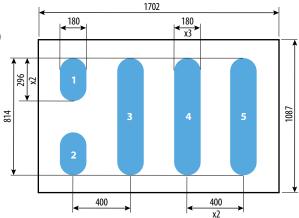

# **RECOMMENDED LAND PATTERN**

(measurements in  $\mu$ m)

Seating Plane

The land pattern is solder mask defined

Pad no. 1 is Gate;

Pads no. 2 and 4 are Source;

Pads no. 3 and 5 are Drain

Efficient Power Conversion Corporation (EPC) reserves the right to make changes without further notice to any products herein to improve reliability, function or design. EPC does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others. eGaN® is a registered trademark of Efficient Power Conversion Corporation. EPC Patent Listing: epc-co.com/epc/AboutEPC/Patents.aspx

Information subject to change without notice. Revised October, 2022