### The eGaN<sup>®</sup> Technology **Journey Continues**

**Physics Based Model of eGaN Device Gate** Failure Mechanism and Dynamic R<sub>DS(on)</sub> Alex Lidow, Ph.D.

# EFFICIENT POWER CONVERSIO

## **Die and Package Stress Tests**

### **RELIABILITY REPORT**

Phase Twelve Testing

EPC eGaN® Device Reliability Testing: Phase 12

Alejandro Pazo Ph.D., Shenake Zhand Ph.D., Gordon Stecklein Ph.D., Reardo Garcia, John Glaser Ph.D., Zhikai Tang Ph.D., and Robert Strittmatter Ph.D., Efficient Power Conversion

The rapid adoption of Efficient Power Conversion's (EPC) eGaN\* devices in many diverse applications calls for continued accumulation of reliability statistics and research into the fundamental physics of failure in GaN devices. This Phase 12 reliability report adds to the growing knowledge base published in the first eleven reports [1-11] and covers several key new topics.

Gallium nitride (GaN) power devices have been in volume production since March 2010 [12] and have established a remarkable field reliability record. This report presents the strategy used to achieve this track record that relied upon tests forcing devices to fail under a variety of conditions to create stronger and stronger products for the industry.

### NEED FOR ADDITIONAL STANDARD QUALIFICATION TESTING

### Why test-to-fail in addition to standard gualification testing?

out of a relatively large group of parts tested.

passed a very specific test condition. By testing parts to the point of failure, an understanding of the amount of margin between understanding of the intrinsic failure mechanisms can be found. By knowing the intrinsic failure mechanisms, the root cause of failure, and the behavior of the device over time, temperature, electrical or mechanical stress, the safe operating life of a product can be determined over a more general set of operating conditions (For an excellent description of this methodology for testing semiconductor devices, see reference [13]).

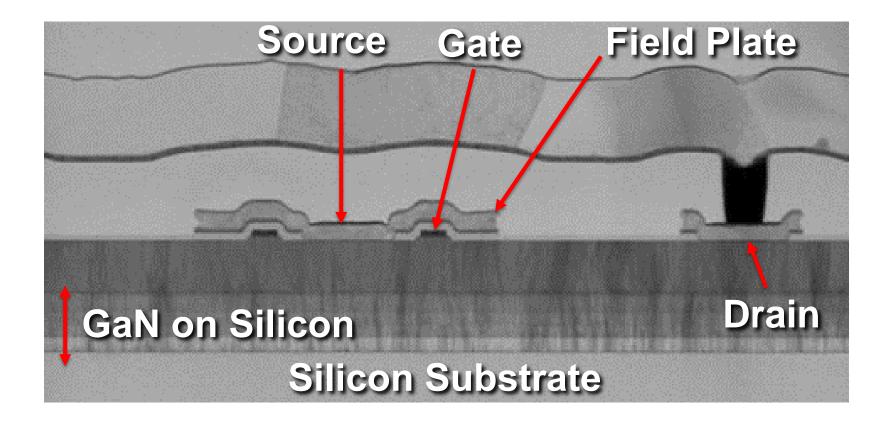

### Key Stress Conditions and Intrinsic Failure Mechanisms for GaN **Power Devices**

What are the key stress conditions encountered by GaN power devices and what are the intrinsic failure mechanisms for each stress condition?

As with all power transistors, the key stress conditions involve voltage, current, temperature, and humidity, as well as various mechanical stresses. There are, however, many ways of applying these stress conditions. For example, voltage stress on a GaN FET can be applied from the gate terminal to the source terminal (V<sub>os</sub>), as well as from the drain terminal to the source terminal (Vps). For example, these stresses can be applied continuously as a DC bias, they can be cycled on-and-off, or they can be applied as high-speed pulses. Current stress can be applied as a continuous. DC current, or as a pulsed current. Thermal stresses can be applied continuously by operating devices at a predetermined temperature extreme for a period of time, or temperature can be cycled in a variety of ways.

By stressing devices with each of these conditions to the point of generating a significant number of failures, an understanding of the primary intrinsic failure mechanisms for the devices under test can be determined. To generate failures in a reasonable amount Standard gualification testing for semiconductors typically of time, the stress conditions typically need to significantly exceed the datasheet limits involves stressing devices at or near the limits specified in their of the product. Care needs to be taken to make certain the excess stress condition datasheets for a prolonged period of time, or for a certain number does not induce a failure mechanism that would never be encountered during normal of cycles. The goal of qualification testing is to have zero failures operation. To make certain this is not the case, the failed parts need to be carefully analyzed to determine the root cause of their failure.

This type of testing is inadequate since it only reports parts that Only by verifying the root cause can a true understanding of the behavior of a device under a wide range of stress conditions be developed. It should be noted that, as more understanding of intrinsic failure modes in eGaN devices is gained, two facts have become clear; (1) eGaN devices are more robust that Si-based MOSFETs, and the datasheet limits can be developed, and more importantly, an (2) MOSFET intrinsic failure models are not valid when predicting eGaN device lifetime under extreme or long-term electrical stress conditions.

| Stressor                          | Device/<br>Package | Test Method                            | Intrinsic Failure<br>Mechanism | EPC Test Results     |

|-----------------------------------|--------------------|----------------------------------------|--------------------------------|----------------------|

| Voltage                           | Device             | HIGB                                   | Dielectric failure (TODB)      | This Report          |

|                                   |                    |                                        | Threshold shift                |                      |

|                                   |                    | HTRB                                   | Threshold shift                | This Report          |

|                                   |                    |                                        | R <sub>OSioni</sub> shift      |                      |

|                                   |                    | ESD                                    | Dielectric rupture             | [2,3,6,7,8,9,10]     |

| Current                           | Device             | OC Current (EM)                        | Bectromigration                | In Progress          |

|                                   |                    |                                        | Thermomigration                | In Progress          |

| Current + Woltage<br>(Power)      | Device             | SOA                                    | Thermal Runaway                | This Report          |

|                                   |                    | Short Circuit                          | Thermal Runaway                | This Report          |

| Voltage Rising/Falling            | Device             | Hard-switching Reliability             | Rosine shift                   | This Report          |

| Current Rising/Falling            | Device             | Pulsed Current.<br>(Lidar reliability) | None found                     | This Report          |

| Temperature                       | Package            | HTS                                    | None found                     | [6,7,8,9]            |

| Humidity                          | Package            | MSL1                                   | None found                     | [3,4,5,6,7,8,9,10]   |

|                                   |                    | HEIRB                                  | None found                     | 1,2,3,4,5,6,7,8,9,10 |

|                                   |                    | ML.                                    | None found                     | 4,5,6,7,8,9          |

|                                   |                    | Solderability                          | Solder corrosion               | This Report          |

|                                   |                    | uHAST                                  | Denrite Formation/Corrosion    | [10]                 |

| Mechanical /<br>Thermo-mechanical | Package            | TC.                                    | Solder Fatigue                 | This Report          |

|                                   |                    | IÚL                                    | Solder Fatigue                 | This Report          |

|                                   |                    | Bending Force lest                     | Delamination                   | This Report          |

|                                   |                    | Bending Force Test                     | Solder Strength                | This Report          |

|                                   |                    | Bending Force Test                     | Piezoielectric Effects         | This Report          |

|                                   |                    | Die shear                              | Solder Strength                | This Report          |

|                                   |                    | Package force                          | Film Cracking                  | This Report          |

1.1

EPC - POWER CONVERSION TECHNOLOGY LEADER | EPC-CO.COM | ©2021

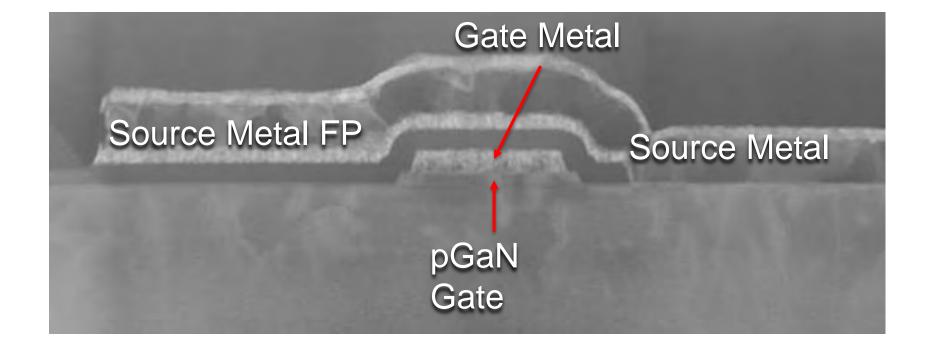

# **Stress – Voltage** Gate-Source

# **Gate-Source Voltage Stress**

=

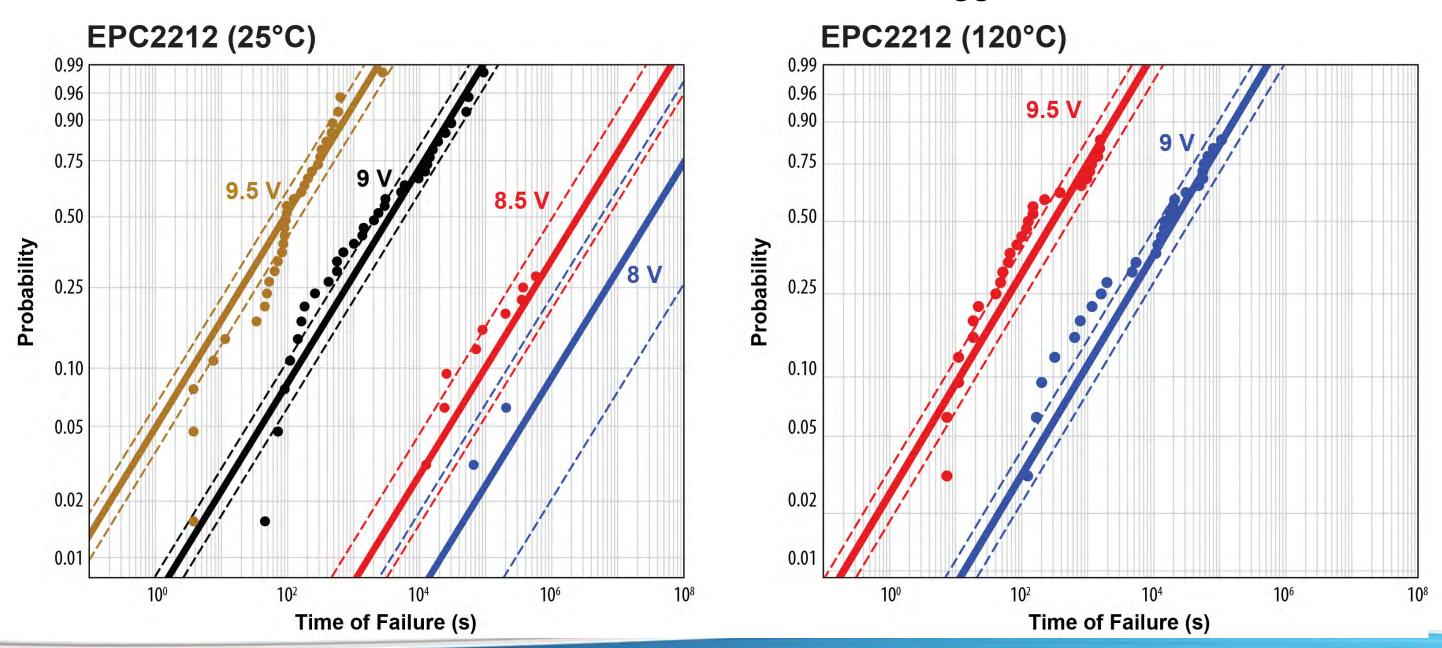

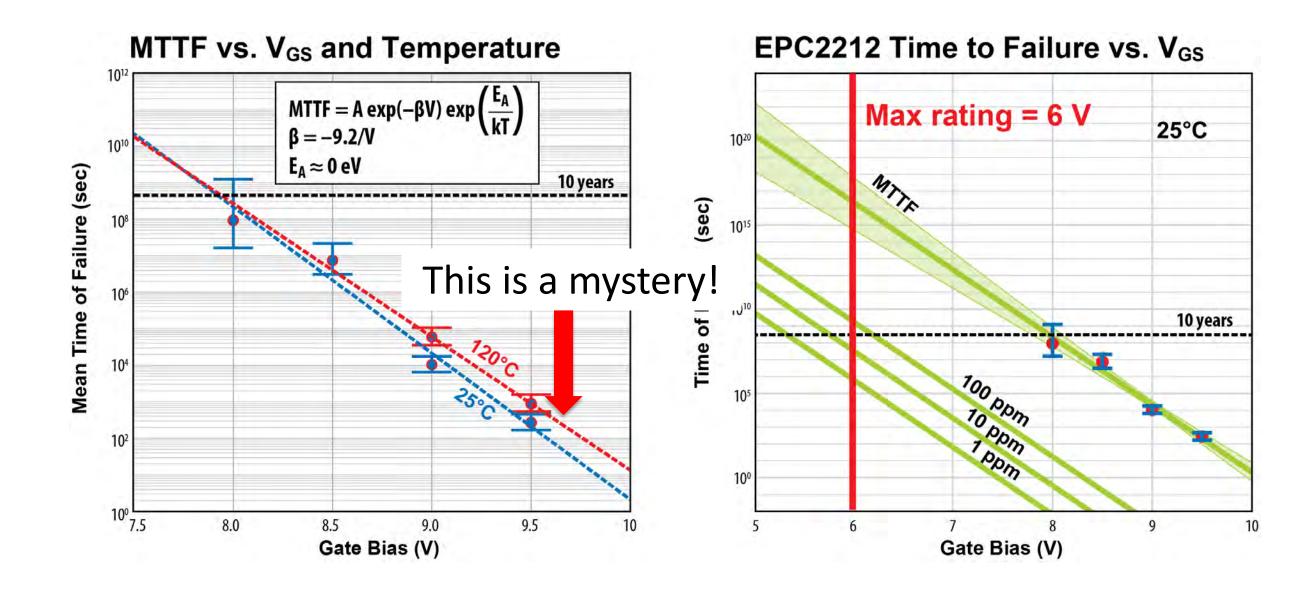

# **Gate Acceleration: Analysis**

### Data Sheet Maximum = $6 V_{GS}$

epc-co.com

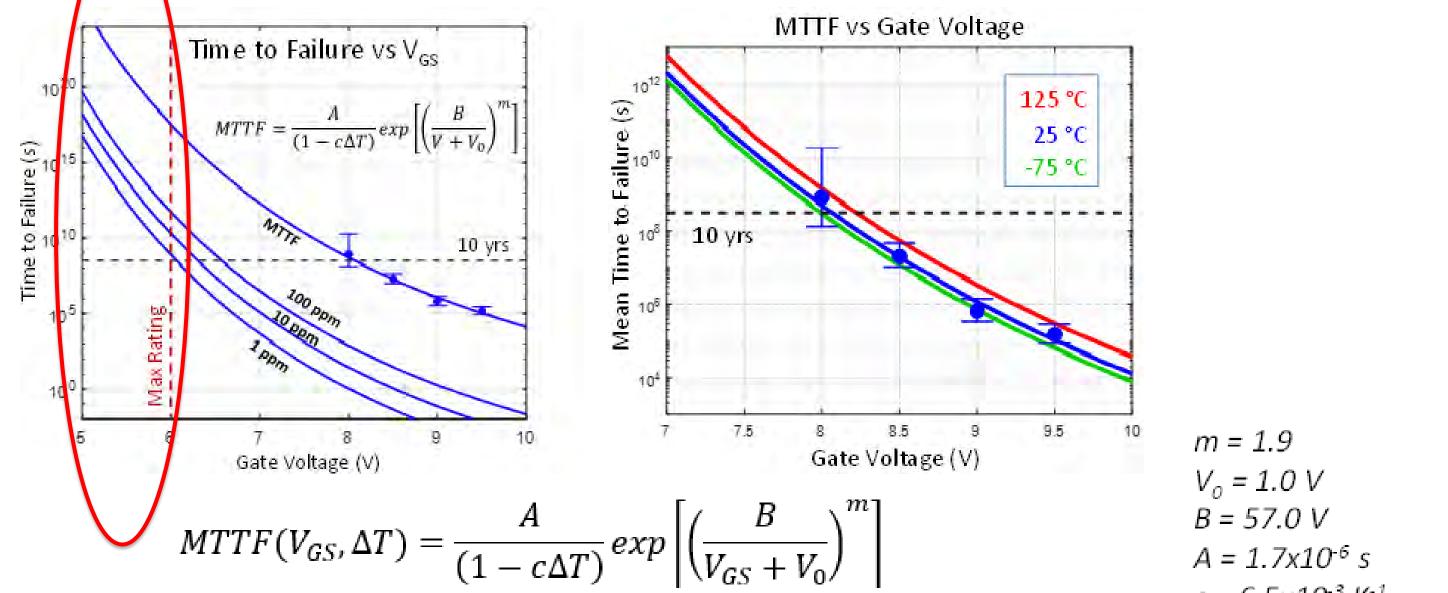

# **Gate Acceleration: Time to Failure**

=

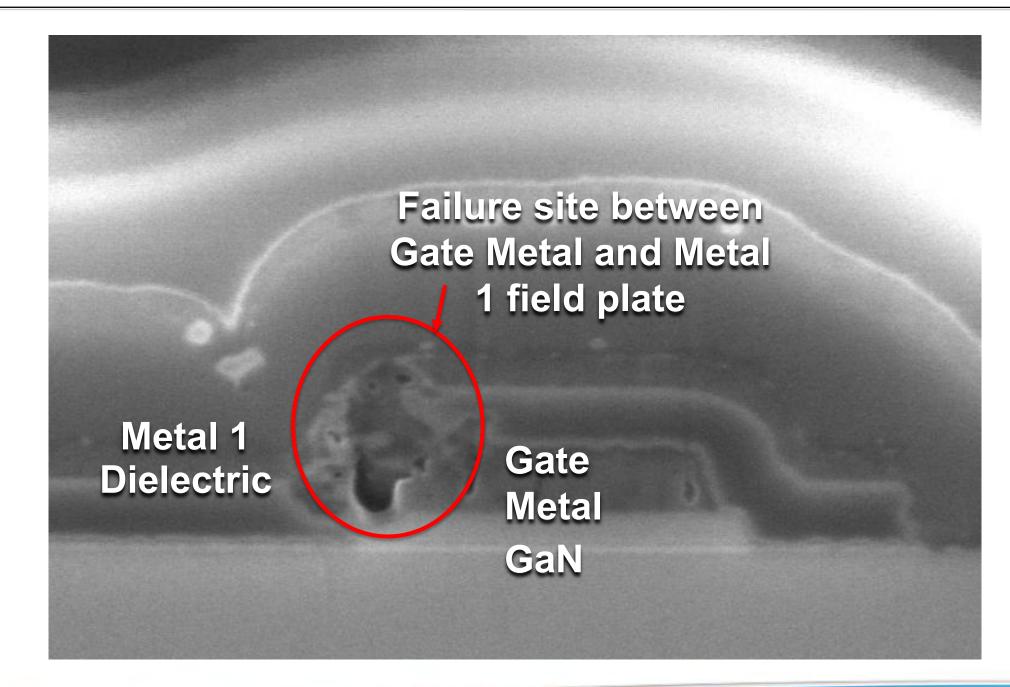

# **Gate Failures Not in GaN**

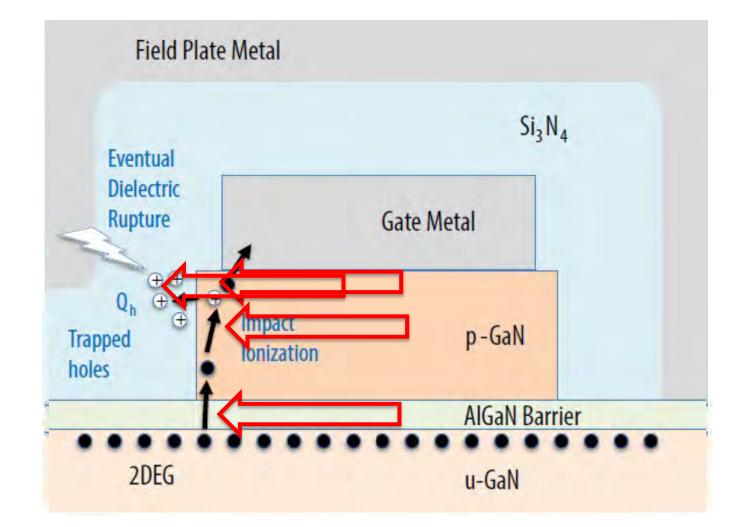

# **Impact Ionization Mechanism**

## **Impact Ionization Model Development**

$$G = \alpha_n \frac{|J_n|}{q} + \alpha_p \frac{|J_p|}{q} \qquad \qquad \alpha_n = a_n e^{-(b_n/F)^m}$$

| Ref             | a <sub>n</sub> (1/cm) | b <sub>n</sub> (V/cm) | m   |

|-----------------|-----------------------|-----------------------|-----|

| Ji et al.[12]   | 2.10E+09              | 3.70E+07              | 1   |

| Ozbek [13]      | 9.20E+05              | 1.70E+07              | 1   |

| Cao et al. [8]  | 4.48E+08              | 3.40E+07              | 1   |

| Ooi et al. [15] | 7.32E+07              | 7.16E+06              | 1.9 |

$$a_n(T) = a_{n;0}(1 - c\Delta T)$$

$c = 6.5x10^{-3} K^{-1}$

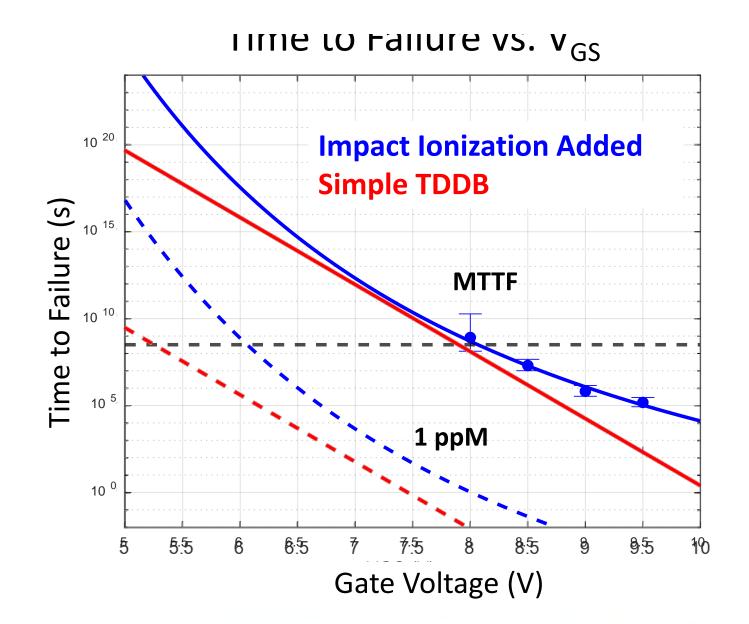

$$G \approx \alpha_n \frac{|J_n|}{q} \qquad J_n \gg J_p \qquad MTTF \propto \frac{Q_c}{G} \qquad MTTF \propto \frac{Q_c}{G} = \frac{qQ_c}{\alpha_n J_n} = \frac{1}{J_n a_{n,0}}$$

$$MTTF = \frac{Q_c}{G} = \frac{qQ_c}{\alpha_n J_n} = \left[\frac{A}{(1-c\Delta T)} exp\left[\left(\frac{B}{V+V_0}\right)^m\right]\right] \qquad \stackrel{m=1.9}{\underset{k=57.0 \text{ V}}{\overset{k=57.0 \text{ V}}{\alpha_n J_n}}$$

Ę

# $\frac{qQ_c}{a_{n,0}(1-c\Delta T)}\exp\left[\left(\frac{b_n}{F}\right)^m\right]$

# Theory vs. Experimental Results

$c = 6.5 \times 10^{-3} K^{-1}$

10

# **TDDB vs. Impact Ionization Models**

Ę

# **Stress – Voltage** Drain-Source

# **Drain-Source Voltage Stress**

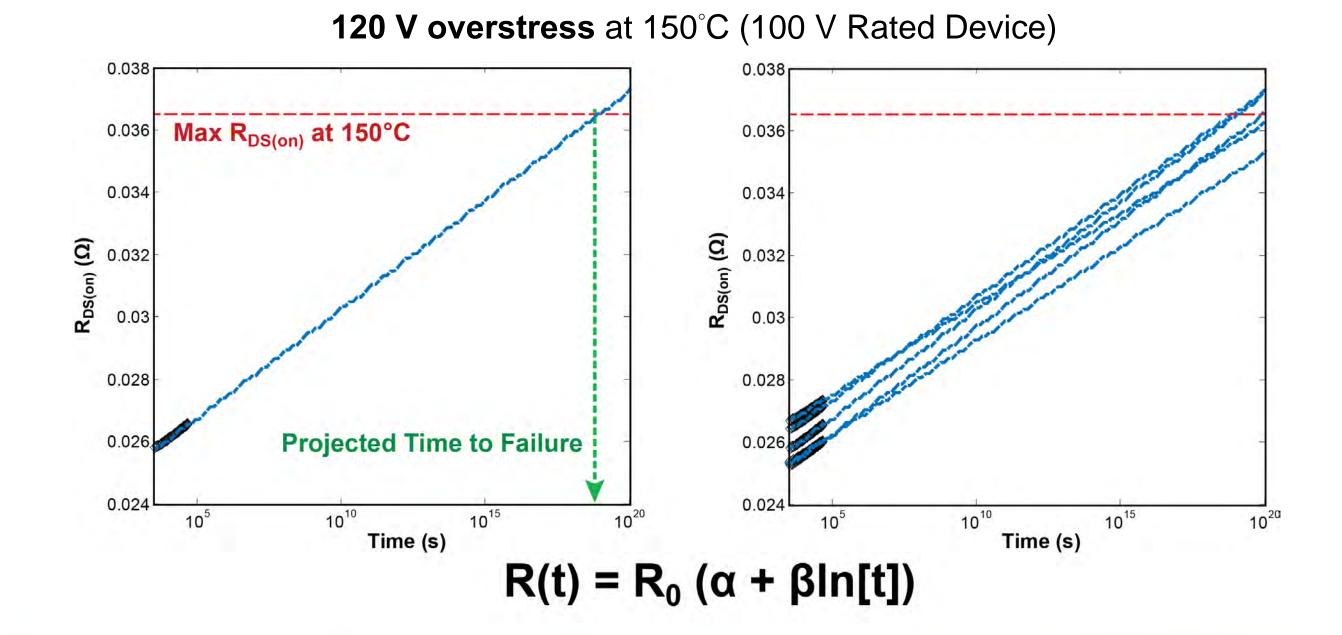

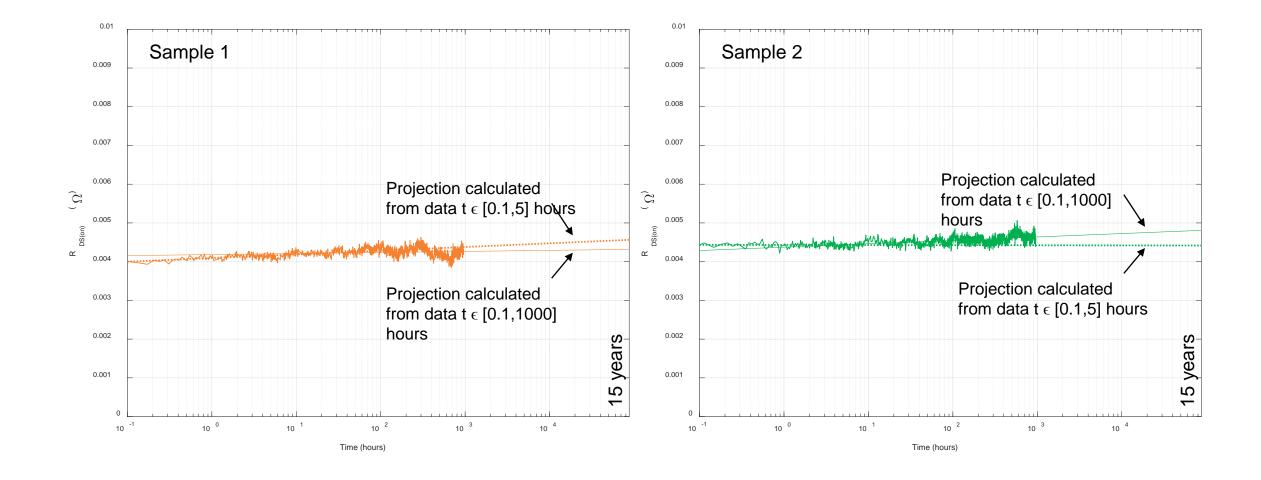

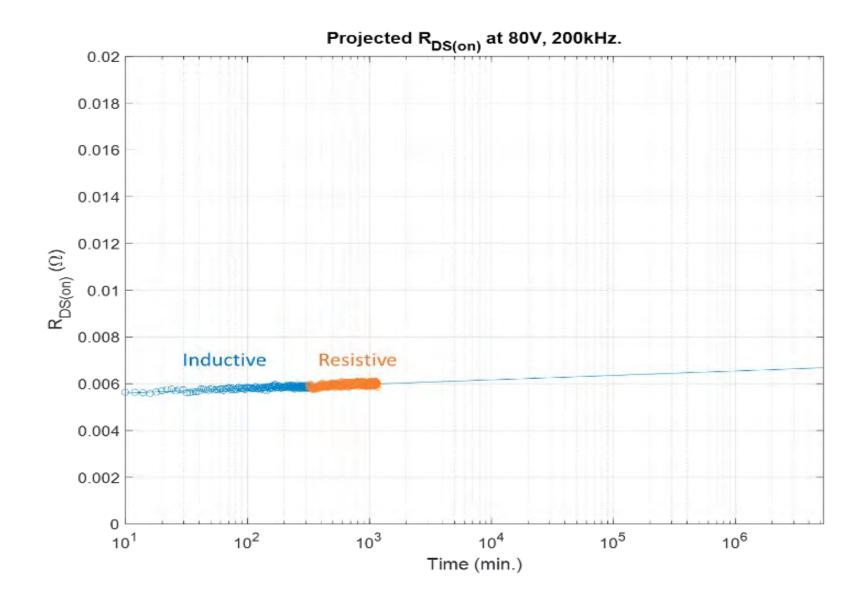

# **Characterizing R**<sub>DS(on)</sub> Shift in Time

# **R**<sub>DS(on)</sub> **Projection Analysis**

Ę

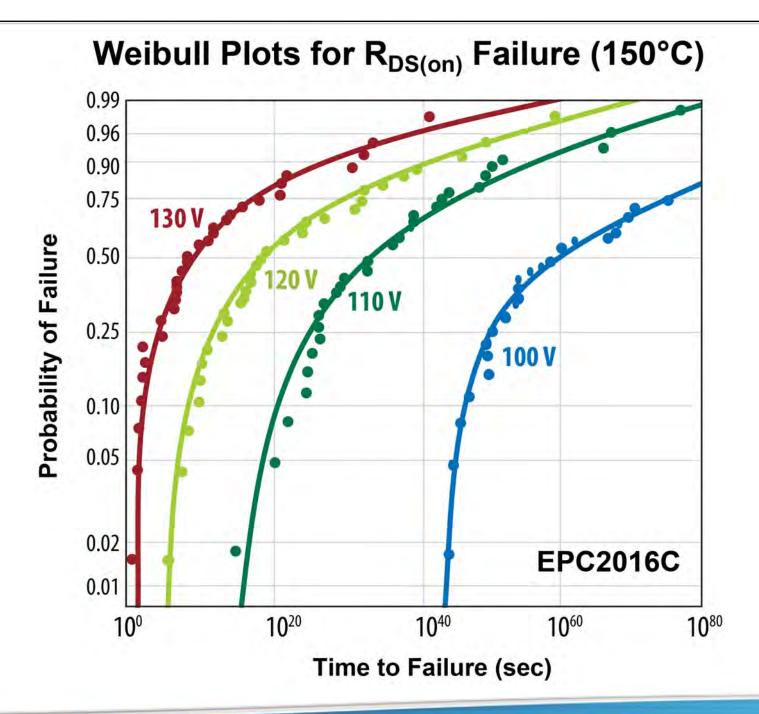

# **Drain Stress Weibull Fits**

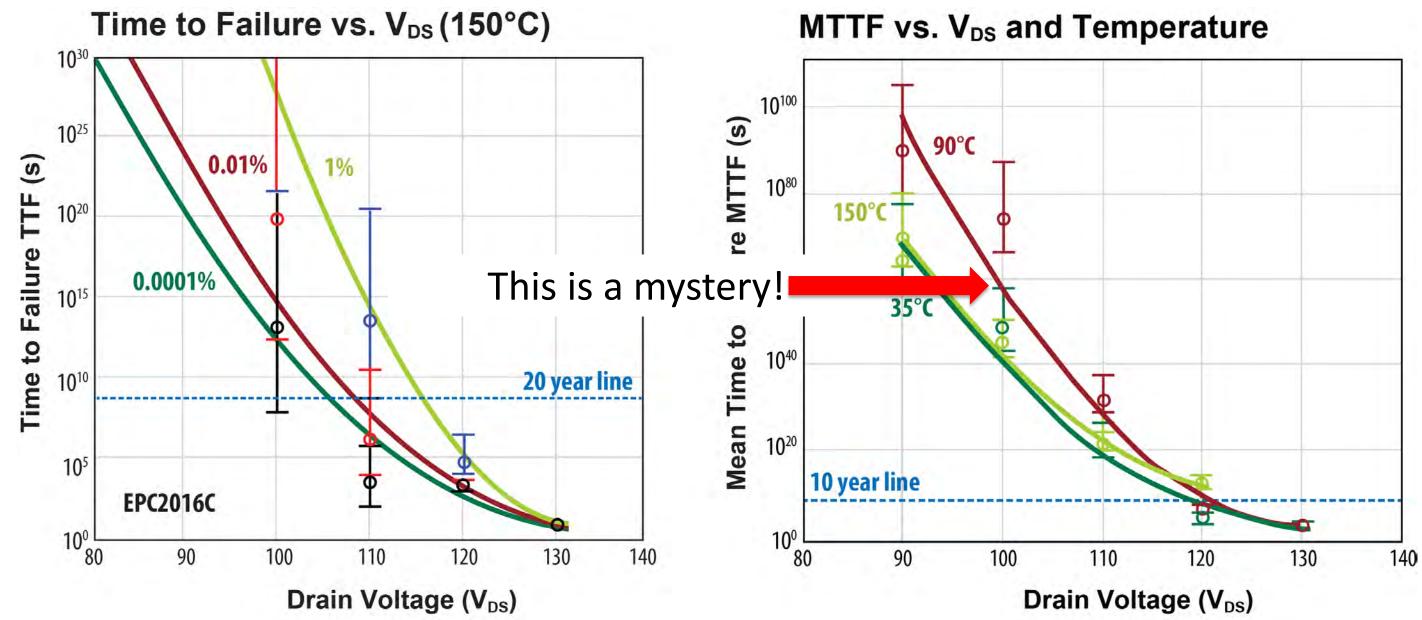

# **Device Robustness vs. V<sub>DS</sub>**

17

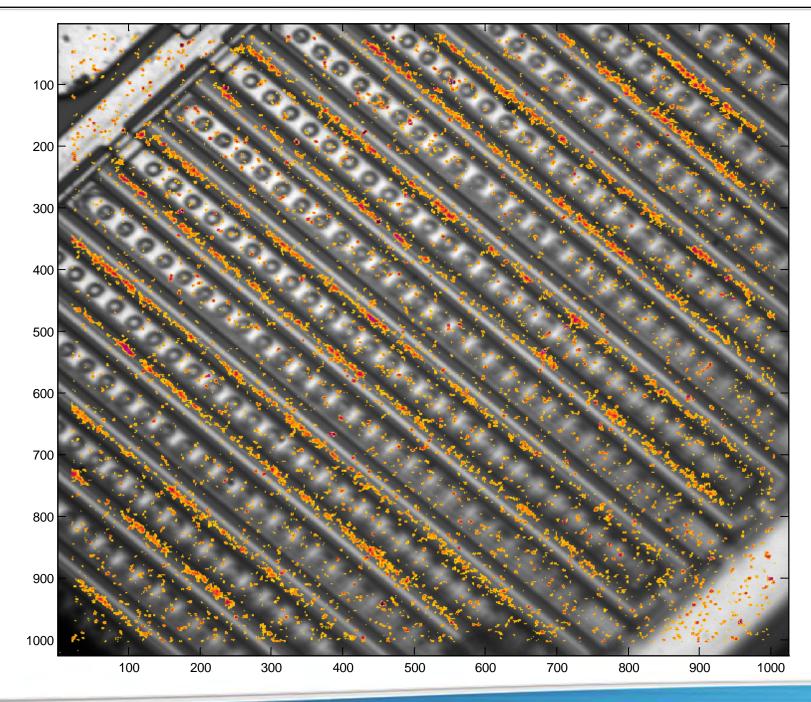

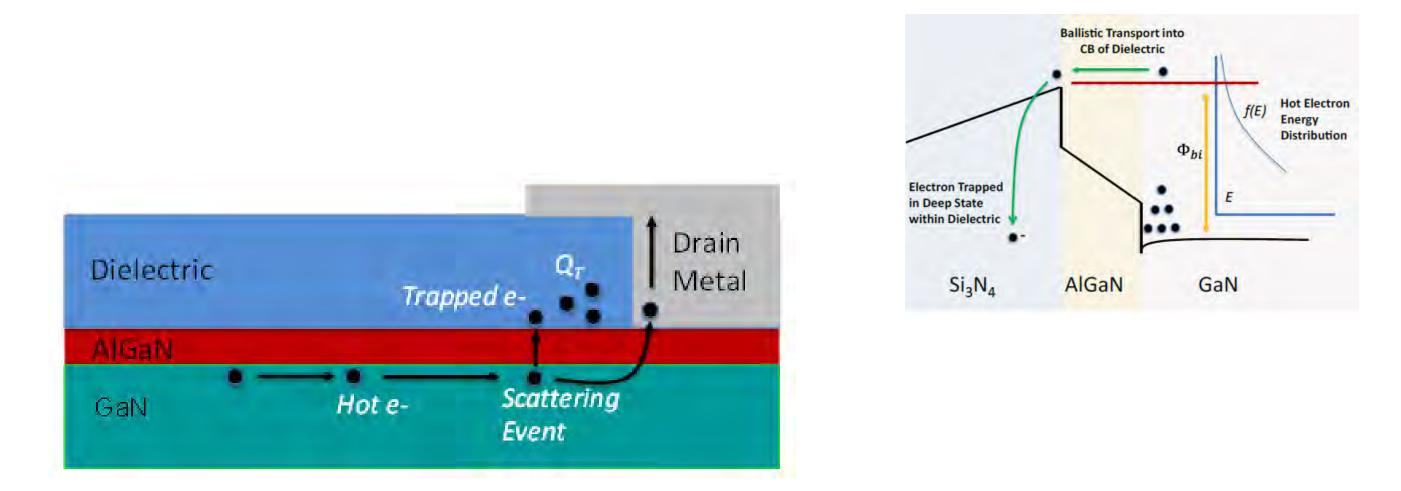

# Physics of R<sub>DS(on)</sub> Shift – Hot Carrier Emission

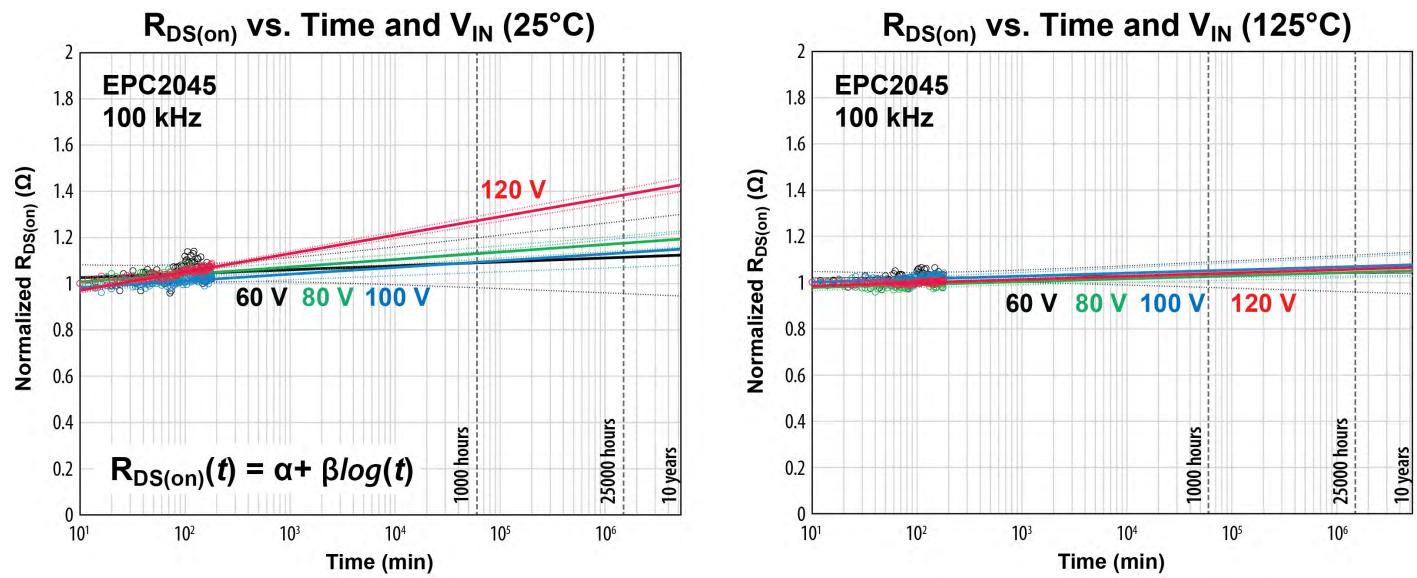

# Hard-Switching: Effect of V<sub>IN</sub>

F

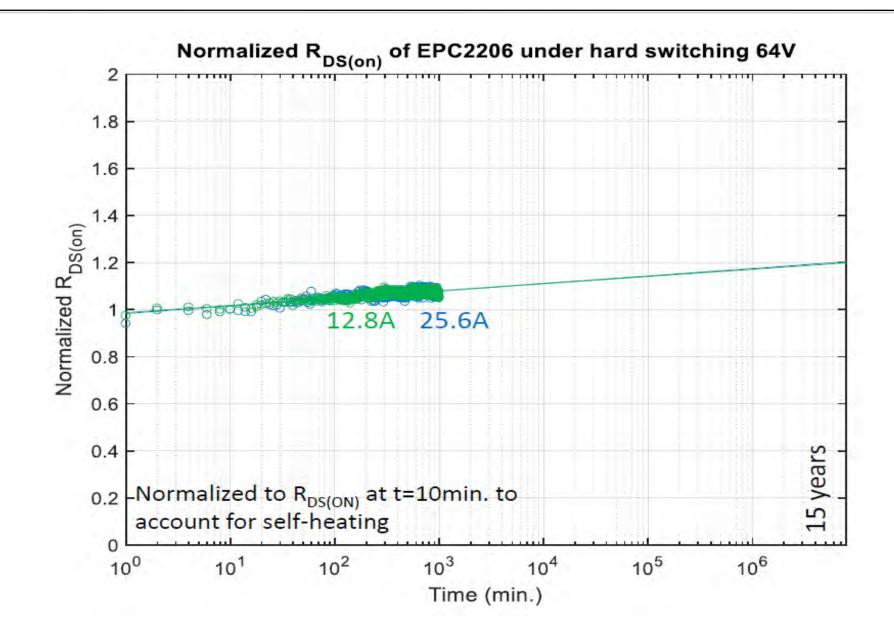

# Impact of Switched Current

# Inductive vs. Resistive Switching

# **Hot Carrier Trapping Mechanism**

### **Hot Carrier Trapping Model**

Ę

$$f(E)dE \propto Ee^{-E/qF\lambda}dE \quad \frac{dQ_s}{dt} = A \int_{\phi_{bl}+\beta Q_s}^{\infty} f(E)dE = A \int_{\phi_{bl}+\beta Q_s}^{\infty} Ee^{-E/qF\lambda}dE$$

$$Q_s(t) = \frac{qF\lambda}{\beta} \log\left(1 + \frac{B\beta}{qF\lambda}t\right) \qquad R(t) = R_0 + \frac{C}{Q_P - Q_s} = R_0 + \frac{Q_P - \frac{qF\lambda}{\beta}}{Q_P - \frac{qF\lambda}{\beta}}$$

$$R(t) \approx R_0 + \frac{C}{Q_P} \left[1 + \frac{qF\lambda}{Q_P\beta} \log\left(1 + \frac{B\beta}{qF\lambda}t\right)\right] \qquad \tau_{LO} \propto exp\left(\frac{\hbar\omega_{LO}}{kT}\right) \quad \lambda = v_{th}\tau_{LO}$$

$$\frac{\Delta R}{R} = \frac{R(t) - R(0)}{R(0)} \approx a + bF \exp\left(\frac{\hbar\omega_{LO}}{kT}\right) \sqrt{T} \log\left(\frac{\hbar\omega_{LO}}{kT}\right)$$

$\frac{dQ_S}{dt} = B \exp\left(-\frac{\beta Q_S}{qF\lambda}\right)$

С  $\frac{\lambda}{\log\left(1 + \frac{B\beta}{qF\lambda}t\right)}$

$\propto A\sqrt{kT}exp\left(\frac{\hbar\omega_{LO}}{kT}\right)$

$\log(t)$

2323

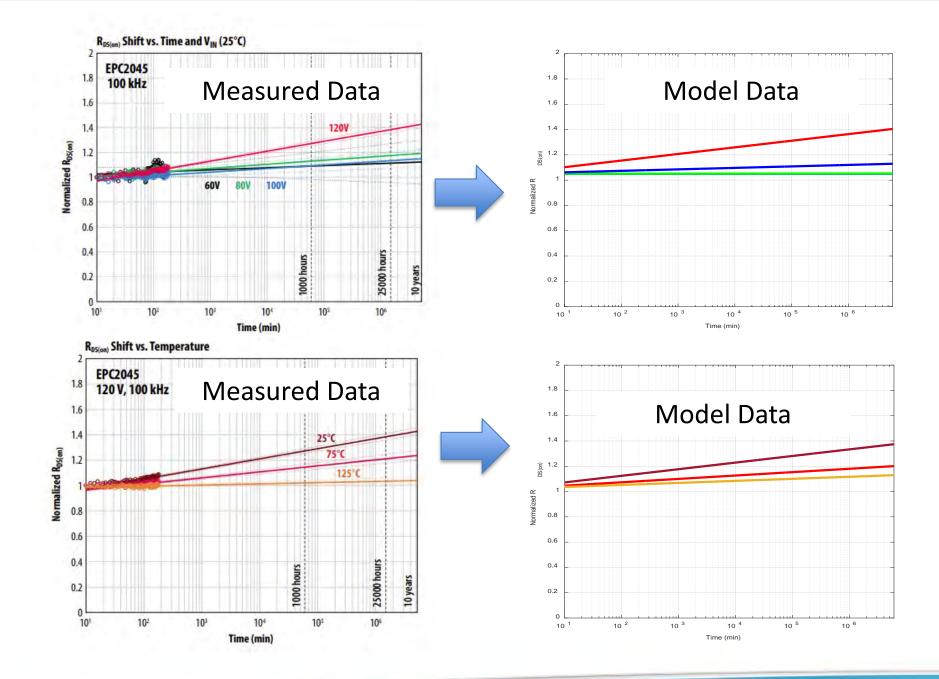

### Putting it All Together – Hot Carrier Trapping Model

$$\frac{\Delta R}{R} = \frac{R(t) - R(0)}{R(0)} \approx a + bF \exp\left(\frac{\hbar\omega_{LO}}{kT}\right) \sqrt{T} \log\left(\frac{kT}{kT}\right) \sqrt{$$

$$= a + b \left[ \frac{V_{DS}}{1 + exp[-\alpha(V_{DS} - V_{FD})]} \right]^2 exp\left( \frac{2\hbar\omega_{LO}}{kT_l} \right) \log(t)$$

a = 0.02 (unitless)

b = 1.9E-8 (V<sup>-2</sup>)

$$\hbar\omega_{LO}$$

= 92 meV

V<sub>FD</sub> = 100V (appropriate for Gen5 100V products only)

$\alpha$  = 0.1 (V<sup>-1</sup>)

t = time in min

F

# g(t)

# **Model vs Measurement**

# **Field Results**

=

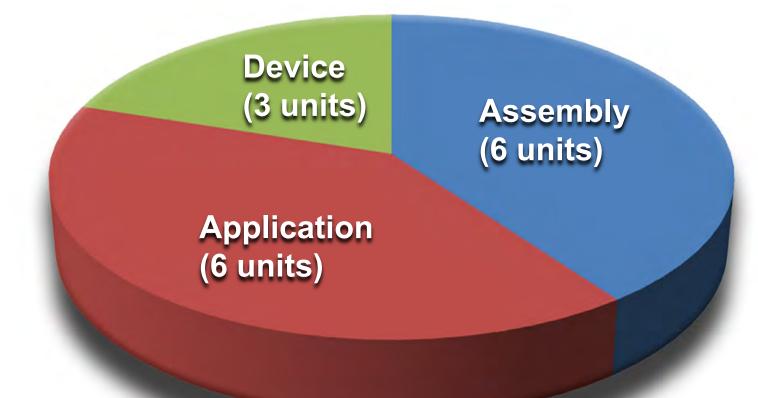

# eGaN FET Reliability

## **Field Failures by Category** 1/1/2017– 12/31/2020

# Proven Reliability – 226 billion device hours in the field since January 1, 2017 with only 3 device failures.

epc-co.com

# **EFFICIENT POWER CONVERSION**

### How To GaN Video Series

# **GaN Transistors for Efficient Power** Conversion

Johan Strydom

David Reusch John Glaser

WILEY

### eGaN<sup>®</sup> FETs and ICs

**Evaluation Kits**

### **3<sup>rd</sup> Edition Textbook**

epc-co.com

## **Next Webinar**