# **GaN Reliability and Lifetime Projections:** Phase 16

Siddhesh Gajare, Ph.D., Duanhui Li, Ph.D., Ricardo Garcia, Gerald Adriano, Angel Espinoza, Han Gao, Ph.D., Gordon Stecklein, Ph.D., Shengke Zhang, Ph.D. <sup>1</sup>Efficient Power Conversion <sup>2</sup>SkyWater Technology

The rapid adoption of Gallium Nitride (GaN) devices in many diverse applications calls for continued accumulation of reliability statistics and research into the fundamental physics of failure in GaN devices, including integrated circuits (ICs). It is also necessary to look for information from real-world experience that either confirms the laboratory-derived data or opens new questions about mission robustness. This Phase 16 Reliability Report documents continued work using test-to-fail methodology and adds guidelines for improving thermo-mechanical reliability.

## **FOCUS AND STRUCTURE OF THIS REPORT**

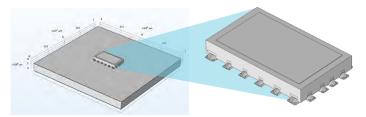

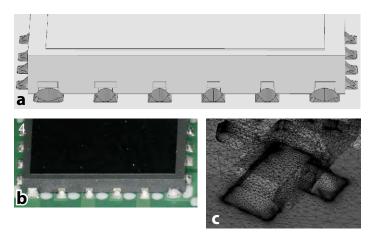

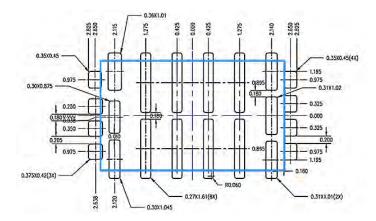

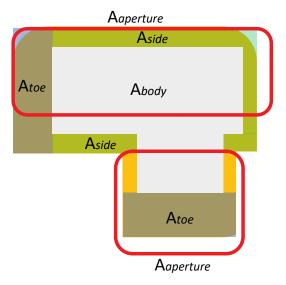

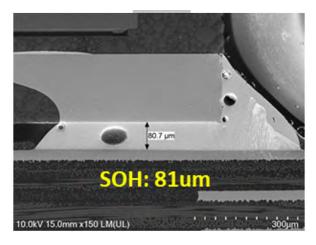

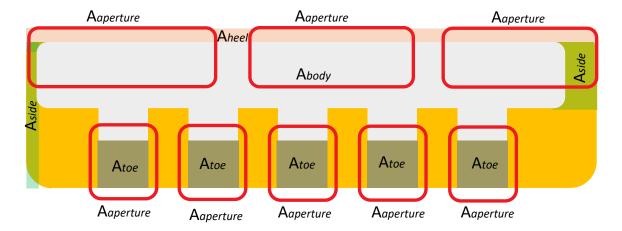

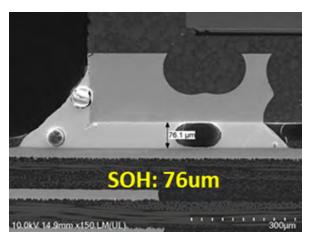

Compared to the Phase 15 Reliability Report [1], this version presents expanded data and analysis. It now includes a general overview of the wear-out mechanisms of primary concern for a given application, which is intended as an introduction to readers new to GaN reliability. Section 1 describes the benefits of testing to failure and how this methodology leads to progress in GaN reliability by revealing a device's intrinsic failure mechanisms. Section 2, which is new to this version of the report, describes how to forecast the reliability of a system in a realistic mission profile that combines periods of substantial and minor stress. The fundamental wear-out mechanisms are discussed individually in Section 3. Compared to previous versions of this report, the thermo-mechanical wear-out mechanisms and overvoltage guidelines include significant new material. Finally, Section 4 reports on the reliability of GaN in specific solar, DC-DC conversion, and light detection and ranging (lidar) applications. A method for optimizing solder stencils for reliable assembly is provided in the Appendix (Section 6), which shows how to determine the solder stand-off height of Power Quad Flat No-Lead (PQFN) packaged GaN FETs.

#### **GETTING STARTED WITH GAN RELIABILITY**

Gallium nitride (GaN) high-electron mobility transistors (HEMTs) have revolutionized power conversion technology due to GaN's superior material properties, which lead to smaller die size, lower on-resistance, and lower parasitic capacitance than their Si-based counterparts. In recent decades, GaN has been increasingly deployed in advanced applications such as light detection and ranging (lidar) for autonomous and commercial vehicles, rooftop solar panels, DC-DC converters for servers, data centers, satellites, motor drives for drones, robots, and power tools. As an emerging technology, the stability, reliability, and robustness of GaN HEMTs attracts significant attention.

The primary wear-out mechanisms in GaN include voltage related wear-out, current density driven wear-out, thermo-mechanical wearout predominantly caused by thermal expansion (CTE) mismatch, and mechanical stress wear-out that is more assembly and application related. To understand which wear-out mechanisms are of primary concern for a given application, designers who are new to GaN are directed to Tables 1 and 2. As listed in the "for details" column of Table 2, this report provides experimental studies and theoretical analysis of all major GaN reliability stressors, with results that can differ from traditional Si-based devices.

| Application | Package | Gate-<br>related | Drain-<br>related | Current<br>Density-<br>related | Thermo-<br>Mechanical-<br>related | Mechanical<br>Stress-<br>related |

|-------------|---------|------------------|-------------------|--------------------------------|-----------------------------------|----------------------------------|

| DC-DC       | CSP     |                  | С                 |                                | Α                                 | Е                                |

| DC-DC       | PQFN    |                  | С                 |                                | В                                 |                                  |

| Lidar       | CSP     | D                |                   | F                              |                                   | Е                                |

| Lidar       | PQFN    | D                |                   | F                              |                                   |                                  |

| Solar       | CSP     |                  |                   |                                | Α                                 | Е                                |

| Solar       | PQFN    |                  |                   |                                | В                                 |                                  |

| Motor       | CSP     | D                | С                 | F                              | А                                 | Е                                |

| Drives      | PQFN    | D                | С                 | F                              | В                                 | E                                |

Table 1: GaN primary wear-out mechanism and means of avoidance by application and device type. For the meaning of notes A through F, see Table 2.

CSP = chip scale packaged devices PQFN = power quad flat no-lead devices

| Note General Mitigation Strategy                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Choose suitable underfill                                                                                               | 3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Design an assembly process that leads to a part which lays flat and adheres well to the PCB                             | Appendix                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Remain within datasheet $V_{DS}$ limits, with excursions that remain within drain overvoltage specification             | 3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Remain within datasheet V <sub>GS</sub> limits,<br>with excursions that remain within gate<br>overvoltage specification | 3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Adhere to recommended mechanical specifications during assembly and handling                                            | 3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Adhere to Safe Operating Area specifications                                                                            | 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                                                                                                                         | Choose suitable underfill  Design an assembly process that leads to a part which lays flat and adheres well to the PCB  Remain within datasheet V <sub>DS</sub> limits, with excursions that remain within drain overvoltage specification  Remain within datasheet V <sub>GS</sub> limits, with excursions that remain within gate overvoltage specification  Adhere to recommended mechanical specifications during assembly and handling  Adhere to Safe Operating Area |  |  |

Table 2: GaN Reliability Concerns - Section References

# **TABLE OF CONTENTS**

|     |      | DN 1: DETERMINING WEAR-OUT MECHANISMS USING O-FAIL METHODOLOGY                   | ,   |

|-----|------|----------------------------------------------------------------------------------|-----|

|     |      | DN 2: USING TEST-TO-FAIL RESULTS TO PREDICT                                      | • - |

|     |      | E LIFETIME IN A SYSTEM                                                           | . 5 |

| SEC | TIC  | N 3: WEAR-OUT MECHANISMS                                                         | . 5 |

|     | 3.1  | Gate Wear-Out                                                                    |     |

|     |      | 3.1.1 Introduction to Gate Wear-Out Mechanisms                                   |     |

|     |      | 3.1.2. Gate Reliability Model                                                    | . 5 |

|     |      | 3.1.3. Summary of Physics-Based Gate Lifetime Model                              | . 6 |

|     |      | 3.1.4. Gate Overvoltage Study                                                    | . 6 |

|     | 3.2  | Drain Wear-Out                                                                   | . 7 |

|     |      | 3.2.1. Introduction to Drain Wear-Out Mechanisms                                 | . 7 |

|     |      | 3.2.2. Physics-Based Dynamic R <sub>DS(on)</sub> and Lifetime Models             | . 7 |

|     |      | 3.2.3. Effect of Switching Frequency and Switching Current                       | . 9 |

|     |      | 3.2.4. Impact of Higher Stress Voltages                                          | . 9 |

|     |      | 3.2.5. 200 V Model                                                               | 10  |

|     |      | 3.2.6. Drian Overvoltage Specification                                           | 11  |

|     |      | 3.2.7. Conclusions for Physics-Based Dynamic R <sub>DS(on)</sub> Model           | 13  |

|     | 3.3. | Current Density Wear-Out                                                         | 13  |

|     |      | 3.3.1. Introduction to Current Density Wear-out Mechanisms                       | 13  |

|     |      | 3.3.2. Safe Operating Area                                                       | 13  |

|     |      | 3.3.3. Short-Circuit Robustness Testing                                          | 14  |

|     |      | 3.3.4. Electromigration for copper interconnect                                  | 17  |

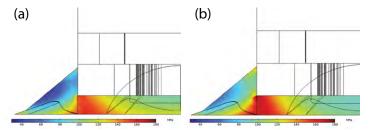

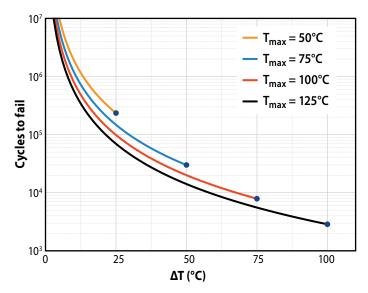

|     | 3.4  | Thermo-Mechanical Wear-Out                                                       | 19  |

|     |      | 3.4.1. Introduction to Thermo-Mechanical Wear-Out Mechanisms                     | 19  |

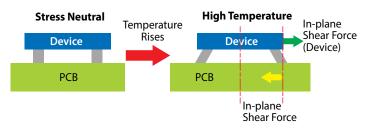

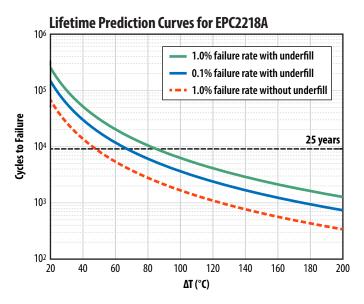

|     |      | 3.4.2. Impact of Die Size and Bump Shape on Temperature Cycling (TC) Reliability | 19  |

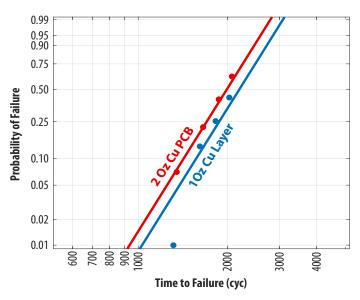

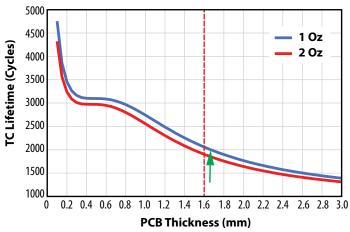

|     |      | 3.4.3. Effect of PCB Properties on Temperature Cycling Lifetime                  | 21  |

|     |      | 3.4.4. Criteria for Choosing a Suitable Underfill                                | 25  |

|     | 3.5. | Mechanical Stress Wear-Out                                                       | 27  |

|     |      | 3.5.1. Introduction to Mechanical Stress Wear-out Mechanisms                     | 27  |

|     |      | 3.5.2. Die Shear Test of Chip-Scale Parts                                        |     |

|     |      | 3.5.3. Backside Pressure Test of Chip-Scale Parts                                | 27  |

|     |      | 3.5.4. Bending Force Test of Chip-Scale Parts                                    | 28  |

|     |      | 3.5.5. Bending test on PQFN Parts                                                |     |

|     |      | ON 4: MISSION-SPECIFIC RELIABILITY PREDICTIONS                                   |     |

|     | 4.1. | Solar Application Specific Reliability                                           | 30  |

|     |      | 4.1.1. Introduction                                                              |     |

|     |      | 4.1.2. Trends In Photovoltaic Power Conversion                                   |     |

|     |      | 4.1.3. Applying Test-to-Fail for Solar                                           |     |

|     |      | 4.1.4. Gate Bias                                                                 |     |

|     |      | 4.1.5. Drain Bias                                                                |     |

|     |      | 4.1.6. Temperature Cycling                                                       |     |

|     |      | 4.1.7. Conclusions                                                               | 33  |

|    | 4.2. DC-DC Application Specific Reliability                               | 33 |

|----|---------------------------------------------------------------------------|----|

|    | 4.2.1. Introduction                                                       | 33 |

|    | 4.2.2. Test-to-Fail Methodology                                           | 33 |

|    | 4.2.3. Gate Bias                                                          | 33 |

|    | 4.2.4. Drain Bias                                                         | 33 |

|    | 4.2.5. Temperature Cycling                                                | 36 |

|    | 4.2.6. Conclusions                                                        | 36 |

|    | 4.3. Lidar Application Reliability                                        | 37 |

|    | 4.3.1. Introduction to Lidar Reliability                                  | 37 |

|    | 4.3.2. Long-Term Stability Under High Current Pulses                      | 37 |

|    | 4.3.3. Monolithic GaN-on-Si laser driver ICs                              | 38 |

|    | 4.3.4. Key Stressors of eToF Laser Driver IC for Lidar Application        | 38 |

|    | 4.3.5. Effect of V <sub>DD</sub> , Logic Supply Voltage                   | 38 |

|    | 4.3.6. Effect of V <sub>D</sub> , Laser Drive Voltage                     | 41 |

|    | 4.3.7. Effect of Operating Frequency                                      | 42 |

| 5. | SUMMARY AND CONCLUSIONS                                                   | 43 |

| 6. | Appendix                                                                  | 44 |

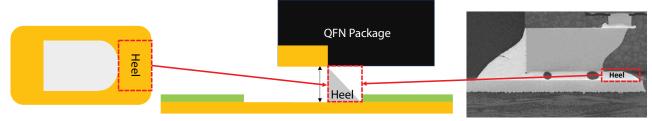

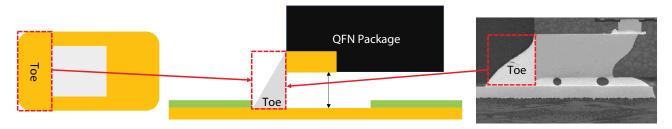

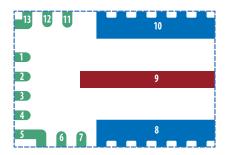

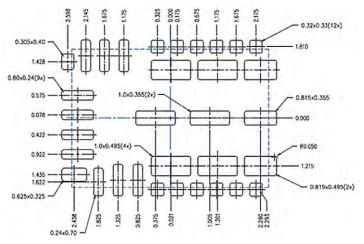

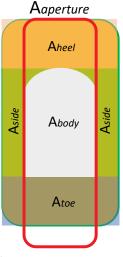

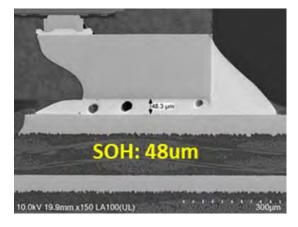

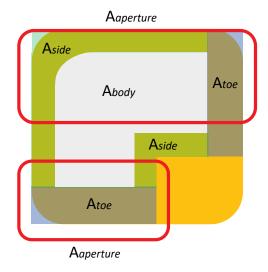

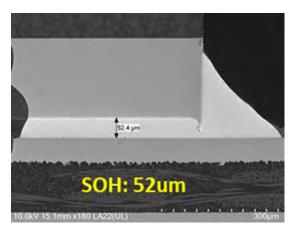

|    | Solder Stencil Design Rule for Reliable Assembly of PQFN Packaged Devices | 44 |

| DE | EEDENCES                                                                  | 51 |

# SECTION 1: DETERMINING WEAR-OUT MECHANISMS USING TEST-TO-FAIL METHODOLOGY

Standard qualification testing for semiconductors typically involves stressing devices at or near the limits specified in their datasheets for a prolonged period, or for a certain number of cycles. The goal of standard qualification testing is to have zero failures out of a relatively large group of parts tested.

This type of qualification testing is inadequate since it only reports parts that passed a very specific test condition. By testing parts to the point of failure, an understanding of the amount of margin between the datasheet limits can be developed, and more importantly, an understanding of the intrinsic failure mechanisms can be found. By knowing the intrinsic failure mechanisms, the root cause of failure, and the behavior of this mechanism over time, temperature, electrical or mechanical stress, the safe operating life of a product can be determined over a more general set of operating conditions (For an excellent description of test-to-fail methodology for testing semiconductor devices, see reference [2]).

As with all power transistors, the key stress conditions involve voltage, current, temperature, and humidity, as well as various mechanical stresses. There are, however, many ways of applying these stress conditions. For example, voltage stress on a GaN transistor can be applied from the gate terminal to the source terminal ( $V_{GS}$ ), as well as from the drain terminal to the source terminal ( $V_{DS}$ ). For example, these stresses can be applied continuously as a DC bias, they can be cycled on-and-off, or they can be applied as high-speed pulses. Current stress can be applied as a continuous DC current, or as a pulsed current. Thermal stresses can be applied continuously by operating devices at a predetermined temperature extreme for a period of time, or temperature can be cycled in a variety of ways.

By stressing devices with each of these conditions to the point of generating a significant number of failures, an understanding of the primary intrinsic failure mechanisms for the devices under test can be determined. To generate failures in a reasonable amount of time, the stress conditions typically need to significantly exceed the datasheet limits of the product. Care needs to be taken to make certain the excess stress condition does not induce a failure mechanism that would never be encountered during normal operation. To make certain that excess stress conditions did not cause the failure, the failed parts need to be carefully analyzed to determine the root cause of their failure. Only by verifying the root cause can a complete understanding of the behavior of a device under a wide range of stress conditions be developed. As the intrinsic failure modes in eGaN® devices are better understood, two facts have become clear; (1) eGaN devices are more robust than Si-based MOSFETs, and (2) silicon MOSFET intrinsic wearout models do not generally apply when predicting eGaN device lifetime under extreme or long-term electrical stress conditions.

Table 1-1 lists in the left-hand column all the various stressors to which a transistor can be subjected during assembly or operation.

Using the various test methods listed in the third column from the left, and taking devices to the point of failure, the intrinsic wear-out mechanisms can be discovered. The wear-out mechanisms confirmed as of this writing are shown in the column on the right.

| Stressor                   | Device/<br>Package                    | Test Method                     | Intrinsic Wear-out<br>Mechanism                         |  |

|----------------------------|---------------------------------------|---------------------------------|---------------------------------------------------------|--|

|                            |                                       | LITCD                           | Dielectric failure (TDDB)                               |  |

|                            |                                       | HTGB                            | Threshold shift                                         |  |

| Voltage                    | Device                                | HTRB                            | Threshold shift                                         |  |

|                            |                                       | ПІКО                            | R <sub>DS(on)</sub> shift                               |  |

|                            |                                       | ESD                             | Dielectric rupture                                      |  |

| Current                    | Device                                | DC Current (EM)                 | Electromigration                                        |  |

| Current                    | Device                                | De current (LIVI)               | Thermomigration                                         |  |

| Current + Voltage          | Device                                | SOA                             | Thermal Runaway                                         |  |

| (Power)                    | Device                                | Short Circuit                   | Thermal Runaway                                         |  |

| Voltage Rising/<br>Falling | Device                                | Hard-switching Reli-<br>ability | R <sub>DS(on)</sub> shift                               |  |

| Current Rising/<br>Falling | g/ Pulsed Current (Lidar reliability) |                                 | None found                                              |  |

| Temperature                | Package                               | HTS                             | None found                                              |  |

|                            |                                       | MSL1                            | None found                                              |  |

|                            |                                       | H3TRB                           | None found                                              |  |

| Humidity                   |                                       | None found                      |                                                         |  |

|                            |                                       | Solderability                   | Solder corrosion                                        |  |

|                            |                                       | uHAST                           | Denrite Formation/<br>Corrosion                         |  |

|                            |                                       | TC                              | Solder Fatigue                                          |  |

|                            |                                       | IOL                             | Solder Fatigue                                          |  |

| Mechanical /               |                                       | Bending Force Test              | Delamination                                            |  |

| Thermo-<br>mechanical      | Package                               | Bending Force Test              | Solder Strength                                         |  |

| mecnanicai                 |                                       | Bending Force Test              | Piezoelectric Effects                                   |  |

|                            |                                       | Die Shear                       | Solder Strength                                         |  |

|                            |                                       | Package Force                   | Film Cracking                                           |  |

|                            |                                       | Gamma Radiation                 | None found                                              |  |

| Dadietie-                  | Daviter                               | Neutron Radiation               | None found                                              |  |

| Radiation                  | Device                                | Heavy Ion<br>Bombardment (SEE)  | Crystal displacement<br>damage and ionization<br>damage |  |

Table 1-1: Stress conditions and intrinsic wear-out mechanisms for GaN transistors

# SECTION 2: USING TEST-TO-FAIL RESULTS TO PREDICT DEVICE LIFETIME IN A SYSTEM

When multiple failure mechanisms or stressors are involved, the total failure rate of a system, commonly known as Failure in Time (FIT), is the sum of the failure rates per failure mechanism [3,4] as shown below,

$$FIT_{Total} = FIT_1 + FIT_2 + \dots + FIT_i$$

Eq. 2-1

where FIT is failure in time, which typically represents the number of failures in 109 (1 billion) device hours, and the subscript indicates the different failure mechanisms identified.

FIT is inversely proportional to mean time to failure (MTTF) as described by

$$FIT = \frac{10^9}{MTTF}$$

Eq. 2-2

Therefore, by plugging Equation 2-2 into Equation 2-1, the total MTTF can be described by Equation 2-3,

$$\frac{1}{MTTF_{Total}} = \frac{1}{MTTF_1} + \frac{1}{MTTF_2} + \dots + \frac{1}{MTTF_i}$$

Eq. 2-3

The subscripts are assigned to the reliability stressors that are relevant to the application of interest. Based on Equation 2-3, it is noted that the smallest denominator yields the smallest MTTF and therefore dominates the overall lifetime. It is critical to understand which stressor is the limiting factor in reliability because the weakest link warrants the most consideration during design and operations.

In most applications, devices experience various stress conditions over the course of the entire mission lifespan, including a combination of different bias conditions and different temperature profiles. Each stress condition corresponds to a specific failure rate (failures per unit time), specified as FRa, FRb, ..., FRn. The respective duration of each stress condition is denoted as ta, tb, ..., tn. Assuming t\_total=t\_a+t\_b+... +t\_n is 10<sup>9</sup> hours, the FIT calculation of total number of failures is then generalized for specific reliability stress conditions as

$$FIT = FR_a \cdot t_a + FR_b \cdot t_b + \dots + FR_n \cdot t_n$$

Eq. 2-4

The time-averaged failure rate FR can be calculated as

$$FR = FR_a \frac{t_a}{t_{total}} + FR_b \frac{t_b}{t_{total}} + \dots + FR_n \frac{t_n}{t_{total}}$$

Eq. 2-5

which can be simplified by introducing fractional operation time,

$$i = \frac{t_i}{t_{total}}$$

Eq. 2-6

noted as a, b, ..., n. The sum of a, b, ..., n is 100% which is given in Equation 2-7.

$$a + b + \dots + n = 100\%$$

Now Equation 2-5 can be simplified to

$$FR = FR_a \cdot a + FR_b \cdot b + \dots + FR_n \cdot n$$

Eq. 2-8

It is known that the failure rate under each sub-stress condition is inversely proportional to the device lifetime LT [4] when the same number of failures is generated. The relation is shown in Equation 2-9.

$$FR \propto \frac{1}{LT}$$

Eq. 2-9

Plugging Equation 2-9 into Equation 2-8 yields Equation 2-10.

$$\frac{1}{LT_{Total}} = \frac{a}{LT_a} + \frac{b}{LT_b} + \dots + \frac{n}{LT_n}$$

Eq. 2-10

where LT<sub>Total</sub> is the total projected lifetime and LT<sub>i</sub> is the projected lifetime for each stress condition.

Equation 2-10 captures how a mission profile consisting of more than one stress condition results in a system lifetime. The fractional operation time (a, b, ..., n) in the numerators account for the times spent in harsh, moderate, and mild stress conditions.

## **SECTION 3: WEAR-OUT MECHANISMS**

## 3.1. Gate Wear-Out

#### 3.1.1. Introduction to Gate Wear-Out Mechanisms

GaN transistors devices require a 5 V<sub>GS</sub> to properly drive the devices, which leaves a small margin from the nominal bus voltage (~5 V) to the datasheet maximum specification (V<sub>GS/Max</sub> = 6 V). Virtually zero (less than one part per million) failure rate is expected if the gate bias is kept less than 6 V<sub>GS,Max</sub> during the entire mission lifespan of 10–25 years. If the transient overvoltage rings beyond 6  $V_{GS}$ , a 1% duty cycle-based overvoltage specification is supported by data and a method to project the lifetime due to gate overvoltage is developed.

#### 3.1.2. Gate Reliability Model

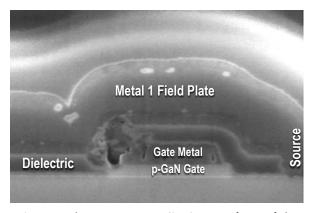

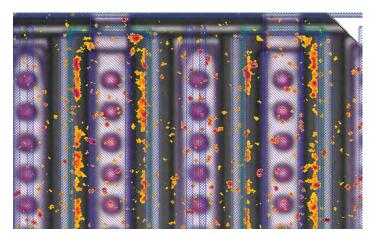

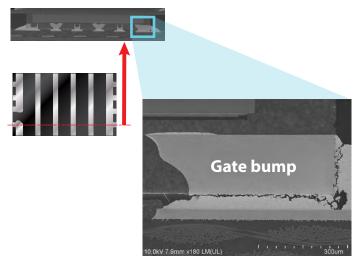

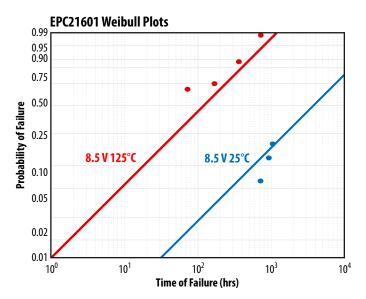

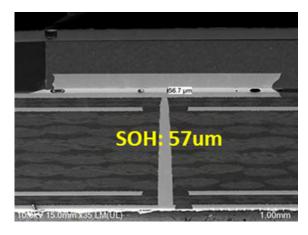

To understand gate wear-out mechanisms, four groups of representative GaN HEMTs (EPC2212) and 32 devices per group were tested under four different accelerated stress conditions, where the bias voltages of 8 V, 8.5 V, 9 V, and 9.5 V well exceeded the max rated gate voltage (V<sub>GS(max)</sub>) of 6 V. At 9 V and 9.5 V, failures occurred very quickly, but it took significantly longer at 8 V and 8.5 V. After the failures were identified, failure analyses were conducted on a large number of failures at all test voltages, and a consistent failure mode was found. Fig. 3-1 shows the failure mode observed in all failures analyzed. The location of the gate failures is where the silicon nitride dielectric is sandwiched between gate metal and field plate metal.

Fig. 3-1. Scanning electron microscopy (SEM) image of a gate failure. Dielectric breakdown is observed between the gate metal and the field plate metal.

To explain all the observations found via failure analysis, an impact ionization model was introduced and developed in a two-step process [1, 5]. Having identified impact ionization as the mechanism responsible for gate wearout led to the development of the following lifetime model applicable to p-GaN gates [5].

$$MTTF = \frac{Q_{c}}{G} = \frac{qQ_{c}}{\alpha_{n}J_{n}} = \frac{A}{(1-c\Delta T)} exp\left[\left(\frac{B}{V+V_{0}}\right)^{m}\right]$$

Eq. 3-1

with parameters listed below:

m = 1.9 $V_0 = 1.0 \text{ V}$ B = 57.0 V $A = 1.7 \times 10^{-6} \text{ s}$  $c = 6.5 \times 10^{-3} \, \text{K}^{-1}$

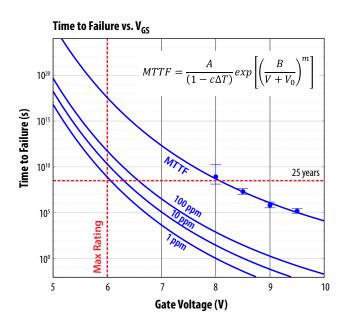

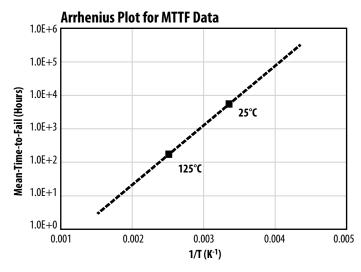

The lifetime equation (Equation 3-1) is plotted against measured acceleration data for EPC2212 in Figure 3-2. To produce this fit, all parameters in Equation 3-1 were fixed except A and B. The resulting best fit for B, (when converted into a field by dividing by the gate thickness), resulted in a value of 7.6 x 10<sup>6</sup> V/cm, in very close agreement with Ooi's value of 7.2 x 10<sup>6</sup> V/cm [6].

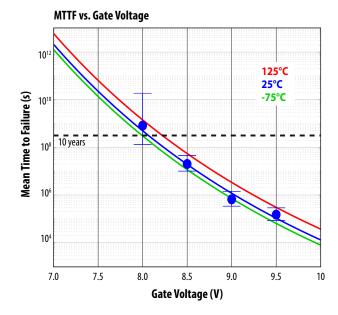

Figure 3-3 shows the temperature dependence of the lifetime equation at -75°C, 25°C, and 125°C. The temperature dependence (contained in the parameter c) is taken directly from Ozbek [7] without fitting to data. Note that at higher temperature, the MTTF is slightly higher than at lower temperatures, which, although counter-intuitive, is consistent with the measured data reported in the Phase 14 report [5].

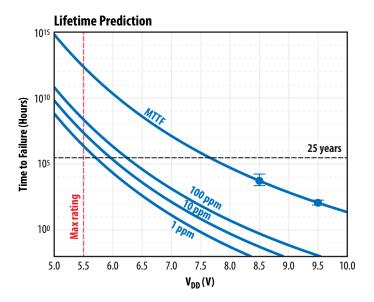

Figure 3-2: EPC2212 MTTF vs. V<sub>GS</sub> at 25°C (and error bars) are shown for four different voltage legs. The solid line corresponds to the impact ionization lifetime model. Extrapolations of time to failure for 100 ppm, 10 ppm, and 1 ppm are shown as well.

Figure 3-3: MTTF for EPC2212 (25°C) measured at four different gate biases. Blue line is the lifetime model. Red and green lines are predictions of the lifetime model at 125°C and -75°C, respectively.

# 3.1.3. Summary of Physics-Based Gate Lifetime Model

The impact ionization model of gate lifetime in GaN transistors (Equation 3-1) successfully accounts for a host of observed factors:

- Positive temperature coefficient of MTTF (which is unusual in semiconductor physics of failure).

- Very high acceleration with gate bias, and acceleration that is steeper than exponential at decreasing gate bias.

- Dielectric rupture through a high quality Si<sub>3</sub>N<sub>4</sub> film at a field strength well below breakdown (as a result of hole injection and trapping from the adjacent pGaN region).

This lifetime equation is not simply borrowed from the body of standard reliability models developed for MOSFETs. Instead, it represents the first gate lifetime model, built up from the root physics of failure, specifically applicable to enhancement mode GaN transistors.

## 3.1.4. Gate Overvoltage Study

Gate overvoltage spikes during device turn-on transients are commonly observed in gallium nitride high electron mobility transistors (GaN HEMTs) under high-frequency, fast-switching conversion applications [8]. The magnitude of the gate overvoltage transients is primarily governed by the gate-loop inductance and the slew rate (V<sub>GS</sub>/dt) which both are closely related to circuit design and PCB layout [10]. Therefore, it is critical to understand the gate overvoltage capability of GaN HEMTs as well as the associated lifetimes under various overvoltage stresses.

The projected lifetime results offer assurance that the failure rate is expected to be less than 1 part per million (ppm) for 25 years if the gate was biased less than the datasheet maximum limit at 6 V<sub>GS,Max</sub>. This virtually zero failure rate is also consistent with EPC's field experience, where no gate failures have ever been identified despite very demanding applications in automotive, satellites, and advanced enterprise servers. This projected extremely low failure rate helps build confidence in overall gate reliability but does not provide a methodology to accurately estimate the overall lifetime when gate overvoltage spikes are present repetitively during switching.

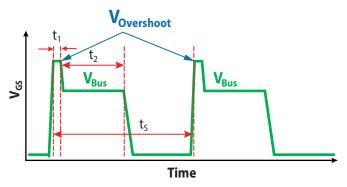

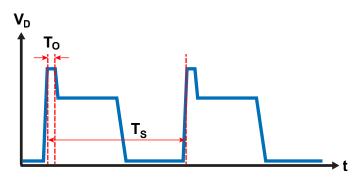

In real-world applications, the common mission profile can be simplified and illustrated by Figure 3-4 [8,12]. Within each switching period (t<sub>s</sub>), it mainly includes two portions which are labeled as overvoltage duration, t1, and bus voltage duration, t2.

Figure 3-4: An illustration of a normal gate switching waveform in real-world applications.  $t_1$  is the duration of gate overshoot in each period and  $t_2$  is the nominal bus voltage bias duration within each switching period.  $t_s$  is the switching period that is dependent on the switching frequency.

By following the mathematical approach introduced in Section 2 using the durations shown Figure 3-4, Equation 3-2 is developed to estimate total lifetime by accounting for gate overshoot period and normal bus voltage period.

$$\frac{1}{T_{Total}} = \frac{a}{T_{VG_{Overshoot}}} + \frac{b}{T_{VG_{Bus}}}$$

Eq. 3-2

Another term, overshoot duty cycle, is introduced in Equation 3-3, where DC<sub>overshoot</sub> is the ratio between t1, gate overvoltage duration within each switching period, and the switching period,  $t_\varsigma$  that is inversely proportional to the switching frequency.

$$DC_{overshoot} = \frac{t_1}{t_s}$$

Eq. 3-3

To further demonstrate the model of Equations 3-2 and 3-3, two examples are provided in the following discussion, based on the data presented in Section 3.1.2. Assume the nominal bus voltage for EPC2212 is 5.5 V. The overvoltage is estimated to be 120% of the nominal bus voltage, which is calculated to be 6.6 V ( $V_{GS,Max} = 6 \text{ V}$ ). The overshoot duty cycle is expected to be approximately 1% as defined by Equation 3-3 and Figure 3-4.

To simplify the calculation, it is assumed that the gate is operating 99% of the time at 5.5 V although there should always be another duty cycle involved in real applications. Therefore, adding the impact of the overshoot to the nominal drive condition, the EPC2212 GaN device lifetime is projected to be 1.64 x 10<sup>9</sup> seconds, or 51 years, for a 10 ppm failure rate (10 device failures per 1 million tested).

In another example, the GaN devices are used in a poorly designed circuit where the gate terminal sees a 7 V gate voltage spike during turn-on transient repetitively with the same 1% overshoot duty cycle. In this extreme example the bus voltage is still at 5.5 V for 99% of the time. After approximately 16 years, the failure rate is still expected to be only 100 ppm.

The test-to-fail approach was applied to GaN devices to investigate the gate reliability beyond the maximum datasheet limit. This work provides a comprehensive lifetime equation to account for the respective lifetimes under various gate bias conditions including overvoltage stress condition and nominal bus voltage bias condition. The projected lifetime based on 1% of gate overshoot duty cycle at 120% of  $V_{\text{Bus}}$  is expected to significantly exceed 25 years at a failure rate of 10 ppm. This result demonstrates excellent gate overvoltage reliability.

### 3.2 Drain Wear-Out

#### 3.2.1 Introduction to Drain Wear-Out Mechanisms

The same test-to-fail methodology is adapted to investigate drainrelated wear-out mechanism. One of the more common concerns among GaN transistor users is dynamic on-resistance, especially if their experiences are based on older generation products from various suppliers. This is a condition whereby the on-resistance of a transistor increases when the device is exposed to high drain-source voltage (V<sub>DS</sub>). The dominant wear-out mechanism in GaN is uncovered and modeled from first principles, leading to a comprehensive lifetime equation to project dynamic R<sub>DS(on)</sub> shift with respect to various parameters, including voltage, temperature, frequency, and current etc. When overvoltage spikes are observed during switching applications, another duty cyclebased overvoltage specification is developed.

## 3.2.2 Physics-Based Dynamic R<sub>DS(on)</sub> and Lifetime Models

As shown in the Phase 15 report [1], the dominant mechanism causing on-resistance to increase is the trapping of electrons near the drain electrode. As the trapped charge accumulates, it depletes electrons from the two-dimensional electron gas (2DEG) in the ON state, leading to an increase in R<sub>DS(on)</sub>.

Figure 3-5 is a magnified image of an EPC2016C GaN transistor showing thermal emissions in the 1-2 µm optical range. Emissions in this part of the spectrum are consistent with hot electrons and their location in the device is consistent with the location of the highest electric fields when the device is under drain-source bias.

Figure 3-5: A magnified image of an EPC2016C GaN transistor showing light emission in the 1–2  $\mu$ m wavelength short-wave infrared light range (SWIR) that is consistent with hot electrons. The SWIR emission (red-orange) has been overlaid on a regular (visible wavelength) microscope image and a semi-transparent image of the design photomask (purple).

Knowing that hot electrons in this region of the device are the source of trapped electrons, a better understanding of how to minimize the dynamic on-resistance can be achieved with improved designs and processes. By understanding the general behavior of hot electrons, their behavior over a wider range of stress conditions can be generalized.

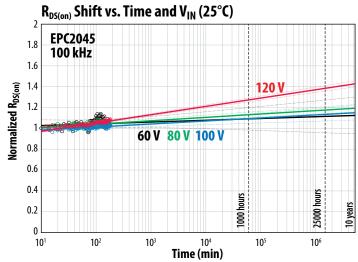

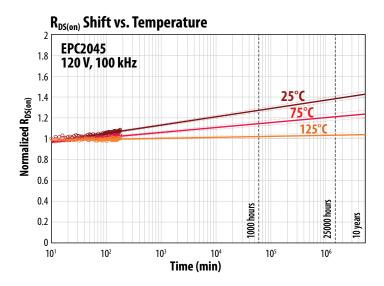

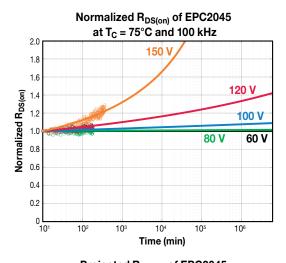

Figure 3-6 shows how the R<sub>DS(on)</sub> of a fifth generation EPC2045 GaN transistor [13], designed with the knowledge that hot electron trapping is accelerated with peak electric fields near the drain, increases over time at various voltage stress levels and temperatures. On the top graph, the devices were tested at 25°C, at voltages from 60 V to 120 V (EPC2045 has a  $V_{DS(max)}$  of 100 V). The horizontal axis shows time measured in minutes, with the right side ending at 10 years. The graph on the bottom shows the evolution of R<sub>DS(on)</sub> when biased at 120 V at different temperatures. The counter-intuitive result shows that the on-resistance increases faster at lower temperatures. This is consistent with hot-carrier injection because hot electrons travel further between scattering events at lower temperatures and therefore are accelerated to greater kinetic energies by a given electric field. The result is that the electrons scatter further with higher energies, reaching layers where they are more likely to become trapped. This suggests that traditional testing methods, where a device is tested at maximum voltage and temperature, may not be enough to determine the reliability of a device.

In the original publication of the results [5,9,14], the MTTF was found to be longer at 90°C than at either 35°C or 150°C, which was a mystery at the time. The results now can be better understood. As the device is heated under DC bias, the leakage current increases. However, the shorter mean free path of the hot carriers outweighs

Figure 3-6: The  $R_{DS(on)}$  of a fifth generation EPC2045 GaN transistor over time at various voltage stress levels and temperatures. On the left, the devices were tested at 25°C with voltages from 60 V to 120 V. The graph on the right shows the evolution of  $R_{DS(on)}$  at 120 V at various temperatures.

the increase in available electrons such that the rate of  $R_{DS(on)}$  increase falls from room temperature to 90°C. At temperatures above 90°C, leakage continues to grow and the rate of  $R_{DS(on)}$  increase rises slightly.

When the applied drain bias is no greater than 120% of the  $V_{DS,Max}$ , indicating the trapped charge density is significantly smaller than the 2DEG carrier concentration, the model for  $R_{DS(on)}$  growth is shown in Equation 3-4.

Eq. 3-4

$$\frac{\Delta R}{R} = a + b \log \left(1 + \exp\left(\frac{V_{DS} - V_{FD}}{\alpha}\right)\right) \sqrt{T} \exp\left(\frac{\hbar \omega_{LO}}{kT}\right) \log(t)$$

#### **Independent Variables:**

$V_{DS}$  = Drain voltage (V)

T = Device temperature (K)

t = Time (min)

#### **Parameters:**

a = 0.00 (unitless)

$b = 2.0E-5 (K^{-1/2})$

$\hbar\omega_{L0}$  = 92 meV

$V_{FD}$  = 100 V (appropriate for Gen5 100 V products only)

$\alpha = 10 (V)$

k = Boltzmann constant = 0.0862 meV/K

Many customers require lifetime estimates under specific use conditions to fulfill certain quality or reliability requirements. By defining the lifetime (under hard-switching conditions) as the time <t> at which  $R_{DS(on)}$  will rise 20% from its initial value, Equation 3-4 can be inverted in a straightforward manner to obtain the time to failure

$$\langle t \rangle = \exp \left[ \frac{(0.2-a)}{b \log \left( 1 + \exp \left( \frac{V_{DS} - V_{FD}}{a} \right) \right) \sqrt{T} \exp \left( \frac{\hbar \omega_{LO}}{kT} \right)} \right] (\min) \quad \text{Eq. 3-5}$$

This equation gives the expected MTTF under hard-switching conditions as a function of operating voltage and temperature. Typically, worst case values (highest voltage, lowest temperature) are used to provide a lower bound. As before, the lifetime will be in units of minutes. Other definitions of lifetime can be applied and extracted from Equation 3-4 as well.

#### 3.2.3. Effect of Switching Frequency and Switching Current

In the analysis so far, the effects of switching frequency (f) and switch current (I) on the  $R_{DS(on)}$  growth characteristics have been ignored. The current directly impacts the number of electrons injected into the high field region during the hard-switching transition, and therefore has a linear effect on the hot carrier density. Likewise, the switching frequency determines the number of hot carrier pulses seen at the drain in a given time interval, and therefore also has a linear effect on the surface trapping rate.

By assuming that the surface trapping rate is linearly proportional to both frequency (f) and current (I), the effects of f and I are included in Equation 3-6, where a simple scaling term is derived to relate the  $R_{DS(on)}$  growth in one switching condition ( $f_1$ ,  $I_1$ ) to another ( $f_2$ ,  $I_2$ ).

$$R(t; f_2, I_2) = R(t; f_1, I_1) + b \left( \log \left( \frac{f_2}{f_1} \right) + \log \left( \frac{I_2}{I_1} \right) \right)$$

Eq. 3-6

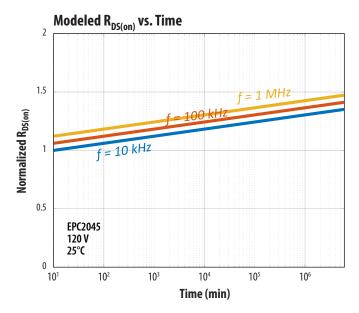

Mathematically, the effect of changing the switching frequency or current is to simply offset the  $R_{DS(on)}$  growth curve vertically by a small amount. The offset depends on the logarithm of f and I,

and therefore has a fundamentally weak dependence on these variables. Furthermore, the offset depends on the overall slope b of the log(t) growth characteristic. Therefore, if the FET is operated under conditions with low R<sub>DS(on)</sub> rise (low slope b), the effect of changing frequency or current will be negligible.

Figure 3-7: Modeled  $R_{DS(on)}$  vs. Time at three different switching frequencies, covering two orders of magnitude. Note that the effect of frequency change is a small vertical offset in the growth characteristic. The same offset would occur at different switch currents.

I, and therefore has a fundamentally weak dependence on these variables. Furthermore, the offset depends on the overall slope b of the log(t) growth characteristic. Therefore, if the FET is operated under conditions with low R<sub>DS(on)</sub> rise (low slope b), the effect of changing frequency or current will be negligible.

Figure 3-7 compares the modeled  $R_{DS(on)}$  vs. time for an EPC2045 at three different switching frequencies, from 10 kHz to 1 MHz. Note that the curves are simply offset from each other vertically. The same would be true had we compared different switch currents. Because the offset changes as the logarithm of f (or I), even a 10x increase in switching frequency (or current) would be difficult to observe experimentally owing to  $\pm 10\%$  noise in the measurement and projection.

# 3.2.4. Impact of Higher Stress Voltages

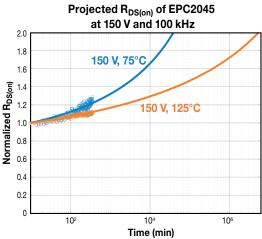

In the case where the amount of trapped charge approaches the number of electrons available in the 2DEG (the surface trapped charges ( $Q_S$ ) approaches the built-in 2DEG piezoelectric charge ( $Q_P$ )), the simplifying assumption used to develop Equation 3-4 is no longer valid. This situation could occur when devices are taken to voltages well above their design limits. Figure 3-8 shows results for EPC2045 devices tested up to 150 V at 75°C and 125°C. Note how the straight-line extrapolation that would occur with a simple log(time) dependence is no longer applicable. By removing the simplified assumption that only a small fraction of  $Q_P$  is trapped and transform into  $Q_S$ , the result shown in Equation 3-7 is obtained.

Calculating Equation 3-7 using the expanded list of parameters yields the solid lines in Figure 3-8, providing further evidence of the validity and applicability of this physics-based model.

$$\frac{\Delta R}{R} = a_1 \left[ \frac{a_2 \Psi log \left( 1 + a_3 t/\Psi \right)}{1 - a_2 \Psi log \left( 1 + a_3 t/\Psi \right)} \right]$$

where:

$$a_1 \equiv \frac{C}{Q_p}$$

$a_2 \equiv \frac{1}{Q_p}$   $a_3 \equiv B$  Eq. 3-7

with the following expanded list of parameters:

$a_1 = 0.6$  (unitless)

$a_2 = b/a_1$  (where  $b = 2.0E-5 K^{-1/2}$  from [5,9])

$a_3 = 1000 (K^{1/2} min^{-1})$

$b = 2.0E-5 (K^{-1/2})$

$\hbar\omega_{L0}\,{=}\,92\;meV$

V<sub>FD</sub> = 100 V (appropriate for Gen5 100 V products only)

$\alpha = 10 (V)$

T = Device temperature (K)

t = Time (min)

Figure 3-8: 100 V EPC2045 devices in hard-switching circuit at various voltages up to 150% of design rating (top), and at two different temperatures, also at 150% of design rating (bottom). The solid lines are the model predictions, and the dots represent measurement points.

#### 3.2.5 200 V Model

A similar analysis was developed for 200 V GaN transistors. The resultant variables are as follows:

$a_1 = 0.6$  (unitless)

$a_2 = 2.8 \cdot b/a_1$  (where  $b = 2.0E-5 \text{ K}^{-1/2} \text{ from [7]})$

$a_3 = 1000 (K^{1/2} min^{-1})$

$b = 2.0E-5 (K^{-1/2})$

$\hbar\omega_{L0}$  = 92 meV

$V_{FD}$  = 210 V (appropriate for Gen5 200 V products only)

$\alpha$  = 25 (V) (appropriate for Gen5 200 V products only)

T = Device temperature (K)

t = Time (min)

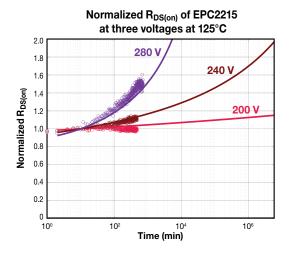

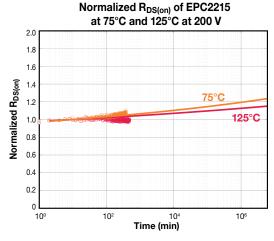

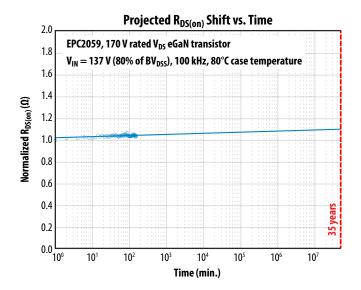

Figure 3-9 compares this model to measurements of 200 V devices. On the left is the normalized  $R_{DS(on)}$  for the fifth-generation, 200 V rated EPC2215 at three voltages. The highest voltage, 280 V, is 40% above the maximum rating. On the right are measurements compared with the model at two different temperature and the maximum rated voltage.

Figure 3-9: (Top) 200 V EPC2215 normalized  $R_{DS(on)}$  at three voltages. Note that 280 V is 40% above the maximum rated voltage. (Bottom) EPC2215 at 75°C and 125°C and 200 V. The solid lines are the model results using variables for 200 V devices, and the dots are actual measurements.

# 3.2.6. Drain Overvoltage Specification

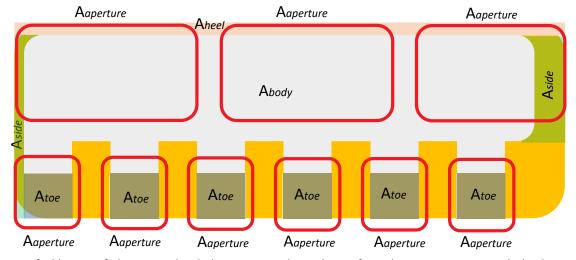

Transient drain voltage overshoot is commonly observed in gallium nitride-based converters due to high slew rate and fast switching applications. A survey of transient overvoltage specification from a suite of GaN suppliers was conducted by JEDEC JC-70 committee and presented in JEP186 [15]. Most of the transient overvoltage specifications describe it as a device robustness indicator. In addition, many of them consider drain voltage overshoot as a single rare event or atypical occurrence. Hence, it is challenging for application engineers to effectively implement these specifications into their designs. Therefore, an application driven, and user-friendly repetitive transient off-state drain overvoltage specification on datasheets is important for the general adoption of GaN technology because of the absence of avalanche mechanisms in GaN HEMTs.

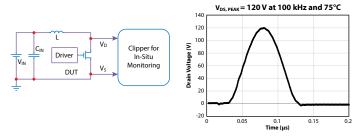

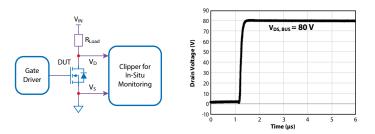

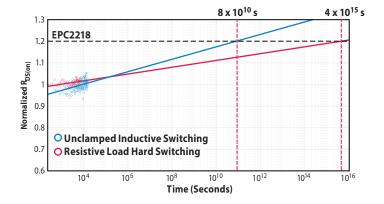

A resistive-load hard switching system (also known as "fast dR")  $[1,5,9,14] was deployed to study dynamic R_{DS(on)} shift under cumulative \\$ drain overshoot stress, where this system operates at 100 kHz, 85% of the time reverse-biasing the GaN device under test (DUT) at the specified off-state drain voltage. When determining time of failure, 20% of  $R_{DS(on)}$  shift compared to the initial  $R_{DS(on)}$  value after a projected 25 years of stress is used as the failure criteria. Equation 3-4 is used to extrapolate the time-of-failure when the in-situ monitored R<sub>DS(on)</sub> shifts more than 20% to its initial value ( $R_0$ ). This approach is more stringent than the typical datasheet maximum R<sub>DS(on)</sub> limit.

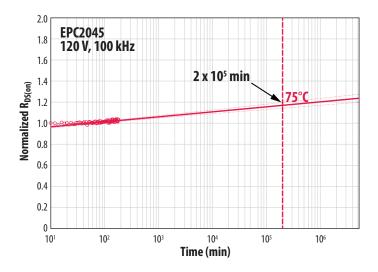

A suite of 100 V fifth generation GaN products were tested by the fast dR system at 120% of  $V_{DS,Max}$  (120 V) and 75°C junction temperature, a common mission temperature. EPC2045 was the first 100 V rated GaN product that was launched from the fifthgeneration 100 V product family. EPC2045 was first subjected to testing under such accelerated conditions. Figure 3-10 shows the testing results, where the DUT is projected to exceed the 20% R<sub>DS(on)</sub> shift limit at approximately 2 x 10<sup>5</sup> minutes by considering a 90% upper bound confidence level. Lifetime extrapolation is based upon the logarithmic time relation.

By multiplying by 85%, it yields 1.7 x 10<sup>5</sup> minutes, representing the total lifetime when the DUT is off-state biased continuously under 120 V and 75°C. When comparing with 25 years of expected overall lifetime, equivalent of 1.3 x 10<sup>7</sup> minutes, 1.7 x 10<sup>5</sup> minutes translates to approximately 1.3% of total lifespan. To add more margin, we rounded to 1% of 25 years. Now a total lifetime-based overvoltage specification of 1.3 x 10<sup>5</sup> minutes is developed.

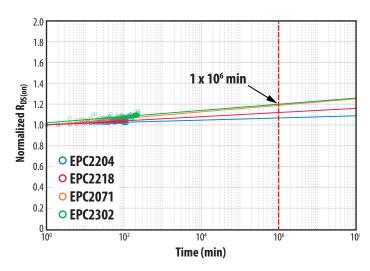

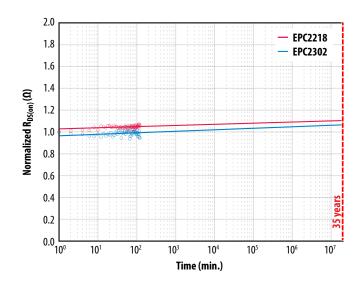

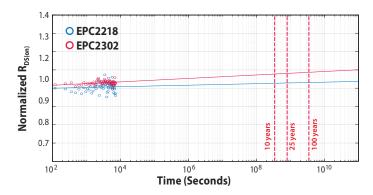

To further validate this total time-based specification, the same testing conditions were applied to newer 100 V rated GaN products including EPC2218, EPC2071, EPC2302, and EPC2204. Figure 3-11 summarizes the testing results of the listed products, where they are all projected to outperform the 1.3 x 10<sup>5</sup> minutes of lifetime.

Figure 3-10: Evolution of R<sub>DS(on)</sub> of a representative EPC2045 device, a fifth-generation 100 V rated GaN transistor, tested at 120 V and 75°C. It is projected to exceed 20% R<sub>DS(on)</sub> shift at 2 x 10<sup>5</sup> minutes by considering 90% of upper bound confidence level.

Figure 3-11: Evolution of R<sub>DS(on)</sub> of representative EPC2204, EPC2218, EPC2071, and EPC2302 GaN transistors, rated at 100 V and tested at 120 V and 75°C. They are projected to have less than 20% R<sub>DS(on)</sub> shift at a minimum of 1 x 10<sup>6</sup> minutes, significantly exceeding the 2 x  $10^5$  minutes lifetime based on EPC2045.

This total time-based specification can be scaled to a shorter duration that occurs repetitively within each switching cycle. Therefore, another way to specify this repetitive rating is to calculate the ratio of overvoltage duration of each cycle over the switching period, which is the 1% scaling factor that was initially discussed. This is equivalent to calculating the duty cycle of the overvoltage spike.

For instance, if a converter operates at 100 kHz, equivalent of 10 µs per switching period, it suggests that the GaN devices should withstand a repetitive 120 V overvoltage spike with a 100 ns duration in each switching cycle over 25 years of lifetime. This mathematical relation is demonstrated in Equation 3-8 and further illustrated in Figure 3-12.

Eq. 3-8  $Overshoot\ duty\ cycle = \frac{120\%\ Overvoltage\ Duration\ at\ 75^{\circ}C\ (T_{O})}{Switching\ Period\ (T_{S})} \leq 1\%$

where  $T_0$  is the overvoltage duration within each switching period and  $T_S$  is the switching period.

Figure 3-12: Illustration of the 1% overshoot duty cycle overvoltage specification. 1% is the ratio between  $T_{\rm O}$  (overvoltage duration) and TS (one switching period).

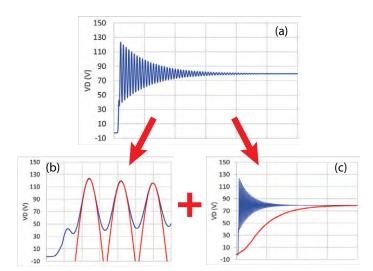

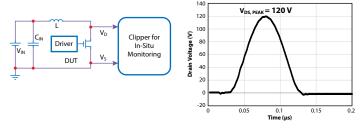

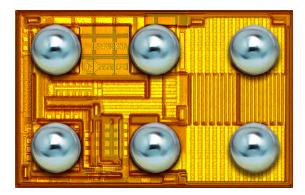

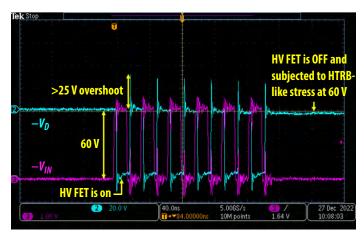

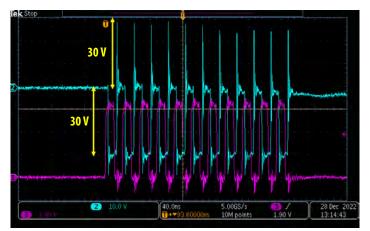

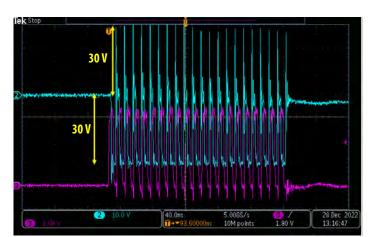

To verify this newly proposed overvoltage specification method, an unclamped inducive switching (UIS) circuit was developed [16,17]. Figure 3-13 shows the resulting overvoltage pulse that is generated by UIS.

Figure 3-13: Simplified schematic of the unclamped inductive switching circuit and the resulting overvoltage pulse with  $V_{DS-Peak}$  of 120 V under 100 kHz operating frequency.

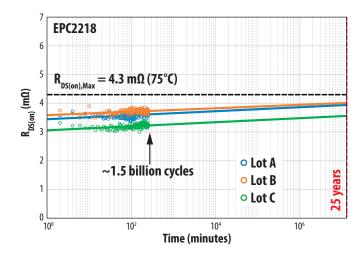

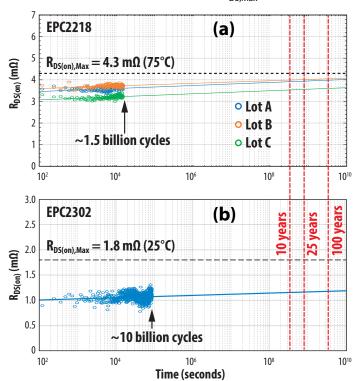

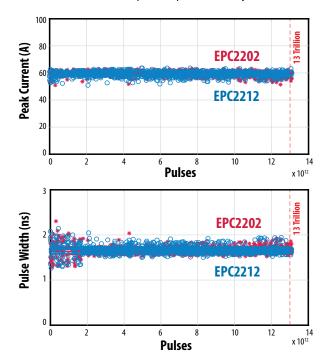

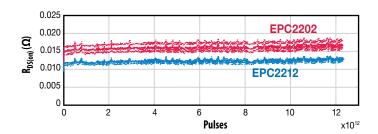

A number of 100 V rated GaN transistors from different wafer lots are stressed by a 120  $V_{DS/Peak}$  overvoltage spike at 100 kHz operation frequency and 75°C junction temperature. Figure 3-14 shows that representative EPC2218 devices from three different wafer lots were tested to billions of switching cycles showing very small dynamic  $R_{DS(on)}$  shift.

The same physics-based lifetime model based on hot carrier trapping was applied to project the lifetime under such drain overvoltage stresses. The projection demonstrates the excellent robustness of GaN devices under 120% overvoltage stress over long-term continuous operation. At each switching cycle, the

duration exceeding  $100 \text{ V}_{DS,Max}$  is approximately 25 ns, lower than the 120 V peak overshoot voltage. At the end of  $8 \times 10^8$  seconds (25 years), which equates to  $8 \times 10^{13}$  total pulses by multiplying with 100 kHz frequency, none of the DUTs surpassed the  $20\% \text{ R}_{DS(on)}$  shift failure criteria. Multiplying 25 ns by  $8 \times 10^{13}$  pulses gives  $2 \times 10^5$  minutes, which is close to the estimated total lifetime of  $1.3 \times 10^5$  minutes. The slight difference can be explained by the fact that the DUTs only reach the 120 V peak voltage for a very short portion of each pulse. The voltage waveform shown in Figure 3-13 is more representative of real time circuit applications.

Figure 3-14: Evolution of dynamic  $R_{DS(on)}$  of a representative EPC2218 DUTs from three different wafer lots under 120  $V_{DS,Peak}$  and 75°C UIS testing for more than 1.5 billion cycles.

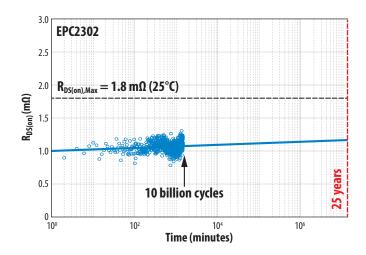

EPC2302, a representative power quad flat no-lead (PQFN) packaged 100 V rated GaN transistor was also tested in UIS at 120  $V_{DS,Peak}$  for more than 10 billion switching cycles. The projected lifetime showed extreme robustness of GaN devices under such overvoltage stress condition, shown in Figure 3-15. This further validates the proposed overvoltage specification.

Figure 3-15: Evolution of dynamic  $R_{DS(on)}$  of a representative EPC2302 DUT under 120  $V_{DSPeak}$  UIS testing for approximately 10 billion switching cycles.

A repetitive drain overvoltage specification is proposed and validated by resistive load hard switching and unclamped inductive switching testing circuits. This duty cycle-based specification offers a more quantitative and easy-to-implement quideline for application engineers to design GaN devices. This work also demonstrates the extreme overvoltage robustness of GaN HEMTs.

# 3.2.7. Conclusions for Physics-Based Dynamic R<sub>DS(on)</sub> Model

EPC has developed a first principles physics-based model to explain R<sub>DS(on)</sub> rise in GaN transistors under hard-switching conditions. The model is predicated on the assumption that hot electrons are injected over a surface potential into the conduction band of the surface dielectric. Once inside, the electrons guickly fall into deep mid-gap states, where they are assumed to be trapped permanently (no de-trapping). Hot electrons are created during the switching transition, where the transient combination of high injection current and high fields leads to a hot carrier energy distribution with long tails into the high energy regime.

This model predicts the following observations:

- Small R<sub>DS(on)</sub> growth with time

- The slope of R<sub>DS(on)</sub> over time has a negative temperature coefficient (i.e., lower slope as temperature rises).

- Switching frequency does not affect the slope but causes a small vertical offset.

- Switching current does not affect the slope.

The time dependence results from a rapidly self-quenching charge trapping dynamic that involves two intertwined effects: (1) a hot electron energy distribution that is exponential in energy; and (2) an accumulating surface charge Q<sub>S</sub> that steadily raises the barrier for electron injection into the dielectric [9]. The combination of these effects leads to a trapping rate that becomes exponentially slower as charge accumulates, leading to a slow time dependence. As the number of trapped charges approaches the number of available electrons in the 2DEG, the R<sub>DS(on)</sub> appears to climb faster than a straight log(time) dependence. The trapping mechanism, however, continues to follow a true log(time) dependence.

The negative temperature dependence results from the effect of LO-phonon scattering on the hot carrier energy distribution. At lower temperature, decreased scattering improves the mean free path, allowing electrons to gain higher energy in an electric field.

Key parameters in the mathematical model were fit to measured results for the EPC2045 across a range of drain voltages and temperatures. The model allows users to project long-term R<sub>DS(on)</sub> growth as a function of four key input variables: drain voltage, temperature, switching frequency, and switching current. The model was adapted to provide a simple MTTF equation, allowing users to predict lifetime under arbitrary conditions.

# 3.3. Current Density Wear-out

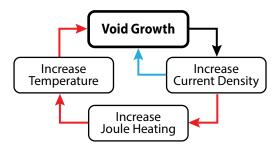

# 3.3.1. Introduction to Current Density Wear-out Mechanisms

Thermal limits can be of concern for GaN devices when high current and high drain-source voltage occur simultaneously. Extensive robustness testing was conducted, and the results verified the validity of safe operating area specified by the datasheet. For certain applications, the capability of withstanding short circuit fault conditions is a must. Therefore, short circuit testing was performed, where GaN demonstrated excellent robustness under such extreme stress conditions. When the devices are exposed to continuous high current at elevated temperatures, electromigration (EM) robustness becomes a frequently asked question by customers. Accelerated EM testing was conducted on power quad-flat no-leads (PQFN) devices, demonstrating excellent robustness against EM.

# 3.3.2. Safe Operating Area

Safe operating area (SOA) testing exposes the GaN transistor to simultaneous high current (ID) and high voltage (VDS) for a specified pulse duration. The primary purpose is to verify the transistor can be operated without failure at every point (I<sub>D</sub>, V<sub>DS</sub>) within the datasheet SOA graph. It is also used to probe the safety margins by testing to fail outside the safe zone. During SOA tests, the highpower dissipation within the die leads to a rapid rise in junction temperature and the formation of strong thermal gradients. For sufficiently high power or pulse duration, the device simply overheats and fails catastrophically. This is known as thermal overload failure.

In Si MOSFETs, another failure mechanism known as secondary breakdown (or Spirito effect [18]) has been observed in SOA testing. This failure mode, which occurs at high V<sub>D</sub> and low I<sub>D</sub>, is caused by unstable feedback between junction temperature and threshold  $V_{TH}$ . As the junction temperature rises during a pulse,  $V_{TH}$  drops, which can cause local current to rise. The rising current, in turn, causes temperature to rise faster, thereby completing a positive feedback loop that leads to thermal runaway and ultimate failure. A goal of this study is to determine if the Spirito effect exists in GaN transistors.

For DC, or long-duration pulses, the SOA capability of the transistor is highly dependent on the heatsinking of the device. This can present a huge technical challenge to assess the true SOA capability, often requiring specialty water-cooled heatsinks. However, for short pulses (< 1 ms), the heatsinking does not impact SOA performance. This is because on short timescales the heat generated in the junction does not have sufficient time to diffuse to any external heatsink. Instead, all the electrical power is converted to raising the temperature (thermal capacitance) of the GaN film and nearby silicon substrate. As a result of these considerations, SOA tests were conducted at two pulse durations: 1 ms and 100 µs.

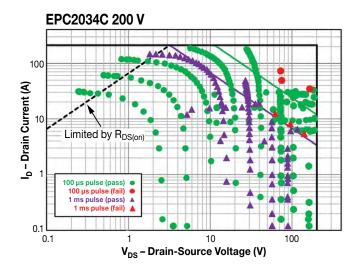

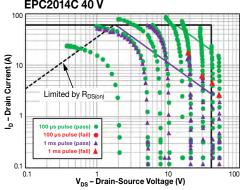

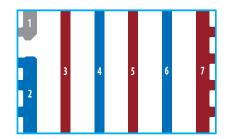

Figure 3-16 shows the SOA data of 200 V EPC2034C. In this plot, individual pulse tests are represented by points in ( $I_D$ ,  $V_{DS}$ ) space. These points are overlaid on the datasheet SOA graph. Data for both 100  $\mu$ s and 1 ms pulses data are shown together. Green dots correspond to 100  $\mu$ s pulses in which a part passed, whereas red dots indicate where a part failed. A broad area of the SOA was interrogated without any failures (all green dots), ranging from low  $V_{DS}$  all the way to  $V_{DSmax}$  (200 V). All failures (red dots) occurred outside the SOA, indicated by the green line in the datasheet graph. The same applies to 1 ms pulse data (purple and red triangles); all failures occurred outside of the datasheet SOA.

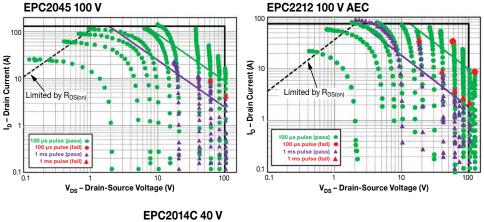

Figure 3-17 provides SOA data for three more parts, AEC EPC2212 (4th generation automotive 100 V), EPC2045 (5th generation 100 V), and EPC2014C (4th generation 40 V). In all cases, the datasheet safe operating area has been interrogated without failures, and all failures occur outside of SOA limits, often well outside the limits.

The datasheet SOA graph is generated with finite element analysis, using a thermal model of the device including all relevant layers along with their heat conductivity and heat capacity. Based on transient simulations, the SOA limits are determined by a simple criterion: for a given pulse duration, the power dissipation must be such that the junction temperature does not exceed 150°C before the end of the pulse. This criterion results in limits based on constant

power, denoted by the 45° green (100 µs) and purple (1 ms) lines in the SOA graph. This approach leads to a datasheet graph that defines a conservative safe operating zone, as evidenced by the extensive test data in this study. In power MOSFETs, the same constant power approach leads to an overestimate of capability in the high voltage regime, where failure occurs prematurely due to thermal instability (Spirito effect).

While the exact physics of failure is yet to be determined, the main outcome of this study is clear – GaN transistors will not fail when operated within their datasheet SOA.

#### 3.3.3. Short-Circuit Robustness Testing

Short circuit robustness refers to the ability of a FET to withstand unintentional fault conditions that may occur in an application while in the ON (conducting) state. In such an event, the device will experience the full bus voltage combined with a current that is limited only by the inherent saturation current of the transistor and the circuit parasitic resistance, which varies with the application and location of the fault. If the short-circuit state is not quenched by protection circuitry, the extreme power

Figure 3-16: EPC2034C SOA plot. The "Limited by  $R_{DS(on)}$ " line is based on datasheet maximum specification for  $R_{DS(on)}$  at 150°C. Measurements for 1 ms (purple triangles) and 100  $\mu$ s (green dots) pulses are shown together. Failures are denoted by red triangles (1 ms) or red dot (100  $\mu$ s). Note that all failures occur outside the datasheet SOA region.

Figure 3-17: SOA results for EPC2045, EPC2212, EPC2014C. Measurements for 1 ms (purple triangles) and 100 μs (green dots) pulses are shown together. Failures are denoted by red triangles.

dissipation will ultimately lead to thermal failure of the transistor. The goal of short-circuit testing is to quantify the "withstand time" the part can survive under these conditions.

Typical protection circuits (e.g., de-saturation protection for IGBT gate drivers) can detect and react to over-current conditions in 2–3 µs. It is therefore desirable if the GaN transistor can withstand unclamped short-circuit conditions for about 5 µs or longer.

The two main test circuits used for short-circuit robustness evaluation are described in [28]. They are:

- Hard-switched fault (HSF): gate is switched ON (and OFF) with drain voltage applied.

- Fault under load (FUL): drain voltage is switched ON while gate is ON.

For this study, devices were tested in both fault modes and no significant differences in the withstand time were found. Therefore, the focus will be on FUL results for the remainder of this discussion. However, it is important to note that from HSF testing, GaN transistors did not exhibit any latching or loss of gate control that can occur in silicon based IGBTs [69]. This result was expected given the lack of parasitic bipolar structures with the GaN devices. Until the time the transistors fail catastrophically, the short circuit can be fully quenched by switching the gate LOW, an advantageous feature for protection circuitry design.

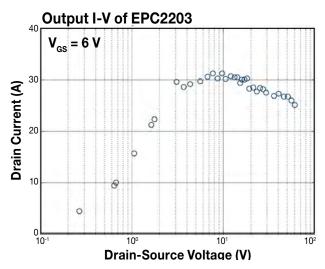

Two representative GaN transistors were tested:

- 1. EPC2203 (80 V): 4th generation automotive grade (AEC) device

- 2. EPC2051 (100 V): 5th generation device

These devices were chosen because they are the smallest in their product families. This simplified the testing owing to the high currents required for short-circuit evaluation. However, based on simple thermal scaling arguments, the withstand time is expected to be identical for other in-family devices. EPC2203 results cover EPC2202, EPC2206, EPC2201 and EPC2212; EPC2051 covers EPC2045 and EPC2053.

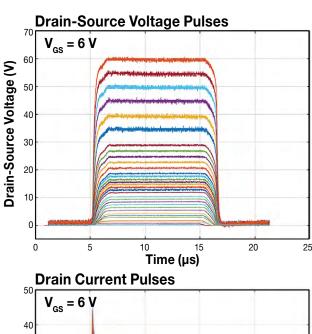

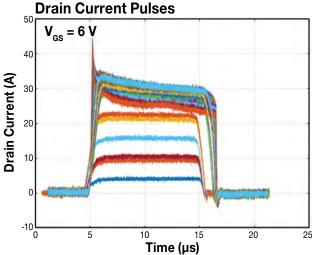

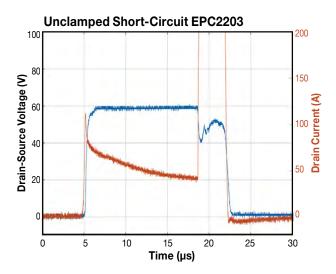

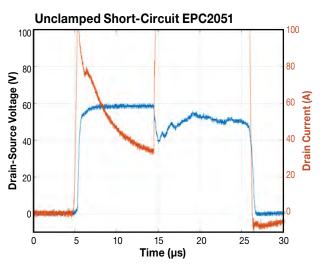

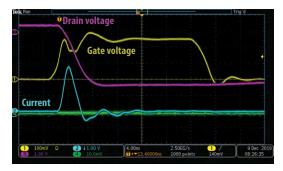

Figure 3-18 shows fault-under-load data on EPC2203 for a series of increasing drain voltages. With  $V_{GS}$  at 6 V (the datasheet maximum), and a 10  $\mu s$  drain pulse, the device did not fail all the way up to  $V_{DS}$  of 60 V. Under these conditions, over 1.5 kW is dissipated in a 0.9 x 0.9 mm die. At the higher  $V_{DS}$ , the current is seen to decay over time during the pulse. This is a result of rising junction temperature within the device and does not signify any permanent degradation.

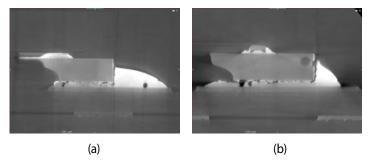

Using a longer pulse duration (25  $\mu$ s), the parts eventually fail from thermal overload. Representative waveforms are shown in Figure 3-19. The time of failure is marked by the abrupt sharp rise in drain current. After this event, the devices are permanently damaged. The withstand time is measured from the beginning of the pulse to the time of failure.

Figure 3-18: EPC2203 fault under load test (FUL) waveforms for a series of increasing drain voltages. Drain pulse is 10  $\mu$ s and  $V_{GS} = 6$  V. The device did not fail for this pulse width. In the  $V_{DS}$  vs. time plot (top),  $V_{DS}$  is Kelvin-sensed directly at the device terminals. In the IDS vs. time plot (center), it is noted that  $I_{DS}$  decreases over time due to self-heating. Resulting output curve for this test sequence (bottom). Drain current is reported as the average current during the pulse. Drain current rolls over in the saturation region owing to device heating at higher  $V_{DS}$ .

Figure 3-19: Fault-under-load test waveforms for a typical EPC2203 (top) and EPC2051 (bottom) at  $V_{DS}$  = 60 V,  $V_{GS}$  = 6 V, and a 25  $\mu$ s drain pulse. The abrupt rise in drain current marks the time of catastrophic thermal failure.

To gather statistics on the withstand time, cohorts of eight parts were tested to failure using this approach. Table 3-1 summarizes the results. EPC2203 was tested at both 5 V (recommended gate drive) and 6 V ( $V_{GS(max)}$ ), with mean withstand time of 20  $\mu$ s and 13  $\mu$ s, respectively. Note that the device survives less time at 6 V because of the higher saturation current. EPC2051 exhibited a slightly lower time-to-fail (9.3  $\mu$ s) compared with the EPC2203 at 6 V. This is expected because of the more aggressive scaling and current density of 5th generation products. However, in all cases, the withstand time is comfortably long enough for most short-circuit protection circuits to respond and prevent device failure. Furthermore, the withstand time showed small part-to-part variability.

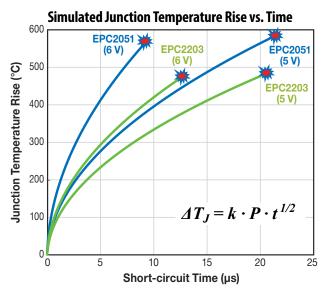

The lower rows in Table 3-1 provide pulse power and energy relative to die size. To gain insight into the relationship between these quantities and the time to failure, time-dependent heat transfer was simulated to determine the rise in junction temperature  $\Delta T_J$  during the short-circuit pulse. The results are shown in Figure 3-20.

| Short-circuit pulse     | EPC2203 (Gen 4) |                | EPC2051 (Gen 5) |                        |  |

|-------------------------|-----------------|----------------|-----------------|------------------------|--|

| V <sub>DS</sub> = 60 V  | $V_{GS} = 6 V$  | $V_{GS} = 5 V$ | $V_{GS} = 6 V$  | $V_{GS} = 5 \text{ V}$ |  |

| Mean TTF (μs)           | 13.1            | 20.0           | 9.33            | 21.87                  |  |

| Std. dev. (μs)          | 0.78            | 0.37           | 0.21            | 2.95                   |  |

| Min. TTF (μs)           | 12.1            | 19.6           | 9.08            | 18.53                  |  |

| Avg pulse power (kW)    | 1.764           | 1.4            | 3.03            | 2.03                   |  |

| Energy (mJ)             | 23.83           | 27.6           | 27.71           | 42.49                  |  |

| Die area (mm²)          | 0.9             | 025            | 1.              | 105                    |  |

| Avg power/area (kW/mm²) | 1.95            | 1.55           | 2.74            | 1.84                   |  |

| Energy/area (mJ/mm²)    | 26.4            | 30.59          | 25.08           | 38.46                  |  |

Table 3-1: Short-circuit withstand time statistics for EPC2203 and EPC2051

Note: Statistics derived from eight devices in each condition. Withstand times are tightly distributed around mean value. Average pulse power and energy correspond to a typical part within the population.

Figure 3-20: Simulated junction temperature rise versus time during the short-circuit pulses for both EPC2051 and EPC2203 at both 5 and 6  $V_{GS}$ . Measured failure times are indicated by red markers. Note that EPC2203 fails catastrophically at a  $\Delta T_J$  of around 475°C, whereas EPC2051 fails around 575°C. The simulated  $\Delta T_J$  is well fit by a simple square root dependence on time (heat diffusion), as shown in the equation. P denotes the average power per unit area, and  $k = 6.73 \times 10^{-5} \, \text{K} \, \text{m}^2 / \text{W} \, \text{s}^{1/2}$ .

The intense power density during the pulse leads to rapid heating in the GaN layer and nearby silicon substrate. Because the pulse is short and heat transfer is relatively slow, only a small thickness of semiconductor ( $<\sim$ 100 µm in depth) can help to absorb the energy. The temperature grows as the square root of time (characteristic of heat diffusion), and linearly with the pulse power. As can be seen in Figure 3-20, for EPC2203, both the 5 V and 6 V conditions fail at the same junction temperature rise of  $\sim$ 475°C.

The same is true for EPC2051, where both conditions fail at the same  $\Delta T_1$  of ~575°C. Three key conclusions stem from these results:

- 1. For a given device, the time to failure is inversely proportional to the power dissipation squared (P-2). This applies for short-circuit and SOA pulses of duration < ~1 ms.

- 2. The intrinsic failure mode resulting from high power pulses is directly linked to the junction temperature exceeding a certain

- 3. Wide bandgap eGaN devices can survive junction temperatures (> 400°C) that are totally inaccessible to silicon devices owing to free-carrier thermal runaway.

To establish whether devices could survive these extreme conditions repetitively, several parts were subjected to over 500,000 cycles under short-circuit conditions that caused device currents about twice the maximum rated pulse current listed on their datasheets. In the test setup, gate bias of either 5 or 6 V<sub>GS</sub> was applied to the device under test (DUT). Drain bias was set at 10  $V_{DC}$  and a 60 mF capacitor was connected across the drain supply. A low R<sub>DS(on)</sub> high-side transistor in series with the DUT controlled the otherwise unlimited flow of current. The control transistor was then pulsed with 5 µs pulses at 1 Hz to give the channel time to re-equilibrate. Table 3-2 shows the various types of devices tested, their datasheet rating for maximum pulsed current, and the amount of short-circuit current that pulsed through the device during each cycle at the start of the test.

| Device  | Туре      | Datasheet<br>pulsed (A) | V <sub>GS</sub> | Mean<br>(A) | Sigma<br>(A) |

|---------|-----------|-------------------------|-----------------|-------------|--------------|

| EPC2203 | 80 V AEC  | 17                      | 5               | 35          | 2.4          |

| EPC2203 | Gen4      | 17                      | 6               | 43          | 2.5          |

| EPC2212 | 100 V AEC | 75                      | 5               | 124         | 2.1          |

| EPCZZIZ | Gen4      | /5                      | 6               | 160         | 3.5          |

| EPC2051 | 100 V     | 27                      | 5               | 68          | 1.0          |

| EPC2051 | Gen5      | 3/                      | 37 6            | 87          | 1.3          |

| FDC20F2 | 100 V     | 74                      | 5               | 147         | 1.6          |

| EPC2052 | Gen5      | 74                      | 6               | 163         | 2.2          |

| FDC2207 | 200 V     | 00 V                    | 5               | 99          | 4.7          |

| EPC2207 | Gen5      | 54                      | 6               | 132         | 5.0          |

Table 3-2: Devices tested under extreme pulsed short-circuit current, typically twice the maximum datasheet limit.

Table 3-3 shows the various key device parameters for EPC2051, the same part number as used in Table 3-2 and in Figure 3-20. Even under these extreme conditions of 500,000 85 A pulses that are more than twice the datasheet maximum ratings, all electrical characteristics remained within datasheet specifications. There was, however, a small reduction in the amount of short circuit current "consumed" by the DUT over time, consistent with the small increase in  $V_{TH}$ . After this 500,000-pulse sequence, this part underwent an unbiased 10 minute anneal at 175°C. As can be seen in the right-hand column of Table 3-3, the electrical parameters and short-circuit current recovered to near their values before being subjected to repetitive pulse stresses. This recovery indicates that no permanent damage occurred from repetitive high-current pulses.

| EPC2051                    | t=0 | 100 k<br>pulses | 500 k<br>pulses | Post 10 min.<br>175°C Anneal |

|----------------------------|-----|-----------------|-----------------|------------------------------|

| V <sub>TH</sub> (V)        | 1.8 | 2               | 2.1             | 1.8                          |

| I <sub>GSS</sub> (μA)      | 11  | 33              | 55              | 23                           |

| I <sub>DSS</sub> (μA)      | 7   | 5.5             | 5.1             | 5.6                          |

| $R_{DS(on)}(m\Omega)$      | 22  | 22.3            | 22.3            | 22                           |

| I <sub>short circuit</sub> | 84  | 77              | 74              | 82                           |

Table 3-3: Key device parameters for EPC2051 at the start of pulse testing, after 100 k pulses, after 500 k pulses, and after a 175°C, 10 minute anneal. Device parameters stayed within datasheet limits at all times.

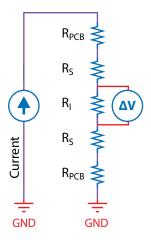

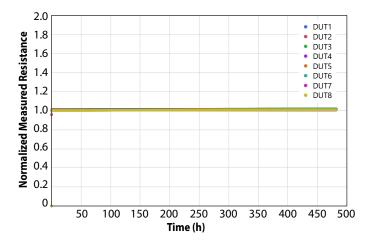

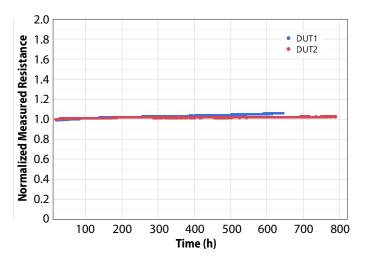

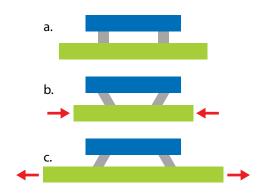

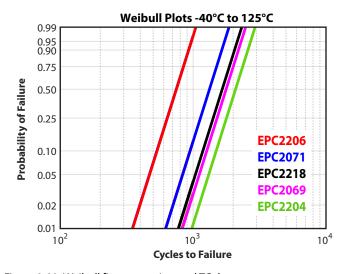

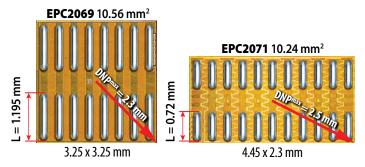

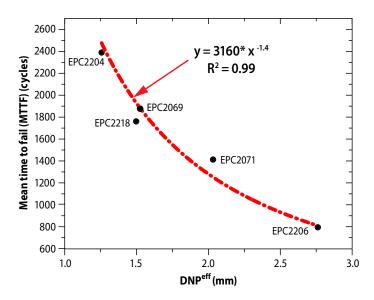

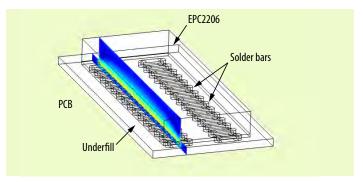

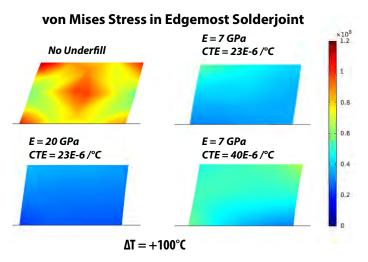

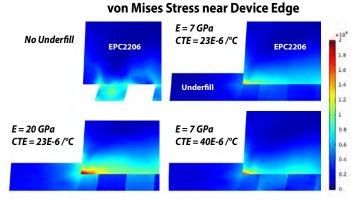

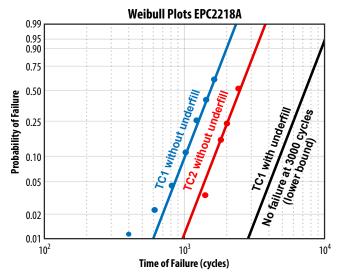

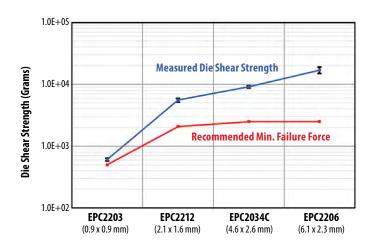

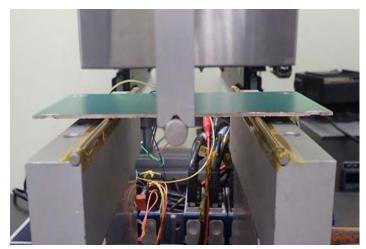

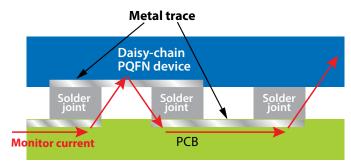

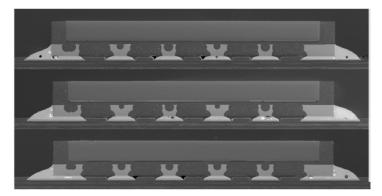

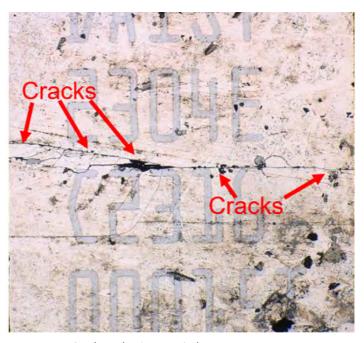

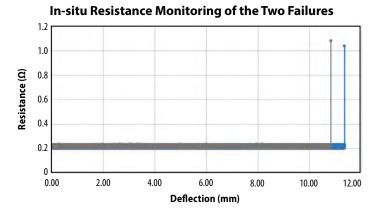

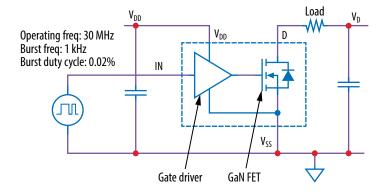

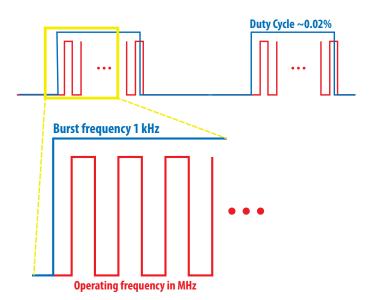

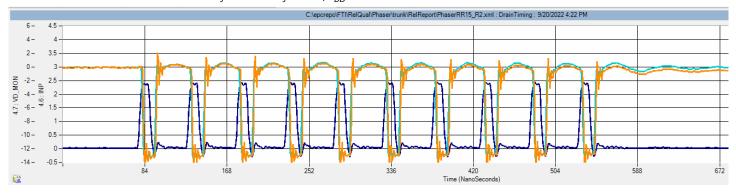

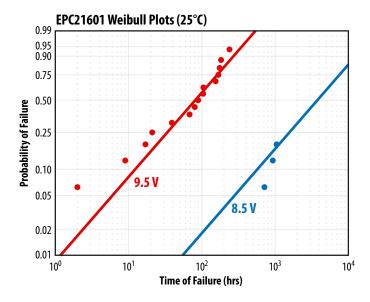

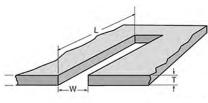

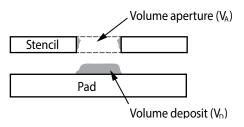

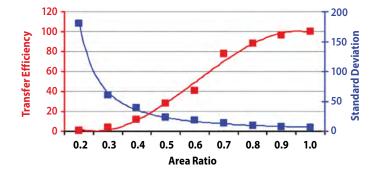

# 3.3.4. Electromigration for copper interconnect