### **Preliminary**

#### **Summary:**

e-GaN® 25 V, 101 A, 0.37 m $\Omega$  typ Surface Mount Package size 3.3mm x 3.3mm

#### Features:

- Ultra-low Q<sub>G</sub> for High Frequency

- PQFN Package with Backside Thermal Pad

- No reverse recovery

#### **Application:**

- High Performance, high power-density DC-DC Conversion

- High-Frequency DC-DC Converters

- Synchronous Rectifiers

- Point of Load Buck Convertor

#### **Description:**

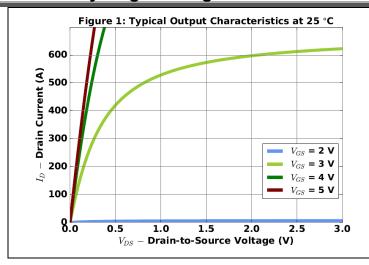

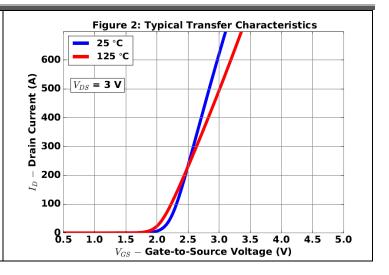

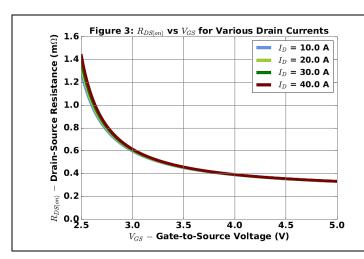

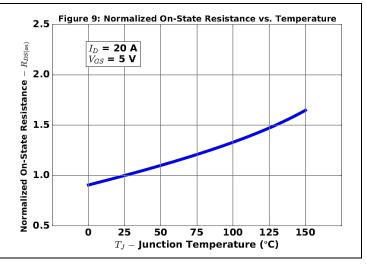

EPC's eGaN® power switching transistors have been specifically designed for critical applications in DC-DC conversion. These devices have exceptionally high electron mobility and a low temperature coefficient resulting in very low  $R_{DS(on)}$  values. The lateral structure of the die provides for very low gate charge ( $Q_G$ ) and extremely fast switching times. These features enable faster power supply switching frequencies resulting in higher power densities, higher efficiencies and more compact packaging. EPC2372 has been specifically designed for synchronous rectifier applications on the secondary side of a 48V-8 or 5 V LLC converter, where it brings an industry leading low  $R_{DS(on)}$   $xQ_G$  figure of merit and enables higher frequency and higher efficiency operation. EPC2372 is also for Point of Load Buck converters.

| Maximum Ratings  |                                                            |            |       |  |

|------------------|------------------------------------------------------------|------------|-------|--|

| Symbol           | Parameter-Conditions                                       | Value      | Units |  |

| $V_{DS}$         | Drain-to-Source Voltage                                    | 25         | V     |  |

|                  | Drain-to-Source Voltage (up to 10,000 5ms pulses at 150°C) | 30         | V     |  |

| I <sub>D</sub>   | Continuous Drain Current at V <sub>GS</sub> = 5 V          | 101        | А     |  |

| $I_{DM}$         | Pulsed (25°C, T <sub>PULSE</sub> = 300 μs)                 | 699        |       |  |

| $V_{GS}$         | Gate-to-Source Voltage                                     | 6          | V     |  |

| V <sub>GS</sub>  | Gate-to-Source Voltage                                     | -4         | V     |  |

| T <sub>J</sub> , | Operating Temperature                                      | -40 to 150 | °C    |  |

| Тѕтб             | Storage Temperature                                        | -40 to 150 | С     |  |

|                     | Static Characteristics (T <sub>J</sub> = 25°C unless otherwise noted) |                                                                            |     |      |     |      |

|---------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------|-----|------|-----|------|

|                     | PARAMETER                                                             | TEST CONDITIONS                                                            | MIN | TYP  | MAX | UNIT |

| $BV_{DSS}$          | Drain to Source Voltage                                               | $V_{GS} = 0 V, I_D = TBD$                                                  | 25  |      |     | V    |

| I <sub>DSS</sub>    | Drain to Source Leakage                                               | $V_{DS} = 25 \text{ V}, V_{GS} = 0 \text{ V}$                              |     | 0.1  |     | mA   |

|                     | Drain to Source Leakage                                               | $V_{DS} = 25 \text{ V}, V_{GS} = 0 \text{ V}, T_{J} = 125^{\circ}\text{C}$ |     |      | 1   |      |

| I <sub>GSS</sub>    | Gate to Source Forward Leakage                                        | V <sub>GS</sub> = 5 V                                                      |     | 0.1  |     | A    |

|                     | Gate to Source Forward Leakage#                                       | V <sub>GS</sub> = 5 V, T <sub>J</sub> = 125°C                              |     | 0.5  |     | mA   |

|                     | Gate to Source Reverse Leakage                                        | V <sub>GS</sub> = -2 V                                                     |     | 300  |     | μΑ   |

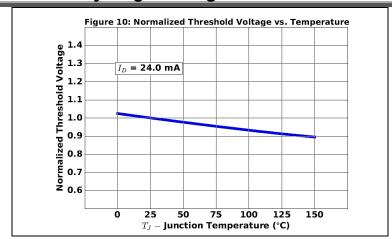

| $V_{GS(TH)}$        | Gate to Source Threshold Voltage                                      | $V_{DS} = V_{GS}$ , $I_D = 24 \text{ mA}$                                  | 0.8 | 1.4  | 2.5 | V    |

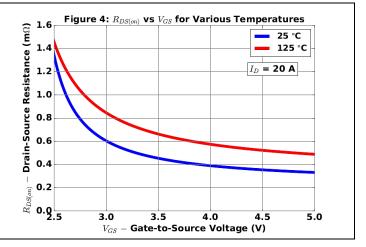

| R <sub>DS(on)</sub> | Drain to Source Resistance                                            | V <sub>GS</sub> = 5 V, I <sub>D</sub> = 20A                                | ·   | 0.37 |     | mΩ   |

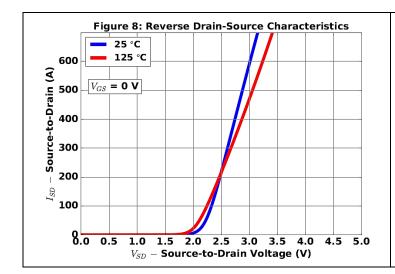

| $V_{SD}$            | Source-Drain Forward Voltage#                                         | $I_S = 0.5 A$ , $V_{GS} = 0 V$                                             |     | 1.6  |     | V    |

All measurements were done with substrate shorted to source.

<sup>#</sup> Defined by design. Not subject to production test.

|                     | <b>Dynamic Characteristics</b> #. (T <sub>J</sub> = 25°C unless otherwise stated) |                                                                                             |     |      |     |            |

|---------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----|------|-----|------------|

|                     | PARAMETER                                                                         | TEST CONDITIONS                                                                             | MIN | TYP  | MAX | UNIT       |

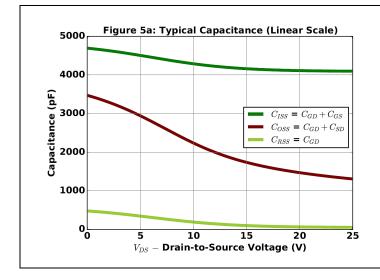

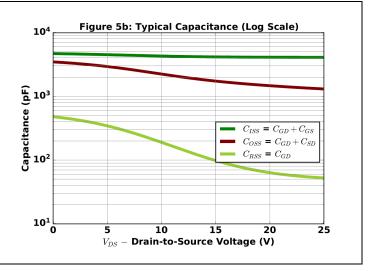

| C <sub>ISS</sub>    | Input Capacitance                                                                 | V <sub>DS</sub> = 12 V, V <sub>GS</sub> = 0 V                                               |     | 4224 |     |            |

| $C_{RSS}$           | Reverse Transfer Capacitance                                                      |                                                                                             |     | 172  |     | pF         |

| Coss                | Output Capacitance                                                                |                                                                                             |     | 2143 |     |            |

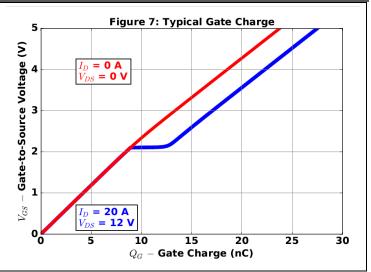

| Q <sub>G</sub>      | Total Gate Charge                                                                 | $V_{DS} = 12 \text{ V}, V_{GS} = 5 \text{ V}, I_{D} = 20 \text{A}$                          |     | 27   |     |            |

| Q <sub>G</sub> Sync | Total Gate Charge Synchronous                                                     | $V_{DS} = 0 \text{ V}, V_{GS} = 5 \text{ V}, I_{D} = 0 \text{A}$                            |     | 24   |     |            |

| $Q_{GS}$            | Gate-to-Source Charge                                                             | $V_{DS} = 12 \text{ V}, I_D = 20 \text{A}$<br>$V_{DS} = 12 \text{ V}, V_{GS} = 0 \text{ V}$ |     | 7    |     | <b>"</b> C |

| $Q_{\sf GD}$        | Gate-to-Drain Charge                                                              |                                                                                             |     | 4    |     | nC         |

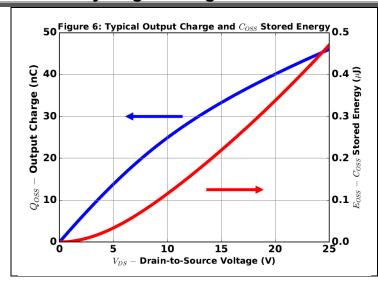

| Q <sub>oss</sub>    | Output Charge                                                                     |                                                                                             |     | 29   |     |            |

| $Q_{RR}$            | Source-Drain Recovery Charge                                                      |                                                                                             |     | 0    |     |            |

All measurements were done with substrate shorted to source.

<sup>#</sup> Defined by design. Not subject to production test.

Negative gate drive voltage increases the reverse drain-source voltage. EPC recommends 0 V for OFF.

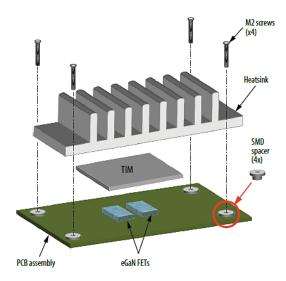

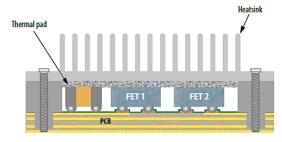

#### TYPICAL THERMAL CONCEPT

The EPC2372 can take advantage of dual sided cooling to maximize its heat dissipation capabilities in high power density designs. *Note that the top of EPC FETs are connected to source potential, so for half-bridge topologies the Thermal Interface Material (TIM) needs to provide electrical isolation to the heatsink*.

Recommended best practice thermal solutions are covered in detail in <a href="How2AppNote012">How to Get More Power Out of an eGaN Converter.pdf</a> (epc-co.com).

Exploded view of heatsink assembly using screws

A cross-section image of dual sided thermal solution

Note: Connecting the heatsink to ground is recommended and can significantly improve radiated EMI

The thermal design can be optimized by using the GaN FET Thermal Calculator (epc-co.com)

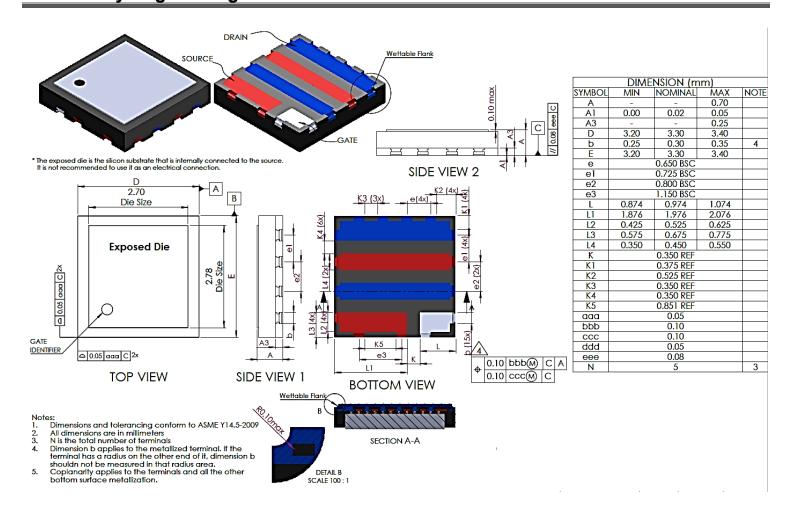

#### PACKAGE OUTLINE AND DIMENSIONS

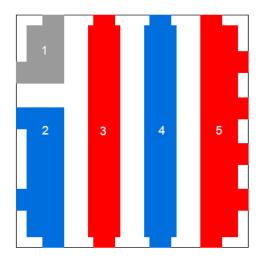

### TRANSPARENT VIEW:

| PIN | DESCRIPTION |

|-----|-------------|

| 1   | Gate        |

| 2   | Source      |

| 3   | Drain       |

| 4   | Source      |

| 5   | Drain       |

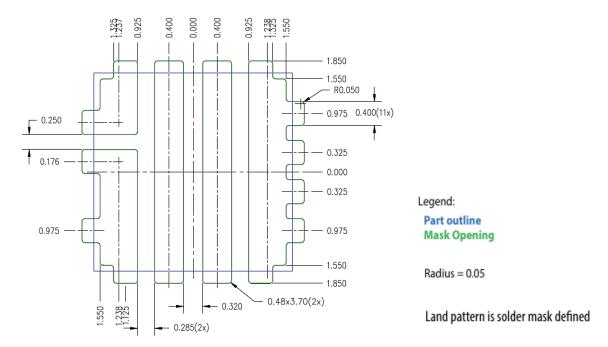

### **RECOMMENDED LAND PATTERN** (units in mm):

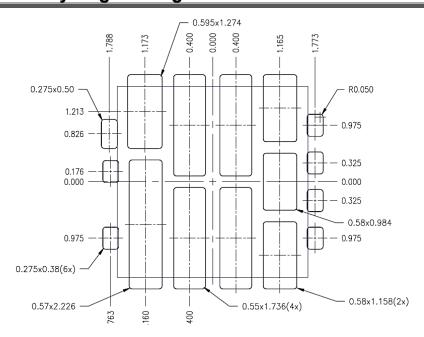

### **RECOMMENDED STENCIL DRAWING** (units in mm):

Legend:

#### **Part Outline**

Stencil Opening

The recommended stencil should be 4mils (100um) thick, must be laser cut, and have openings per drawing.

Intended for use with SAC305 Type 4 solder, reference 88.5% metal content.

Split stencil design can be provided upon request, but EPC has tested this stencil design and not found

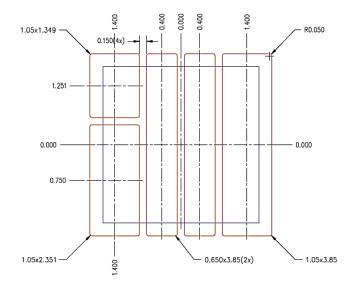

### **RECOMMENDED COPPER DRAWING** (units in mm):

Legend:

Part outline Copper

Radius = 0.05

### ADDITIONAL RESOURCES AVAILABLE

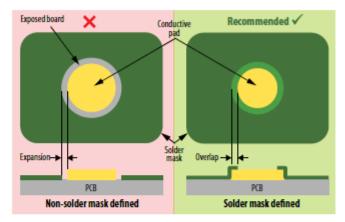

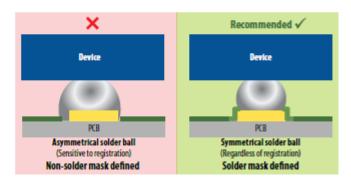

Solder mask defined pads are recommended for best reliability.

Solder mask defined versus non-solder mask defined pad

Effect of solder mask design on the solder ball symmetry

- Assembly resources https://epc-co.com/epc/Portals/0/epc/documents/product-training/Appnote\_GaNassembly.pdf

- Library of Altium footprints for production FETs and ICs https://epc-co.com/epc/documents/altium-files/EPC%20Altium%20Library.zip (for preliminary device Altium footprints, contact EPC)

Prior to final qualification and production release, engineering samples might not meet all datasheet specifications.

Efficient Power Conversion Corporation (EPC) reserves the right to make changes without further notice to any products herein to improve reliability, function or design. EPC does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

eGaN\* is a registered trademark of Efficient Power Conversion Corporation. EPC Patents: http://epc-co.com/epc/AboutEPC/Patents.aspx

Revised August, 2025