### eGaN<sup>®</sup> FET DATASHEET

## EPC2901C\_55

Revised March 27, 2024

# EPC2901C\_55 – Enhancement Mode Power Transistor

V<sub>DS</sub>, 100 V R<sub>DS(on)</sub>, 7 mΩ max I<sub>D</sub>, 36 A 95% Pb/5% Sn Solder

EFFICIENT POWER CONVERSION

Gallium Nitride's exceptionally high electron mobility and low temperature coefficient allows very low  $R_{DS(on)}$ , while its lateral device structure and majority carrier diode provide exceptionally low  $Q_G$  and zero  $Q_{RR}$ . The end result is a device that can handle tasks where very high switching frequency, and low on-time are beneficial as well as those where on-state losses dominate.

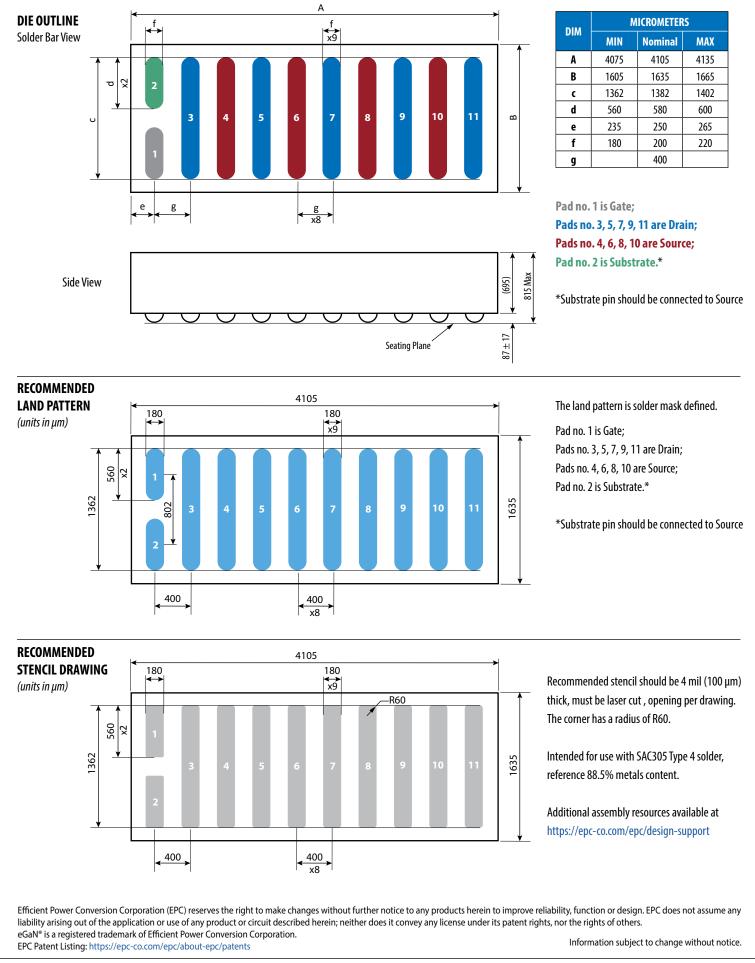

Die size: 4.1 x 1.6 mm

EPC2901C\_55 eGaN® FETs are supplied only in passivated die form with solder bars.

#### Applications

- High-Frequency DC-DC conversion

- Industrial automation

- Synchronous rectification

- Low inductance motor drives

#### Benefits

- Ultra high efficiency

- Ultra low switching and conduction losses

- $\bullet \, Zero \, Q_{RR}$

- Ultra small footprint

Scan QR code or click link below for more information including reliability reports, device models, demo boards!

https://l.ead.me/EPC2901C\_55

|                  | Maximum Ratings                                             |            |      |  |

|------------------|-------------------------------------------------------------|------------|------|--|

|                  | PARAMETER                                                   | VALUE      | UNIT |  |

| v                | Drain-to-Source Voltage (Continuous)                        | 100        |      |  |

| V <sub>DS</sub>  | Drain-to-Source Voltage (up to 10,000 5 ms pulses at 150°C) | 120        | V    |  |

| I <sub>D</sub>   | Continuous (T <sub>A</sub> = 25°C, $R_{\theta JA}$ = 7.3)   | 36         |      |  |

|                  | Pulsed (25°C, $T_{PULSE}$ = 300 µs)                         | 150        | A    |  |

| V <sub>GS</sub>  | Gate-to-Source Voltage                                      | 6          | V    |  |

|                  | Gate-to-Source Voltage                                      | -4         | v    |  |

| ٦J               | Operating Temperature                                       | -40 to 150 | °C   |  |

| T <sub>STG</sub> | Storage Temperature                                         | -55 to 150 | C    |  |

| Thermal Characteristics |                                                  |     |      |  |

|-------------------------|--------------------------------------------------|-----|------|--|

|                         | PARAMETER                                        | ТҮР | UNIT |  |

| R <sub>θJC</sub>        | Thermal Resistance, Junction-to-Case             | 1   |      |  |

| R <sub>θJB</sub>        | Thermal Resistance, Junction-to-Board            | 2   | °C/W |  |

| R <sub>0JA</sub>        | Thermal Resistance, Junction-to-Ambient (Note 1) | 54  | ]    |  |

Note 1:  $R_{0IA}$  is determined with the device mounted on one square inch of copper pad, single layer 2 oz copper on FR4 board. See https://epc-co.com/epc/documents/product-training/Appnote\_Thermal\_Performance\_of\_eGaN\_FETs.pdf for details.

| Static Characteristics ( $T_J = 25^{\circ}$ C unless otherwise stated) |                                              |                                                                        |                 |       |     |      |  |  |

|------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------|-----------------|-------|-----|------|--|--|

|                                                                        | PARAMETER                                    | TEST CONDITIONS                                                        | MIN             | ТҮР   | MAX | UNIT |  |  |

| BV <sub>DSS</sub>                                                      | Drain-to-Source Voltage                      | $V_{GS} = 0 V, I_D = 300 \mu A$                                        | 100             |       |     | V    |  |  |

| I <sub>DSS</sub>                                                       | Drain-Source Leakage                         | $V_{GS} = 0 V, V_{DS} = 80 V$                                          |                 | 2     | 250 | μA   |  |  |

|                                                                        |                                              | $V_{GS} = 0 V, V_{DS} = 80 V, T_{J} = -55^{\circ}C$                    |                 | 0.9   | 50  |      |  |  |

| I <sub>GSS</sub>                                                       | Gate-to-Source Forward Leakage               | $V_{GS} = 5 V$                                                         |                 | 0.019 | 2   | mA   |  |  |

|                                                                        |                                              | $V_{GS} = 5 V, T_{J} = -55^{\circ}C$                                   |                 | 0.01  | 1.5 |      |  |  |

|                                                                        | Gate-to-Source Reverse Leakage               | $V_{GS} = -4 V$                                                        |                 | 1.4   | 250 |      |  |  |

|                                                                        |                                              | $V_{GS} = -4 V, T_J = -55^{\circ}C$                                    |                 | 0.14  | 50  | μA   |  |  |

| V <sub>GS(TH)</sub>                                                    | Gate Threshold Voltage                       | $V_{DS} = V_{GS}$ , $I_D = 5 \text{ mA}$                               | 0.8             | 1.6   | 2.5 | v    |  |  |

|                                                                        |                                              | $V_{DS} = V_{GS}$ , $I_D = 5 \text{ mA}$ , $T_J = -55^{\circ}\text{C}$ | 1.7 2.7         |       | 2.7 |      |  |  |

| R <sub>DS(on)</sub>                                                    | Drain-Source On Resistance                   | $V_{GS} = 5 \text{ V}, \text{ I}_{D} = 25 \text{ A}$                   | 4.8 7   3.1 6.5 |       | 7   | mΩ   |  |  |

|                                                                        |                                              | $V_{GS} = 5 V, I_D = 25 A, T_J = -55^{\circ}C$                         |                 |       | 6.5 |      |  |  |

| $V_{SD}$                                                               | Source-to-Drain Forward Voltage <sup>#</sup> | $V_{GS} = 0 V, I_{S} = 0.5 A$                                          |                 | 1.8   |     | V    |  |  |

| # Defined by                                                           | design. Not subject to production test.      |                                                                        |                 |       |     |      |  |  |

All measurements were done with substrate connected to source.

## eGaN<sup>®</sup> FET DATASHEET

| Dynamic Characteristics <sup>#</sup> (T <sub>J</sub> = 25°C unless otherwise stated) |                                              |                                                               |     |      |      |      |  |

|--------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------|-----|------|------|------|--|

|                                                                                      | PARAMETER                                    | TEST CONDITIONS                                               | MIN | ТҮР  | MAX  | UNIT |  |

| C <sub>ISS</sub>                                                                     | Input Capacitance                            |                                                               |     | 756  | 1020 |      |  |

| C <sub>RSS</sub>                                                                     | Reverse Transfer Capacitance                 | $V_{GS} = 0 V, V_{DS} = 50 V$                                 |     | 9.25 | 13   |      |  |

| C <sub>OSS</sub>                                                                     | Output Capacitance                           |                                                               |     | 493  | 650  | pF   |  |

| C <sub>OSS(ER)</sub>                                                                 | Effective Output Capacitance, Energy Related |                                                               |     | 567  |      |      |  |

| C <sub>OSS(TR)</sub>                                                                 | Effective Output Capacitance, Time Related   |                                                               |     | 711  |      |      |  |

| R <sub>G</sub>                                                                       | Gate Resistance                              |                                                               |     | 0.3  |      | Ω    |  |

| Q <sub>G</sub>                                                                       | Total Gate Charge                            | $V_{GS} = 5 V, V_{DS} = 50 V, I_{D} = 25 A$                   |     | 6.9  | 10   |      |  |

| Q <sub>GS</sub>                                                                      | Gate to Source Charge                        |                                                               |     | 1.9  |      |      |  |

| Q <sub>GD</sub>                                                                      | Gate to Drain Charge                         | $V_{\rm DS} = 50 \text{ V}, \text{ I}_{\rm D} = 25 \text{ A}$ |     | 1.35 | 2    |      |  |

| Q <sub>G(TH)</sub>                                                                   | Gate Charge at Threshold                     |                                                               |     | 1.2  |      | nC   |  |

| Q <sub>OSS</sub>                                                                     | Output Charge                                | $V_{GS} = 0 V, V_{DS} = 50 V$                                 |     | 36   | 45   |      |  |

| Q <sub>RR</sub>                                                                      | Source-Drain Recovery Charge                 |                                                               |     | 0    |      |      |  |

# Defined by design. Not subject to production test. All measurements were done with substrate connected to source.

#### **DIE MARKINGS**

| 2901                                        |                |                          |                                 |                                 |  |

|---------------------------------------------|----------------|--------------------------|---------------------------------|---------------------------------|--|

| YYYY                                        | Dout           | Laser Markings           |                                 |                                 |  |

| Die orientation dot ZZZZ                    | Part<br>Number | Part #<br>Marking Line 1 | Lot_Date Code<br>Marking Line 2 | Lot_Date Code<br>Marking Line 3 |  |

| Gate Pad solder bar<br>is under this corner | EPC2901C_55    | 2901                     | YYYY                            | 2222                            |  |

## eGaN<sup>®</sup> FET DATASHEET

## EPC2901C\_55