# 高周波共振型コンバータの eGaN® FET

David Reusch, Ph.D.、アプリケーション部門ディレクタ、Johan Strydom, Ph.D.、アプリケーション部門バイス・プレジデント

このホワイト・ペーパーでは、高周波共振型コンバータにeGaN FET技術を適用しています。これまでは、ハード・スイッチングの絶縁 型および非絶縁型の用途で、eGaN FETが提供する利点に焦点を当てました。このホワイト・ペーパーでは、既存のパワーMOSFET デバイスで実現可能な特性と比較して、ソフト・スイッチングの用途における効率と出力電力密度を改善するeGaN FETの能力を 示します。1 MHzを超える周波数で動作する共振型の構成を利用した12 V出力で48 V入力の高周波絶縁型中間バス・コンバータ (IBC:intermediate bus converter) を紹介します。

# 概要

分散型電源システムは、電気通信、ネットワーク、およびハイエンド・サーバーのアプリケーションで普及しており、一般に通信業界で採用されている48 Vのバ ス電圧を利用しています。48 Vのバスから、多くの絶縁されたPOL (負荷点) コンバータが最終負荷に電力を供給するので、安全のために絶縁が必要です。 図1 (a) に示す従来の分散型電源アーキテクチャ (DPA: distributed power architecture) は、AC / DCフロントエンド・コンバータを使って48 Vのバス電圧を 供給します。48 Vのバス電圧から、多数の安定化された絶縁型DC / DC POLコンバータを使って、個々の負荷に必要な電圧と電力を供給します。通信、ネット ワーク、および、ハイエンド・サーバーの各システムがより複雑になるにつれて、増加する多数の負荷に要求される電圧と電流が大幅に増加しています [1]。これ らのシステムに電力を供給する多数の安定化した48V入力の絶縁型DC/DC POLコンバータを使うと、システムのコスト、大きさ、複雑さが大幅に増加します。

分散型電源アーキテクチャ(DPA)

従来の分散型電源アーキテクチャの制限は、負荷の電力需要が増加す るにつれて、絶縁型コンバータが複雑になることです。完全に安定化さ れた絶縁型POLコンバータは、低電圧の非絶縁型POLコンバータよりも はるかに大きく、複雑で、高価です。絶縁型コンバータは、絶縁への要求 のため、かさばる変圧器と複雑な制御につながり、これによって、効率 と電力密度が低下します。設計を簡素化するために、中間バス・アーキテ クチャ (IBA: intermediate bus architecture) の概念が提案されました [2],[3]。図1(b)に示す一般的なIBAのアプローチでは、絶縁の要求を満 たし、9.6~12 Vの範囲の中間バス電圧を供給する48 Vの絶縁型バス・ コンバータの数を削減しています。小型、高効率な安定化された非絶縁 POLコンバータによって負荷に供給される最終的な安定化によって、こ のバス・コンバータは、安定化していないDC/DCトランスとして動作させ ることができ、効率が向上し、コストが削減されます。このIBAは現在、 多くの分散型電源システムで広く使われており、従来のアーキテクチャと 比べて性能が向上し、システム全体のコストを削減できます。

DCXまたはDC/DCトランスとも呼ばれる安定化していないバス・コン バータは通常、最高の効率と電力密度を実現するためにデューティ比

中間バス・アーキテクチャ(IBA) 交流入力:90~265 V 交流入力:90~265 V DC/DC 9.6 V - 12 V 3.3 V POL 3.3 V

図1:(a) 従来の分散型電源アーキテクチャと、 (b) 中間バス・アーキテクチャ。

50%付近で動作します。今日のバス・コンバータの大部分は、効率を最大化するために、より低い周波数で動作する従来のハード・スイッチングのブリッジ構成 を採用しています。より低いスイッチング周波数では、絶縁トランスと出力コイルは非常に大きく、基板面積の大部分を占めます。電力密度を改善するために、 動作周波数を上げてコイルとトランスのサイズを小さくすることができます [4]。従来のハード・スイッチング構成で周波数が高くなると、ボディ・ダイオードの 導通、逆回復、スイッチングによる損失が大幅に増加し、コンバータの出力電力能力が制限されます。

EPC: 電力変換技術のリーダー | EPC-CO.COM/EPC/JP | ©2020

### 高周波共振型バス・コンバータ

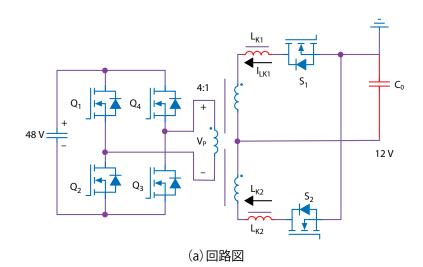

より高いスイッチング周波数で効率を改善するために、共振型の構成が考えられます。共振型構成 [5]~[8] は、DC / DCトランスの用途で特に有効です。これは、安定化の要件がなくなることによって、コンバータが常に共振周波数で動作できるようになるためです。この作業の中で、高周波中間バス・コンバータ (IBC) にeGaN FETを利用することの利点を検討します。図2に示す回路構成では、トランスの磁化インダクタンス (LM)、および漏れインダクタンス (LK)と小さな出力容量 (CO)との共振を利用して、ゼロ電圧スイッチング (ZVS)を実現し、オフ時の電流を制限し、ボディ・ダイオードが導通しないようにします [5]。

図2: 高周波バス・コンバータ [5]。

# 実験のセットアップ

高周波共振型バス・コンバータの用途でeGaN FETとSi MOSFETの性能を 直接比較するために、同じようなオン抵抗のデバイスを選択し、同じ回路構 成を使って、eGaN FETとMOSFETで同じようなレイアウトになるようにし ました。eGaN FETとSi MOSFETの主要なパラメータの直接比較が表IとIIで す。この作業で使われる性能指数FOM (Figures of Merit) は、ゲート電荷 Q<sub>G</sub>×オン抵抗R<sub>DS(on)</sub>と出力電荷Q<sub>OSS</sub>×R<sub>DS(on)</sub>です。これらの特別なFOM は、スイッチング関連の損失を低減するソフト・スイッチング構成に基づいて 選択されたため、FETのゲート駆動と導通が主要な損失要因となります。デ バイスの出力電荷は、ZVSを達成するために必要なエネルギーに直接影響 します。ZVSを実現するために必要なエネルギーを削減すると、デッドタイム が短縮され、電力供給期間 (図2 (b) のt<sub>n</sub>~t<sub>1</sub>) が長くなり、高周波共振型コ ンバータのRMS電流が小さくなります。Si MOSFETと比べて、eGaN FETは、 大幅な改善を示し、ゲート駆動FOMは、1次側の100 Vおよび2次側の40 Vの デバイスで、それぞれ約1/4および1/3に向上し、出力電荷FOMは約1/1.6およ び1/2に向上します。eGaN FETは、ミラー電荷の削減という形で性能を改善 し、1次側デバイスで発生するオフ時のスイッチング損失を削減します。さら なる利点として、eGaN FETのLGAパッケージは、従来のSi MOSFETパッケー ジ (スーパーSO8) と比べて、パッケージの寄生インダクタンスが小さくなっ ています。これらすべての利点をまとめると、高度な回路構成と低損失eGaN FETとを組み合わせて使うことによって、スイッチング周波数は数MHzと高く できます。

| デバイスの比較                       |              |                |

|-------------------------------|--------------|----------------|

| パラメータ                         | EPC2001      | BSC057N08      |

| 電圧定格 (V <sub>DSS</sub> )      | 100 V        | 80 V           |

| R <sub>DS(on)</sub>           | 5.6 mΩ @ 5 V | 5.2 mΩ @ 8 V*  |

| ZVSでのQ <sub>G</sub>           | 5.6 nC @ 5 V | 25.9 nC @ 8 V* |

| Q <sub>GD</sub> @ VIN         | 2.2 nC       | 8.1 nC*        |

| Q <sub>OSS</sub> @ Vin        | 35 nC        | 62 nC*         |

| $FOM = Q_G \times R_{DS(on)}$ | 32.5 pC · Ω  | 134.7 pC · Ω   |

| $FOM = Q_{OSS} x R_{DS(on)}$  | 196 pC · Ω   | 322.4 pC · Ω   |

\*メーカーのデータシートの曲線から計算

表I: V<sub>IN</sub> = 48 V、V<sub>OUT</sub> = 12 Vの1次側デバイスとしての eGaN FETとSi MOSFETとの比較。

| デバイスの比較                           |              |                |

|-----------------------------------|--------------|----------------|

| パラメータ                             | EPC2015      | BSC027N04      |

| 電圧定格 (V <sub>DSS</sub> )          | 40 V         | 40 V           |

| R <sub>DS(on)</sub>               | 3.2 mΩ @ 5 V | 2.9 mΩ @ 8 V*  |

| ZVSでのQ <sub>G</sub>               | 8.3 nC @ 5 V | 27.5 nC @ 8 V* |

| Q <sub>GD</sub> @ 20 V            | 2.2 nC       | 6.5 nC*        |

| Q <sub>OSS</sub> @ 20 V           | 18.5 nC      | 40 nC*         |

| $FOM = Q_G \times R_{DS(on)}$     | 26.6 pC · Ω  | 79.8 pC · Ω    |

| $FOM = Q_{OSS} \times R_{DS(on)}$ | 59.2 pC · Ω  | 116 pC · Ω     |

<sup>\*</sup>メーカーのデータシートの曲線から計算

表 $II: V_{IN} = 48 \text{ V}, V_{OUT} = 12 \text{ V} の 2 次側デバイスとしの eGaN FETと Si MOSFETとの比較。$

### 実験結果

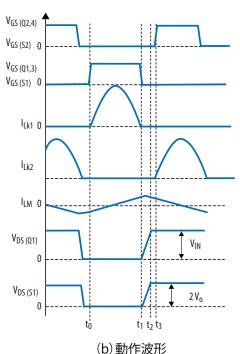

高周波共振型コンバータにおけるeGaN FETとSi MOSFET の性能を比較するために、図3に示す2つの実験プロトタ イプを図2(a)の回路図に基づいて設計しテストしまし た。デバイスの性能のみを正確に比較するために、これ らのプロトタイプは両方とも、[4]で設計したものと同じ 3F45 Mn-Znトランス・コアと同一の巻線にしました。1次 側入力コンデンサと2次共振コンデンサの配置は、両方の 設計で同じにしており、1次側ループおよび2次側ループに 対して、同じ寄生インダクタンスになるようにしたので、Si MOSFETとeGaN FETの異なるパッケージによって生じる 寄生インダクタンスのみが異なります。より低い仕様上の R<sub>DS(on)</sub>と改善されたパッケージを備えたeGaN FETを使 うことによって、実質的な実装領域が大幅に縮小し、Si MOSFETのベンチマーク設計と比べてパワー段のサイズ が30%削減されました。eGaN FETベースの設計では、1 次側デバイスと2次側デバイスに対して米テキサス・インス ツルメンツのドライバLM5113を使い、デバイスを5 Vで駆

図3: $V_{IN} = 48 \text{ V}$ 、 $V_{OUT} = 12 \text{ V}$ の実験に使うバス・コンバータのプロトタイプ。

動しました。Si MOSFETベースの設計では、LM5113と同等の性能のドライバを使い、1次側を8 V、2次側を5 Vで駆動し、オン状態のときの抵抗のわずかなペナルティを払って支配的なゲート損失を低減することによって、高周波Si MOSFETの性能を改善します。どちらの設計でも、ゲート駆動回路は基板の裏面に配置しました。これらのドライバ・チップの公称48 V入力からの電圧の発生は、この作業には含まれていませんが、スイッチで発生するゲート駆動損失は考慮されています。

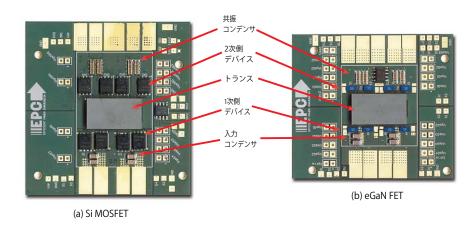

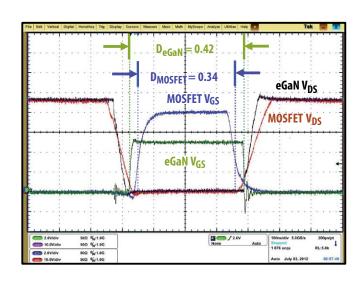

各設計に対する1.2 MHzでの実験におけるスイッチング波形を図4と5に示します。どちらの設計も、デバイスのオフ状態の期間(図2 (b) の $t_1 \sim t_2$ )でZVS (ゼロ電圧スイッチング)を実現するため、エアー・ギャップを介してトランスに組み込まれた磁化インダクタンスは同じです。1次側および2次側のeGaN FETによって提供される出力電荷( $Q_{OSS}$ )がほぼ半分に減ったことで、ZVSの遷移は比例的に短い期間で実現でき、実効的なデューティ比が増加し、コンバータ全体の性能が向上します。Si MOSFETの設計の場合、ZVSに必要なデッドタイムは87 nsと測定され、各デバイスの実効的なデューティ比は34%に制限されていました。より高速スイッチングのeGaN FETでは、デッドタイムは42 nsに短縮され、各デバイスのデューティ比が42%になり、電力供給期間を長くできました。スイッチング波形から、eGaN FETのゲート駆動速度は、より低いゲート駆動電圧で駆動したときでも、同等のSi MOSFETよりも大幅に高速であり、スイッチング速度の高速化とゲート損失の低減の両方を実現していることが分かります。

図4: $F_S = 1.2 \text{ MHz}$ 、 $V_{IN} = 48 \text{ V}$ 、 $I_{OUT} = 26 \text{ A}$ でのeGaN FETおよびSi MOSFETの1次側設計のZVSスイッチング遷移。

図5: $F_S = 1.2 \text{ MHz}$ 、 $V_{IN} = 48 \text{ V}$ 、 $I_{OUT} = 26 \text{ A}$ でのeGaN FETおよびSiMOSFETの1次側設計の実効的なデューティ比を示すスイッチング波形。

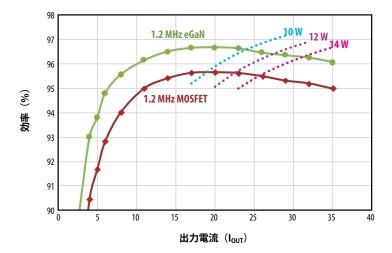

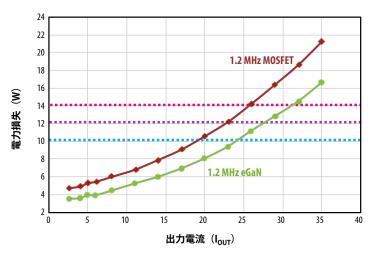

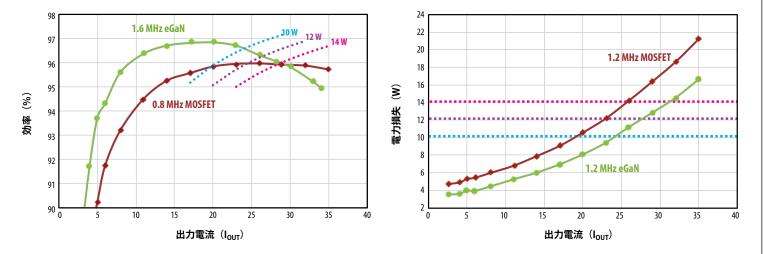

1.2 MHzで動作する2つの設計の間の効率と電力損失の比較を図6に示します。eGaN FETベースのコンバータは、Si MOSFETの同等品に比べてピーク効率が1パーセント・ポイント向上する結果、電力損失が約25%減少します。各ブリック設計は、コンバータのサイズに基づいて与えられた全負荷損失によって熱的に制限されるため、電力損失の削減は、出力電力処理能力の向上に直接かかわります。eGaN FETコンバータは、ベンチマークのSi MOSFET設計と比べたとき、全コンバータ損失を同じに維持しながら、出力電力を最大65 W増やすことができます。両方の設計で約12 Wの最大電力損失を想定すると、eGaN FETベースのコンバータの出力電力は、270 Wから325 Wへと増加します。

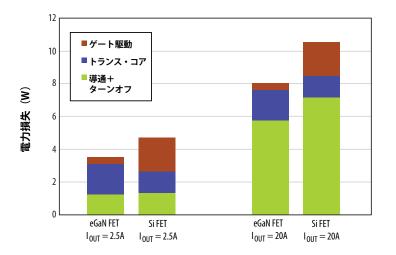

出力電流2.5 Aと20 Aにおける1.2 MHz設計の損失の内訳が図7です。eGaN FETはゲート駆動損失を低減し、すべての負荷条件で効率を改善するという結論になります。大電流では、全電力損失において導通損失が支配的ですが、ZVSのデッドタイムが短いeGaN FETコンバータは、実効的なデューティ比に反比例して小さくなったRMS電流によって、導通損失が低減されます。eGaN FETコンバータに対するZVS時間の短縮のもう1つの影響は、トランスのコア損失の増加です。これは、電力伝送期間の継続時間の増加によって生成されるトランスの磁束密度が高くなることによります。トランスのコア損失の増加は、大電流での導通損失の減少よりもはるかに小さく、eGaN設計の大電流での電力の削減が大きくなります。

1.2 MHzでの結果から、Si MOSFETコンバータがその周波数限界に近づいていることが分かります。すなわち、ZVS遷移時間は全期間のかなりの部分になりつつありますが、eGaN FETにはスイッチング周波数をさらに高められる能力があります。Si MOSFETに対して、eGaN FETで可能な周波数改善を比較するために、Si MOSFET設計のコンバータ周波数を800 kHzに低下させ、eGaN設計を1.6 MHzに高めました。これらの設計の両方で、コア構造は同じままであり、異なる動作周波数に対して最適化されていません。

図6:  $V_{IN} = 48 \text{ V}$ 、 $V_{OUT} = 12 \text{ V}$ 、 $F_S = 1.2 \text{ MHz}$ におけるeGaN FETおよびSi MOSFETに基づく共振型バス・コンバータの間の実験の比較。

図7: eGaN FETおよびSi MOSFET に基づく共振型バス・コンバータの損失 の内訳。 $V_{\rm IN}=48~\rm V,~V_{OUT}=12~\rm V,~F_S=1.2~MHz$ のとき。

各設計の間の効率と損失の比較が図8です。eGaN FET設計では、ピーク効率が0.9%向上し、出力電流29 Aまで電力損失が小さくなります。eGaN FETベースのコンバータにおいて、20 Aを超える電流で効率が急激に低下したのは、交流トランスの巻線損失が増加し、高周波で生じる実効的なデューティ比の減少によるものです。逆に、800 kHzのSi MOSFET設計の効率が平坦なのは、交流トランスの巻線損失が減少し、低い周波数で実効的なデューティ比が大きくなるためです。

図8:  $F_S=1.6$  MHzのeGaN FETおよび $F_S=800$  kHzのSi MOSFET に基づく共振型バス・コンバータの間の実験による比較。 $V_{\rm IN}=48$  V,  $V_{\rm OUT}=12$  Vのとき。

## まとめ

ハード・スイッチング用途で重要な2つの主要パラメータ、Q<sub>GD</sub>とQ<sub>RR</sub>に関して、eGaN FETは、シリコンMOSFETに比べて明らかな利点を備えていることがすでに示されていますが、ソフト・スイッチング用途では、ほとんど影響しません。このホワイト・ペーパーで、eGaN FETは、Si MOSFETと比べて、ソフト・スイッチング/共振型コンバータの性能を大幅に改善できることも実証しました。高周波の用途では、以下が改善されます:

- 1) 出力容量は、ZVSを達成するために必要な循環エネルギーを減らし、転流時間を短くできるため、有効な電力供給期間が長くなり、全体的な効率が向上します。

- 2) eGaN FETによって提供されるゲート容量によって、駆動電圧を低くでき、スイッチング速度が速くなるので、ゲート駆動損失が減少します。 高周波用途でeGaN FETを採用すると、コンバータの性能を犠牲にすることなく周波数を高めることができます。

#### 参考文献:

- [1] M. M. Jovanovic, "Power Conversion Technologies For Computer, Networking, And Telecom Power Systems Past, Present And Future," International Power Conversion & Drive Conference (IPCDC) St. Petersburg, Russia, June 8-9, 2011.

- [2] Martin F. Schlecht, "High Efficiency Power Converter," United State Patent No. 7,269,034.

- [3] White, R. V., "Emerging On-Board Power Architectures," APEC '03, Eighteenth Annual IEEE, Volume 2, 9-13 Feb. 2003, pp. 799-804.

- [4] Reusch, D.; Lee, F.C.; "High Frequency Bus Converter With Low Loss Integrated Matrix Transformer," Applied Power Electronics Conference and Exposition (APEC), 2012 Twenty-Seventh Annual IEEE, pp.1392-1397, 5-9 Feb. 2012.

- [5] Y. Ren, M. Xu, J. Sun, and F. C. Lee, "A Family Of High Power Density Unregulated Bus Converters," IEEE Transactions, Power Electron, Vol. 20, no. 5, pp. 1045–1054, Sep. 2005.

- [6] Y. Ren, "High Frequency, High Efficiency Two-Stage Approach for Future Microprocessors," Ph.D. Dissertation, Virginia Tech, Blacksburg, Virginia, April 2005.

- [7] Y. Ren, F.C. Lee, and M. Xu, "Power Converters Having Capacitor Resonant With Transformer Leakage Inductance," U.S. Patent 7,196,914, March 27 2007.

- [8] Patrizio Vinciarelli, "Point of load sine amplitude converters and methods," U.S. Patent 7,145,786, Dec. 5 2006.