eGaN対シリコン

GaNの話 – John Glaser , Ph.D.

1 23, 2020

この記事は、2016年6月13日にJohn Glaser博士とDavid Reusch博士によって書かれ、米Power Systems Design誌のウエブ・サイトで公開されました。

同期整流器におけるeGaN FETとシリコンMOSFETのデッドタイム損失の比較

ハード・スイッチング、ソフト・スイッチング、高周波電力変換など、さまざまなアプリケーションで、eGaN FETとシリコンMOSFETが比較されています。これらの調査は、eGaN FETがシリコンMOSFETよりも、効率と電力密度において大きな利点があることを示しています。ここでは、同期整流器(SR:synchronous rectifier)の用途でのeGaN FETの使用とデッドタイム管理の重要性に焦点を当てます。eGaN FETは、低オン抵抗RDS(on)と低電荷の利点を超えて、同期整流器のデッドタイムによる損失を劇的に削減できることを示します。

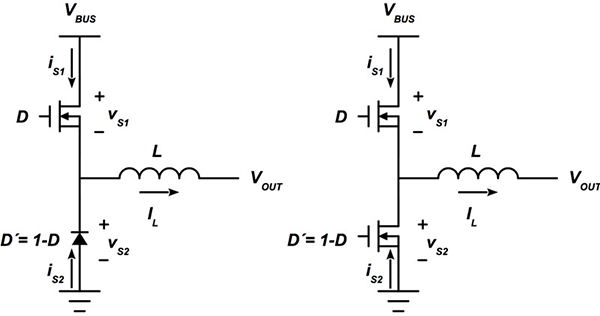

初期の高周波スイッチ・モード・パワー・コンバータは一般的に、ハーフブリッジ構成に、完全に制御されたスイッチ(S1)とダイオード整流器(S2)を使っていました [1]。図1aは、このような構成のバック(降圧型)・コンバータの一例です。パワーMOSFETが、より手頃な価格になり、高効率がより重要になるにつれて、設計者は、図1bに示すように、S1への制御信号で相補的に駆動されるダイオードをMOSFETに置き換え始めました [2]。ダイオードからMOSFETへの置き換えは、同期整流器(SR)と呼ばれます。ダイオードの接合部電圧は出力電圧の大部分を占める可能性があるため、低出力電圧と大電流が必要な場合、同期整流の利用は特に重要です [3]。高効率化に対する要求が、より多くのアプリケーションに広がるにつれて、SRの使用が劇的に増えました。

図1. ダイオード整流器(左)または同期整流器(右)を備えたバック・コンバータ。

図1. ダイオード整流器(左)または同期整流器(右)を備えたバック・コンバータ。

eGaN FETは特に、SR動作に適しています。シリコンFETと比べて、ほぼすべての特性に基づく性能指数FOM(figure-of-merit)が全体的に劇的に改善された結果、コンバータの効率と電力密度が大幅に向上しました [4]。ただし、シリコンMOSFETがeGaN FETに勝ると思われる領域が1つあります。つまり、シリコンMOSFETに対してeGaN FETのボディ・ダイオード電圧降下が大きいことで、これがSRのデッドタイム損失の増加につながる可能性があります [5]。これは、注意深くデッドタイムを管理すること、ショットキー・ダイオードの外付け、または、その両方で軽減できますが、設計が複雑になる可能性があります。これのいくらかは、シリコンMOSFETのボディ・ダイオードが逆回復するという事実によってバランスがとれていることが示唆されましたが、シリコンMOSFETのこの側面に関するデータは驚くほど少ないようです。より良い理解が必要です。

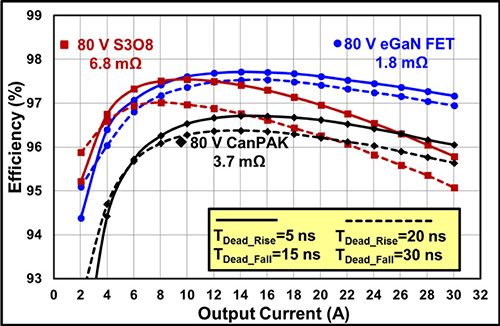

図2. eGaN FETまたはシリコンMOSFETを使ったときの48 V入力、12 V出力、300 kHzのハード・スイッチング・バック・コンバータの効率に対するデッドタイムの影響。

図2. eGaN FETまたはシリコンMOSFETを使ったときの48 V入力、12 V出力、300 kHzのハード・スイッチング・バック・コンバータの効率に対するデッドタイムの影響。

シリコンFETとGaN FETの実験による比較は、FETの種類を除いて、すべての面で同一のハード・スイッチング、300 kHz、48 V入力、12 V出力のバック・コンバータ構成を使って実施しました。図1に、ゲート駆動の最小デッドタイムと、追加したデッドタイム30 ns(各エッジで15 ns)での結果を示します。30 Aの出力では、追加したデッドタイムは、eGaN FETの効率が0.22%低下し、シリコンMOSFETの効率は0.50%および0.56%低下し2倍以上悪化します。eGaN FETの利点は主に、逆回復がないことによります。この記事の残りの部分では、この効果について詳しく説明します。

同期整流器SRの動作に対するデッドタイムの影響

実用的なハード・スイッチングのバック・コンバータでは、制御用FETのS1と同期整流(SR)用FETのS2の両方ともスイッチング時間がゼロではありません。出力電流が非常に大きいとき、S2の導通損失を最小限に抑えるには、オン抵抗RDS(on)が小さい、つまり大きなMOSFETが必要になり、このデバイスの容量の増加によってスイッチング速度が遅くなります。制御用FET のS1とSR用のS2に純粋に相補的な制御信号を使うと、速度が遅いMOSFETのスイッチング遷移が重なり、両方のスイッチが同時に導通して短絡したシュートスルー(貫通)電流によって、損失が大きくなります。

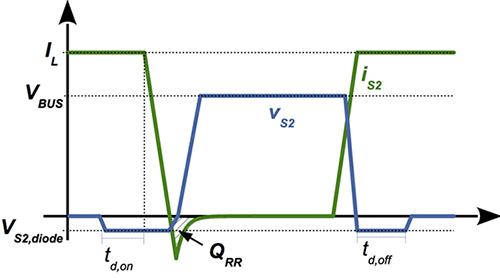

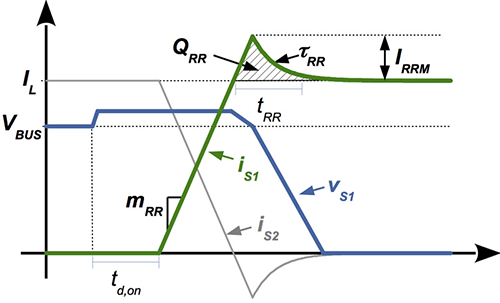

この損失は、SRがターンオフtd,onした後、制御用FETのターンオンの遅延またはデッドタイム、および制御用FETがターンオフtd,offした後、SRのターンオンの遅延によって防止できます。デッドタイム期間中、SRのボディ・ダイオードは自然にコイル電流ILを転流します。この結果、S2のスイッチング波形は、図3に示すようにダイオード整流器を使った場合と似ています。逆回復による負の整流電流と、関連する電荷QRRも示します。これは、この論文で後述します。

図3. ボディ・ダイオードのデッドタイム導通と逆回復を含む同期整流器SRの波形。

図3. ボディ・ダイオードのデッドタイム導通と逆回復を含む同期整流器SRの波形。

デッドタイムは、余分な損失を引き起こすため、高効率が必要なときは慎重に管理しなければなりません。デッドタイムがゼロでないと、ボディ・ダイオードの電圧降下と逆回復の2つが原因で損失を引き起こします。eGaN FETは、シリコンMOSFETと比べて、ボディ・ダイオードの電圧降下が大きいですが、逆回復はありません [6]。80 VのFETでは、シリコンMOSFETのボディ・ダイオードの逆回復損失が支配的であることを示しています。この記事の焦点ではない低電圧では、ボディ・ダイオードの電圧降下が通常、損失に対して支配的で、SRと並列に低電圧ショットキー・ダイオードを使うか、デッドタイム管理によってeGaN FETのデッドタイム損失を軽減できます [ 5]。

逆方向電圧降下によるデッドタイム損失

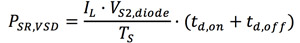

デッドタイム期間中、ボディ・ダイオードがコイル電流ILを流します。ILがほぼ一定でスイッチング周期がTSであると仮定すると、ボディ・ダイオードの電圧降下VS2,diodeによるデッドタイム損失は単純に、

となります。シリコンMOSFETにおいて、このボディ・ダイオードは、ドレインのエピタキシャル層とソースのウエルの間に形成されたPN接合で構成されます。このダイオードの順方向電圧降下は、標準的なシリコンの接合型ダイオードの順方向電圧降下VS2,diode、すなわち0.6~0.8 Vになります。.

eGaN FETの有効なボディ・ダイオードは、ゲートとソースが接続されたときに形成されます。負のドレイン-ソース間電圧VDSによって、ゲート電圧がドレイン電圧よりも高くなります。しきい電圧VTに達すると、チャネルは逆方向に電流を流し始め、ダイオード動作のように振る舞います。したがって、電圧降下は公称電流でのしきい電圧よりわずかに大きいため、VS2,diode≈2.5 Vです。

eGaN FETのVS2,diodeが大きいので、デッドタイムの導通損失がシリコンMOSFETのそれよりも大幅に大きくなります。これは、ショットキー・ダイオードの外付け、またはデッドタイム管理 [5] によって軽減できます。eGaN FETの高速性は、シリコンMOSFETの場合よりもはるかに短いデッドタイムにできますが、多くの古いPWMコントローラは、この機能に対応できません。

ただし、次のセクションでは、シリコンMOSFETにおいて、逆回復によって、ボディ・ダイオードの導通よりもはるかに大きな損失が生じる可能性があることを示します。これらの損失は、eGaN FETのボディ・ダイオードの導通損失をはるかに超えることがあります。

逆回復の概要

逆回復は主要な損失メカニズムですが、良いデータが欠如していることと分析が困難なために、しばしば無視されます [7]。ただし、これはスイッチング損失の主な原因であり、しばしば、他のすべてのスイッチング損失メカニズムよりも支配的になります。シリコンMOSFETを使うと、高性能が要求される場合は、逆回復損失に注意する必要があります。

逆回復は、PN接合ダイオードの現象です。ダイオードに順方向電流id=ILが流れると、少数キャリアの一群が接合部の空乏領域に注入されます。このキャリアの一群の数量はILの大きさに対応しています。さまざまな理由で、その大きさはidの変化よりも遅れ、時定数は遷移時間とキャリア再結合時間の両方に依存します [8],[9]。eGaN FETのボディ・ダイオードは、PN接合のない多数キャリアのデバイスであるため、逆回復は存在しません。

図4は、標準的な制御用スイッチS1のターンオン波形で、td,on の間にS2のボディ・ダイオードがILを流し始め、S1がILを流し終わると、S2のダイオードが完全にオフします。S1がオンすると、S1がILの増加部分を流すため、電流iS2は減少し始めます。制御用FETの電流がILに達すると、iS2=0となり、理想ダイオードはこの時点で導通を停止します。

図4. デッドタイムと逆回復を示す制御用スイッチS1のターンオン波形。参考のために整流器S2の電流波形を表示。

図4. デッドタイムと逆回復を示す制御用スイッチS1のターンオン波形。参考のために整流器S2の電流波形を表示。

少数キャリアの一群はidの変化に遅れているため、電流を流すために十分なキャリアがS2の空乏領域に残っています。言い換えると、このダイオードはオンのままで、貫通電流が発生します。これは逆回復電流とも呼ばれます。この電流はIRRMの最大値まで増加し、その時点で少数キャリアの一群は、電流をサポートできない点まで減少しています。その後、電流は、iS2=0および、iS1=ILになり、ダイオードがオフするまで時定数τRRで減衰します。全回復時間はtRRとして定義されます。

図4は、逆回復に関連する一般的なパラメータ、IRRM、mRR、QRR、tRR、およびτRRも定義しています。IRRM は回復電流のピーク値であり、負の整流器電流のピークの大きさと同じです。オン時の電流変化率はmRR、τRR は回復時定数、QRRとtRR はそれぞれ回復の電荷と時間です。逆回復の間、電荷QRRはバス電圧から供給されなければならないので、QRR によるスイッチング損失は、

シリコンMOSFETのデータシートには、非現実的な条件(mRR=100 A / µsと接合部温度Tj=25℃)でのQRRとtRRの数値が記載されています。実際には、QRRはIL、mRR、Tj、およびダイオードがオフする前にダイオードが導通していた時間の長さに大きく依存します。これらの依存関係は [8],[9] で説明されていますが、ここで重要なのは順方向導通時間td,onへの依存関係です。

デッドタイムが非常に短いと、QRRはゼロに近づきます。td,onが長くなると、接合部の少数電荷はILの関数である最大値まで増加し、それと共にQRRとtRRの両方が増加します。これによって、tRRとIRRMが減少し、SRでのQRR損失が減少します。td,onが空乏領域の電荷が最大値に達するための十分な長さになると、デッドタイムがさらに長くなってもQRR 損失は増えません。td,offの変化は、サイクルのこの部分で制御用FETはオフしたままで貫通状態が存在しないため、逆回復損失に影響を与えません。

残念ながら、逆回復パラメータの測定は難しく、誤りが発生しやすく、テストの設定に大きく依存します。これは、しばしば現実世界の動作とは異なります [7]。この事実は、使用可能な分析やモデリング・ツールの不足と相まって、逆回復損失の不十分なまたは存在しない測定につながります。ただし、この問題に対処する別の方法があります。

コンバータ損失対デッドタイムの関係をプロットすると、シリコンMOSFETのSRに2つの影響が見られます。ボディ・ダイオードの電圧降下によるデッドタイム損失は、全デッドタイム(td,on+td,off)に比例して直線的に増加します。逆回復によるデッドタイムの損失は、td,on~0で非常に小さく、td,onが増加するにつれて、これらの損失は、最初は急速に増加し、デッドタイムに比例してより遅い速度で増加します。最後に、td,offは逆回復に影響しません。eGaN FETは、全デッドタイムに対する線形依存性のみを示す必要がありますが、VS2,diodeが大きいため、傾きはシリコンMOSFETのSRよりも大きくなければなりません。

測定

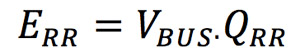

図5は、80 VのFET、L=4.7 μHを搭載し、300 kHz、48入力、12 V出力で動作するように設計された3つのバック・コンバータのパワー段です。これらは、レイアウトが同じで、異なるパワー・トランジスタを比べるために特別に設計されています [10]。中央のコンバータは、eGaN FET(EPC2021)を使い、他のコンバータは最先端のSi MOSFETを使っています。td,onとtd,offの値を変化させ、損失を測定しました。

図5. 80 Vのトランジスタを搭載した48 V入力、12 V出力のテスト・コンバータのパワー段:3.7 mΩのCanPAKTMのSi MOSFET(左)、1.8 mΩのeGaN FET(中央)とS308のSi MOSFET(右)。各基板の各辺は50 mmです。

図5. 80 Vのトランジスタを搭載した48 V入力、12 V出力のテスト・コンバータのパワー段:3.7 mΩのCanPAKTMのSi MOSFET(左)、1.8 mΩのeGaN FET(中央)とS308のSi MOSFET(右)。各基板の各辺は50 mmです。

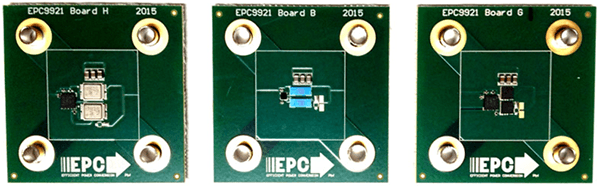

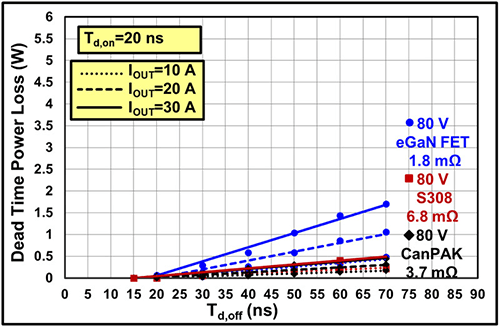

この記事では、デッドタイムの影響に関心があるため、最小のデッドタイムの場合がベースラインとして使われ、すべての損失の測定値から差し引かれます。これによって、デッドタイム効果による損失の定量化が可能になります。図6はこれらの結果です。td,onが長くなると、次のことが分かります。すなわち、Si MOSFETの場合、QRRによる損失の初期の増加が大きくなり、予想通り、VS2,diodeによる一定の傾きの漸近線に近づきます。eGaN FETの場合、予測通り、td,onの全範囲でVS2,diodeによる損失が一定の傾きの線をたどることが分かります。

図6a. eGaN FETおよび選択されたSi MOSFETを搭載した48 V入力、12 V出力、300 kHzのテスト・コンバータのオン時(上図)およびオフ時(下図)のデッドタイム損失。

図6a. eGaN FETおよび選択されたSi MOSFETを搭載した48 V入力、12 V出力、300 kHzのテスト・コンバータのオン時(上図)およびオフ時(下図)のデッドタイム損失。

図6b. eGaN FETおよび選択されたSi MOSFETを搭載した48入力、12 V出力、300 kHzのテスト・コンバータのオン時(上図)およびオフ時(下図)のデッドタイム損失。

図6b. eGaN FETおよび選択されたSi MOSFETを搭載した48入力、12 V出力、300 kHzのテスト・コンバータのオン時(上図)およびオフ時(下図)のデッドタイム損失。

eGaN FETの損失曲線の傾きは、逆方向ダイオードの導通時の電圧降下が大きいため、より大きくなります。傾きは大きくなりますが、Si MOSFETの初期の大きな損失は、大きなtd,onであっても、Si MOSFETの逆回復損失がeGaN FETの逆方向の電圧降下による損失をはるかに上回ることを意味します。td,offが増加すると、デッドタイムによる損失が線形に上昇することが分かり、予測通り、eGaN FETの傾きが大きくなります。オン時のeGaN FETの大きな利点は、Si MOSFETの小さなオフ時のデッドタイムの利点をはるかに上回ります。

拡大する可能性

この実験結果は、シリコン・ベースのパワーMOSFETの逆回復による大きな効率低下を示していることが明らかです。さらに、eGaN FETのデッドタイム制御に関する過去の議論では、デッドタイム管理またはショットキー・ダイオードを介してボディ・ダイオードの導通損失を管理する必要性に焦点を当ててきましたが、デッドタイム管理がSi MOSFETにとって、はるかに重要になる可能性があることがはっきりしました。

Si MOSFETは、スイッチング性能指数が非常に大きく、その結果、スイッチング遷移が遅いため、厳しい課題です。したがって、Si MOSFETの場合、スイッチング遷移のオーバーラップによるQRR損失を貫通損失に対してバランスをとるために、デッドタイムを慎重に最適化しなければなりません。この問題は、逆回復パラメータが温度と負荷電流に大きく依存するという事実によって厄介になります。スイッチング遷移のオーバーラップはデバイスの故障を加速する可能性が高いため、シリコンMOSFET用に設計されたほとんどのPWMコントローラは、逆回復損失を悪化させる長く最適でないデッドタイムを選択します。

eGaN FETの非常に速い遷移速度、および、逆回復から解放されることによって、非常に短いデッドタイムを使えるので、高い信頼性を維持しながら効率を高められます。GaNのエコシステムが拡大し続けるにつれて、GaNの可能性をさらに解放する新しいコントローラが利用可能になると期待しています。

参考文献

[1] R. W. Erickson and D. Maksimovic, Fundamentals of Power Electronics, Second. Springer, 2001, p. 912.

[2] R. Blanchard and R. Severns, “MOSFETs move in on low voltage rectification,” in Official Proceedings of the Ninth International PCI, 1984, vol. 84, pp. 29–31.

[3] D. Reusch and J. Glaser, DC-DC Converter Handbook - A Supplement to GaN Transistors for Efficient Power Conversion, 1st ed. Power Conversion Publications, 2015, ISBN 978-0-9966492-0-9.

[4] J. Glaser, J. Strydom, and D. Reusch, “High Power Fully Regulated Eighth-brick DC-DC Converter with GaN FETs,” in PCIM Europe 2015; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management; Proceedings of, 2015, pp. 406–413.

[5] J. Strydom and D. Reusch, “eGaN® FET-Silicon Power Shoot Out Volume 12: Optimizing Dead Time,” Power Electronics - Penton Electronics Group, Jan. 2013.

[6] A. Lidow, J. Strydom, M. de Rooij, and D. Reusch, GaN Transistors for Efficient Power Conversion, 2nd ed. Wiley, 2014, ISBN 978-1-118-84476-2.

[7] C. Mößlacher and O. Guillemant, “Improving Efficiency of Synchronous Rectification by Analysis of the MOSFET Power Loss Mechanism,” Infineon Technologies, Mar. 2012.

[8] X. Kang, A. Caiafa, E. Santi, J. L. Hudgins, and P. R. Palmer, “Parameter extraction for a power diode circuit simulator model including temperature dependent effects,” IEEE Applied Power Electronics Conference and Exposition (APEC), March 2002, Vol. 1, pp. 452–458.

[9] P. O. Lauritzen and C. L. Ma, “A simple diode model with reverse recovery, ”Power Electronics, IEEE Transactions on, vol. 6, no. 2, pp. 188–191, Apr. 1991.

[10] D. Reusch, J. Strydom, and A. Lidow, “Thermal Evaluation of Chip–Scale Packaged Gallium Nitride Transistors,” IEEE Applied Power Electronics Conference and Exposition (APEC), March 2016, pp. 587–594.