宇宙用DC-DC設計にGaNを採用する理由

GaNの話 – David Reusch, Ph.D.

3 03, 2021

パワー・エレクトロニクスの技術者は常に、高い信頼性を維持し、コストを最小限に抑えながら、より高い効率とより高い電力密度が得られる設計に取り組んでいます。設計技術の進歩と部品技術の向上によって、技術者は、これらの目標を終始一貫して達成することができます。パワー半導体は、これらの設計の中核であり、それらの改善は、より良い性能に不可欠です。このEPCの宇宙のブログでは、GaNパワー半導体が宇宙用途の過酷な放射線環境での革新を可能にする方法を示します。

GaNパワー半導体は、高信頼性市場の設計者に、前任者であるシリコンのパワーMOSFETと比べて、電気的性能の急激で大幅な改善を提供します。表1は、回路設計者がコンバータの効率と電力密度を向上させるために重要な放射線耐性を強化したGaNとSiのパワー半導体デバイスの特性の比較です。

|

|

200 V GaN FBG20N18B

|

200 V Si MOSFET

|

技術比較

|

|

VDS (V)

|

200

|

200

|

同じ

|

|

RDS(ON) (mΩ)

|

26

|

28

|

ほぼ同じ

|

|

面積 (mm2)

|

23

|

237

|

1/10に削減

|

|

QG (nC)

|

6

|

240

|

1/40に削減

|

|

QGD (nC)

|

2

|

60

|

1/30に削減

|

|

QGS (nC)

|

2

|

70

|

1/35に削減

|

|

COSS (pF) @50 V VDS

|

300

|

900

|

1/3に削減

|

|

COSS (pF) @1 V VDS

|

950

|

10000

|

1/10に削減

|

|

QRR (nC)

|

0

|

11700

|

無限の削減

|

|

VSD (V)

|

1.75

|

1.2

|

1.5倍

|

表1:耐放射線特性を強化したGaNとSiのパワー半導体デバイスの特性の比較

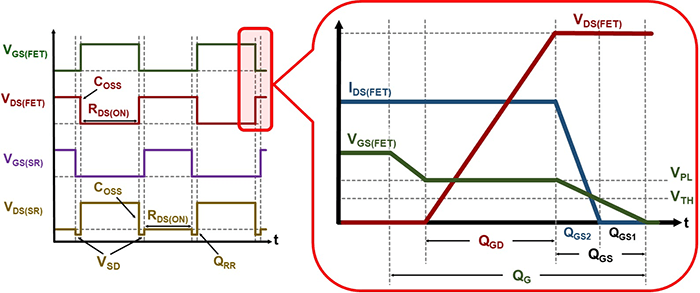

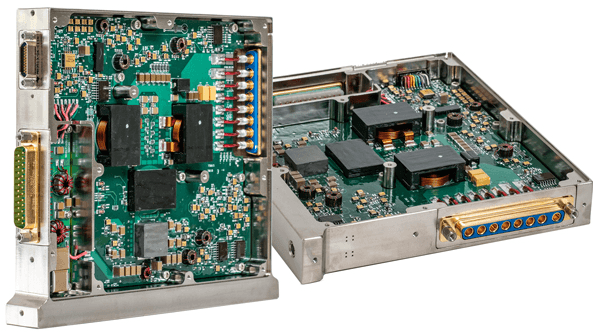

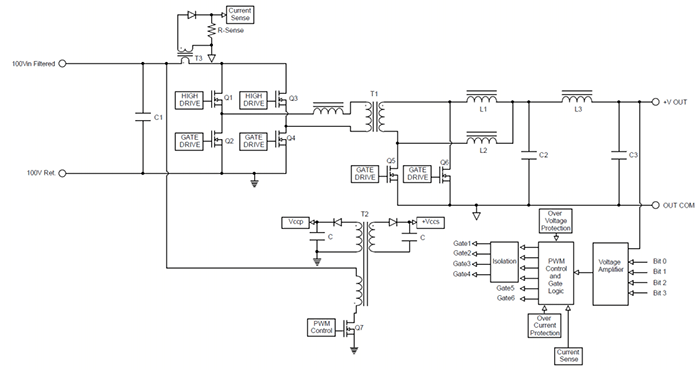

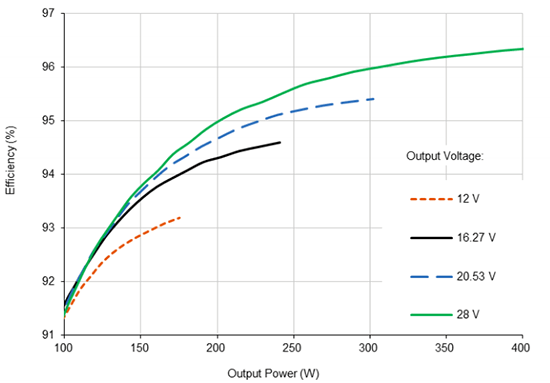

表1の比較は、新しいパワー半導体技術の利点を明確に示していますが、これが、パワー半導体がより大きなシステムの一部である実際の回路性能に、どのように貢献するかを見積もることは困難です。図1のパワー半導体転流図を使って、これらのデバイス特性がコンバータの性能に与える理論的影響を説明し、図2に示す米VPTのDC-DCコンバータSGRB10028Sを使った革新的な実際の製品設計への影響を説明します。SGRB10028Sは、入力100 V、調整可能な12 V〜28 Vの単一出力、最大出力電力400 W、および96%を超える効率が得られます。SGRBコンバータは、1次側デバイスと2次側同期整流器の両方にGaNデバイスを使った位相シフトのフルブリッジ回路構成を採用しています。

図1:ハード・スイッチの同期整流型パワー・コンバータの理想的な波形と損失メカニズム

図1:ハード・スイッチの同期整流型パワー・コンバータの理想的な波形と損失メカニズム

始めます。VDSは、図1に示すオフ状態のドレイン-ソース間電圧を十分なマージンでサポートするために、十分な大きさでなければなりません。これには、主に回路の寄生インダクタンスによって誘起される回路の電圧リンギングも含まれます。ブロッキング電圧のほとんどは、絶縁トランスの漏れインダクタンスのスパイク、設計の入力電圧と出力電圧に依存します。したがって、GaNとSiの設計では、電圧ストレス、すなわち、最大ドレイン-ソース間ブロッキング電圧は同じになります。

デバイスのオン状態のドレイン-ソース間抵抗RDS(ON)は、導通損失を決めます。この設計例では、大電力需要に対応するために大電流が必要であり、利用可能な最小のオン抵抗のデバイスが選択されています。これらの設計例は、それぞれ26 mΩと28 mΩのGaNパワー半導体とSiパワー半導体の間でほぼ同じです。オン抵抗は、ほぼ同じですが、パワー半導体に必要なデバイス面積とプリント回路基板のスペースは大きく異なります。GaNパワー半導体はSi MOSFETの約1/10のサイズです。この設計では、図2に示すように、GaNパワー半導体が設計の片面の基板スペースの約5〜10%を占めています。設計者が10倍大きいSi MOSFETを使う必要がある場合、占有される基板スペースは50%以上に跳ね上がります。これは、他の部品、特に磁気部品の設計に大きな影響を与え、部品を小さくし、統合された磁気部品の使用の制限になります。これらは両方とも、損失を増加させ、コンバータの効率を低下させます。このような利点は、表1と図1には示されていませんが、システム特性に大きな影響を与えます。

デバイスのサイズが小さくなると、設計の熱的なボトルネックにならないように、損失を比例して減らす必要があります。表1の残りの部分は、スイッチング・サイクル中に発生するスイッチング関連損失に関するものです。ゲート電荷QGは、図1に示すように、デバイスをオンにするために必要な電荷の合計量です。GaNデバイスの場合、QGはSiデバイスの1/40と小さいため、ゲート駆動損失が小さくなります。ゲート駆動損失が小さいことのもう1つの利点は、補助電源に必要な電力が削減されることです。補助電源は、多くの場合、大きな基板スペースを占有し、無視できない電力損失があります。ゲート-ドレイン間電荷QGDは、しばしばミラー電荷と呼ばれ、図1に示すように、電圧転流中の電荷量です。GaNデバイスの場合、QGDはSiデバイスの1/30と小さいため、電圧転流損失が小さくなります。ゲート-ソース間電荷QGSは、図1に示すように、デバイスのしきい値電圧(QGS1)に到達し、ミラー・プラトー電圧(QGS2)に上昇する電荷量です。GaNデバイスの場合、QGSがSiデバイスの1/35と小さいので、図1のQGS2のタイミングで発生する電流転流損失が減少します。出力容量COSSは、ドレイン-ソース間容量とゲート-ドレイン間容量の合計です。COSSは、スイッチング・サイクルごとに放電またはソフト転流しなければなりません。GaNデバイスの場合、高電圧(50 V)および低電圧(1 V)のブロッキング電圧に対して、COSSは、それぞれSiデバイスよりも1/3、および1/10に小さくなっています。ハード・スイッチング用途では、出力容量の損失はVDS2に関連し、より高いブロッキング電圧での出力容量条件がより重要になります。ソフト・スイッチングが一般的にVDSに関連して実現されるソフト・スイッチング用途は、より低いブロッキング電圧で発生する大きな出力容量値が重要になります。設計の回路構成に関係なく、GaNデバイスはCOSS関連の損失が小さくなります。逆回復電荷QRRは、MOSFET が電圧をブロックする前に放電しなければならないMOSFETのボディ・ダイオードに蓄積された電荷であり、同期整流器(SR)の主な損失源です。少数キャリアがなく、QRRがゼロの GaNデバイスの場合、逆回復損失はSiデバイスよりも無限に小さくなります。ソース-ドレイン間の順方向電圧VSDは、MOSFETのボディ・ダイオードの順方向電圧として知られ、同期整流デバイスがオフで電流を流す必要があるときの導通電圧であり、図1に示すように、一般的には制御デバイスがオンになるまでの短いデッドタイムです。GaNデバイスの場合、順方向導通損失はSiデバイスの1.5倍です。これらの損失メカニズムのそれぞれの詳細な重み付けはアプリケーションに依存し、このブログの範囲を超えていますが、アプリケーションに関係なく、GaNはSi MOSFETと比べて、電荷/容量が大幅に小さく、関連する損失も大幅に小さくなります。図2に示す設計の場合、GaNパワー半導体の損失は、Si MOSFETのわずか1/10と十分小さく、システムの熱的ボトルネックではありません。この成果は、優れたパワー半導体なしでは実現できません。

(a)

(a)

(b)

(b)

(c)

図2:米VPTのDC-DCコンバータSGRB10028Sの (a) ハードウエア、(b) 回路構成、 (c) VIN=100 Vでの効率

(c)

図2:米VPTのDC-DCコンバータSGRB10028Sの (a) ハードウエア、(b) 回路構成、 (c) VIN=100 Vでの効率

高度なGaNパワー半導体と最先端の設計技術を組み合わせることで、図2に示すように、高信頼性の宇宙設計で新しいレベルの性能を実現できます。米VPTのSGRBシリーズは、高効率、低雑音、放射線耐性が不可欠な宇宙通信向けに特別に設計されています。SGRB シリーズは、高度なGaNベースの技術を使って、電源効率を向上させ、システムの大きさ、重さ、コストを削減するソリューションを提供するために開発されました。このGaNベースのSGRBシリーズのDC-DCコンバータは、最高の栄誉であるMilitary & Aerospace Electronics Innovators Awardsのプラチナ認定を獲得しました。この賞は、設計上の課題を解決するための画期的な貢献と革新的なソリューションを提供した航空宇宙および防衛エレクトロニクスの業界の企業を認定しています。