Alex Lidow博士、CEO(最高経営責任者)、Efficient Power Conversion Corporation

過去30年間、パワーMOSFETの構造、技術、回路構成における革新が、私たちの日常生活の中での電力へのニーズの高まりに歩調を合わせてきたように、パワー・マネージメント(電源管理)の効率とコストは、着実に改善しています。しかし、シリコン・パワーMOSFETは、その理論的な限界に漸近してきているので、ここ数年、改善率が鈍化してきています。

シリコンのパワーMOSFET:30年の旅

パワーMOSFETは、バイポーラ・トランジスタの代替として、1976年に初めて出てきました。これらの多数キャリア・デバイスは、より速く、より丈夫で、少数キャリアの対応デバイスよりも高い電流利得が得られました。この結果、スイッチング電力変換の商用化が現実的なものになりました。初期のデスクトップ・コンピュータ用のAC-DCスイッチング電源は、パワーMOSFETの最も初期の大量消費製品の1つで、その後、可変速モーター駆動、蛍光灯、DC-DCコンバータ、および、私たちの日常生活で当たり前になった他の多くのアプリケーションが続きました。

最も初期のパワーMOSFETの1つは、米インターナショナル・レクティファイアー社が1978年11月に製品化したIRF100でした。ドレイン-ソース間の耐圧を100 Vに高め、オン抵抗は0.1Ω:この;時代のベンチマークでした。チップ面積は40 mm2を超え、価格は34米ドルでした。この製品は、由緒あるバイポーラ・トランジスタを、すぐに広く置き換えるように運命づけられていたわけではありません。

パワーMOSFETの多くの世代が、長年にわたって、いくつかのメーカーによって開発されてきました。30年以上の間、毎年のようにベンチマークが設定され、実現されました。この記事の執筆時点で、100 Vのベンチマークは、おそらく、独インフィニオン社のIPB025N10N3Gが保持しています。IRF100の4Ω-mm2の性能指数FOM(figure of merit)と比べて、IPB025N10N3GのFOMは、0.1Ω-mm2以下です1)。つまり、ほぼシリコン・デバイスの理論上の限界にあります2)。

行うべき改善は、依然としてあります。例えば、CoolMOSデバイスやIGBTは、単純な縦方向多数キャリアのMOSFETの理論的な限界を超える導電率の向上を実現しています。これらの技術革新は、まだ、かなりの時間継続するかもしれません。そして、何年か後、それらの電力変換の回路やシステムから得られるすべてを絞り出すことを学んだ知識の豊富な設計者にとって、および、パワーMOSFETの低コスト構造にとって、ある程度貢献するでしょう。

GaNの旅の始まり

HEMT(高電子移動度トランジスタ)のGaNトランジスタは、日本のユーディナデバイス社によってディプリーション・モードのRFトランジスタとして2004年頃に初めて製品化されました。SiC(炭化ケイ素)基板上のGaNを使って、ユーディナ社は、RF市場向けに設計されたトランジスタを製造することができました3)。このHEMT構造は、1975年に三村 高志氏ら4) によって初めて、1994年にはM. A. Khan氏ら5) によって、この現象が説明され、これは、AlGaNとGaNのヘテロ構造の境界面の間の境界付近で異常に高い電子移動度を示しました。この現象を炭化ケイ素上に成長させた窒化ガリウムに応用して、ユーディナ社は、マルチギガヘルツの周波数範囲でベンチマークとなる電力利得を実現することができました。2005年、米Nitronex社は、同社のSIGANTIC®技術7) を使って、シリコン・ウエハー上にGaNを成長して作った最初のディプリーション・モードのRF HEMTトランジスタを製品化しました。

GaNのRFトランジスタは、いくつかの他の企業が市場に参入してきたように、RF用途に浸透し続けてきました。しかし、この市場以外での採用は、ディプリーション・モード動作の不便さと、デバイス・コストによって制限されていました。

図1:GaNオン・シリコンのデバイスは、横型DMOSデバイスに似た非常に単純な構造で、標準的なCMOSファウンドリーで製造することができます

2009年6月、Efficient Power Conversion Corporation(EPC)は、パワーMOSFETの代替品として特別に設計されたエンハンスメント・モードGaNオン・シリコンのパワー・トランジスタを初めて製品化しました。これらの製品は、シリコンの標準的な製造技術や設備を用いて、低コストで大量に生産できるように設計されました。この構造は、図1に示すように比較的単純です。

障壁を破る

30年間のシリコン・パワーMOSFETの旅は、この破壊的技術の採用率を制御する以下4つの重要な変数があったことを私たちに教えてくれました。

- それは、重要な新しい機能を可能にしますか?

- それは、使いやすいですか?

- それは、ユーザーにとって費用対効果が非常に高いですか?

- それは、信頼性がありますか?

次の数セクションでは、これらの4つの基準のそれぞれに基づいて、GaNオン・シリコンのパワー・トランジスタが支配的なシリコン・パワーMOSFETを破壊するための準備状況を検討します。次に、近い将来の開発を見据えて、電力変換業界へのそれらの影響を推定します。

GaNパワー・トランジスタによって可能になった新しい機能

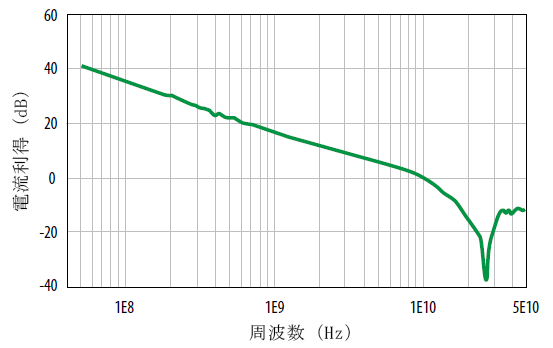

エンハンスメント・モードGaN HEMTデバイス(eHEMT)によって可能になった最も重要な新しい機能は、スイッチング特性と全体的なデバイスの帯域幅の破壊的な改善に由来します(図2参照)。GaNは、シリコンよりも非常に大きな臨界電界も備えているため、この新種のデバイスは、オン抵抗に対するごくわずかな犠牲を払って、ドレイン-ソース間の非常に大きな電圧に耐えることができます。

図2:EPCのエンハンスメント・モードGaNパワー・トランジスタの周波数対利得の関係

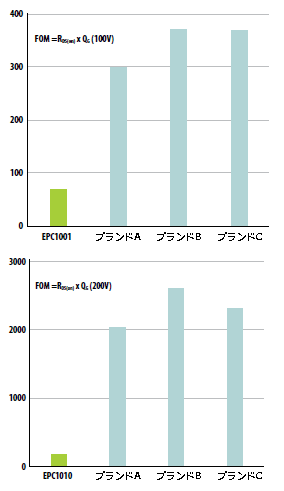

図3:定格100 Vと200 VのシリコンのベンチマークとGaNに対するRQ積の比較

パワーMOSFETでは、部品の導電率と、デバイスをオン状態からオフ状態(または、オフ状態からオン状態)にするために必要な電荷量との間に基本的なトレードオフが存在します。このトレードオフから、RQ積と呼ばれる性能指数FOMが重要視されます。これは、動作時の電圧と電流において、デバイスをスイッチングするためにゲートに供給されなければならない全電荷量とデバイスのオン抵抗との積として定義されます。この積の改善は、高周波DC-DCコンバータにおける変換効率の向上につながることが示されています。RQ積の絶対値は、実際の回路で達成可能な最小パルス幅の指標でもあります。過去数年にわたって、RQ積が大きく改善されていますが、シリコンは、すでに市場に出回っている第1世代eHEMTデバイスが達成できたFOMに近づくことができません。図3に、定格100 Vと200 Vのシリコン・デバイスのベンチマークとGaNデバイスとの間の比較を示します。

DC-DCコンバータ

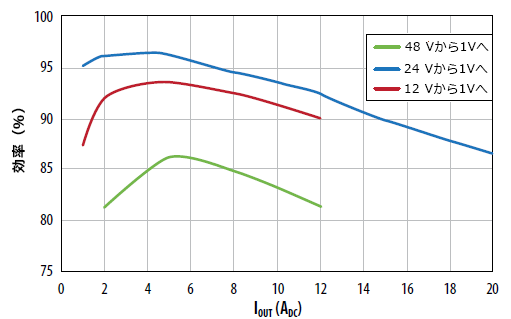

大きな電力損失がなく、高速にスイッチングする能力は、電力変換回路では、はるかに短いパルス幅を実現できることを意味します。この能力を必要とする1つの重要な新しいアプリケーションは、非絶縁型DC-DCコンバータです。シリコン・パワーMOSFETの基本的な限界は、1段の非絶縁型バック・コンバータの入力電圧に対する出力電圧の実質的な最大比を10対1に制限することです。この比率を超えると、降圧回路において上側のトランジスタに要求される短いパルス幅は、許容できないほど大きなスイッチング損失、および、この結果としての低い変換効率をもたらします。図4と5に示すように、GaNトランジスタは、この特性の水準を完全にリセットします。

図4:さまざまな入力電圧に対するバック・コンバータの効率対電流の関係。このコンバータは、上側と下側の各1個の100 Vのトランジスタ(いずれもEPC1001)で構成されています。10対1よりも大きな比率は一般的に、シリコン・デバイスでは非現実的と考えられています。

図5a:バック構成にトランジスタEPC1001を使ったとき、300 kHzでの48 Vから1 Vへの変換

図5b:1.5 MHzでの48 Vから1 Vへの変換

図5c:48 Vから0.5 Vへの変換

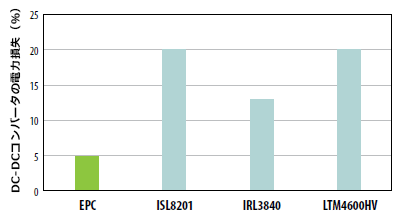

図6:3種類の一般的なPOLコンバータにおいて、Vin = 12 V、Vout = 1 Vで、5 A、600 kHzのときの電力損失と、GaNトランジスタのEPC1014/ EPC101で構成したコンバータの電力損失との比較。

GaNによって可能になったVIN/VOUT範囲の拡大に加えて、既存のバック・コンバータでは、いかなるVIN/VOUTにおいてもスイッチング損失を大幅に低減することができます。 この大幅な改善を示す12 Vから1 Vへのコンバータでの比較が図6です。

新しいGaNトランジスタが急速に、現在のパワーMOSFETとIGBTの電流と電圧の範囲をカバーできるようになったので、AC-DC変換、同期整流、力率改善はすべて、主な特性改善のための候補です。

D級オーディオ

D級オーディオ・アンプは常に、コスト、サイズ、および、サウンドの歪みの間のトレードオフに直面しています。

歪みに対して最も重要な要因は、デッドタイムと、出力フィルタの位相シフトです。

デッドタイムに基づいて出力パルス幅が変化する3つの異なる動作モードがあります。正のコイル電流での転流はハイサイド・スイッチに基づいており、負のコイル電流での転流はローサイド・スイッチに基づいており、双方向電流での転流は各スイッチに基づいています。これらは、立ち上がりエッジ、降下エッジ、または、何もないときのデッドタイムを決めます。

デッドタイムの長さは、この現象に依存する歪みを決めます。有限のスイッチング速度とボディ・ダイオードの順方向電圧が、この効果に加わります。エンハンスメント・モードGaNトランジスタはゲート電荷が極めて小さいので、非常に短い遅延時間と非常に高速なスイッチング速度に貢献します。スイッチングの精度があると、スイッチング現象をよりうまく制御できるので、歪みの低下につながるデッドタイムの短縮を可能にします。

出力フィルタのサイズと帰還の利得は、スイッチング周波数によって決まります。低い周波数では、所望の信号から搬送波周波数を十分に除去するために、フィルタのコンデンサとコイルは、大きな値にしなければなりません。大きな値のフィルタ部品は、アンプのコストとサイズを大きくするだけでなく、位相シフトも引き起こします。これは、システムの安定性を低下させ、歪み成分の多くを補償するために使われる帰還利得を制限するので、システムの忠実度を制限します。従来のシリコンMOSFETを使うと、スイッチング損失が大きいので、消費電力が急激に上昇するため、周波数が制限されます。

GaNトランジスタは、オン抵抗RDS(ON)とゲート電荷QGが両方とも小さいので、マルチメガヘルツの範囲で十分優れた効率が得られます。したがって、歪みに対するスイッチング・アンプの寄与を低減するための大きな利得の帰還が可能になるだけでなく、アンプには、コスト、サイズ、歪みを低減する小さい値のフィルタ部品を使うことができます。

したがって、エンハンスメント・モードGaNトランジスタは、D級アプリケーションの忠実度とコストの両方を大幅に改善する可能性を秘めています。

エンハンスメント・モードのGaNトランジスタは、使いやすいですか?

デバイスをいかに簡単に使いこなせるかは、ユーザーのスキル、開発中の回路の難易度、ユーザーが経験のあるデバイスと比べて、そのデバイスがどう違うか、および、ユーザーがそのデバイスを適用する助けとなるツールを利用できるか、に依存します。

エンハンスメント・モードGaNトランジスタの新しい世代は、既存のパワーMOSFETと振る舞いが非常に似ているので、ユーザーは過去の設計経験をうまく活用することができます。特別な注意を必要とするものとして、2つの主な領域があります。すなわち、比較的低いゲートの絶縁耐力(ゲート幅の1 mm当たりのマイクロ・アンペア・オーダーでの有限のゲートの漏れ)と比較的高い周波数応答です。技術が成熟するにつれて、これら2つの違いの1つである比較的低いゲート絶縁耐力は、改善されるでしょう。その間に、作業場のESD(静電気容量)を排除するために、そして、データシートの最大値8)を下回るVGSを維持する回路を設計するために、対策が取られる必要があります。2番目の相違点である比較的高い周波数応答は、いかなるシリコン・デバイスをも上回るステップ関数の改善と、回路をレイアウトするときのユーザーの更なる配慮の両方が必要になります。例えば、寄生の小さな浮遊インダクタンスは、潜在的にデバイスにダメージを与えるゲート-ソース間電圧の大きなオーバーシュートを引き起こす可能性があります。

一方、これらのデバイスを、前任者であるシリコンよりも簡単に使えるようにする特性がいくつかあります。例えば、しきい電圧は、広範囲にわたって実質的に温度と独立であり8)、オン抵抗の温度係数は、シリコンよりも非常に小さいことです8),9)。

GaNトランジスタは300℃の高温で正常に動作することもできますが、プリント回路基板へのはんだ接続は、実際のアプリケーションでは125℃以上にすることはできません。したがって、最初の商用のエンハンスメント・モードの部品は、単に最大125℃までで定格化されています。

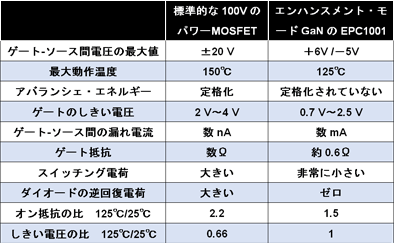

表1

表1は、シリコン・パワーMOSFETとGaNトランジスタEPC1001との間の基本的な特性を使いやすさの観点から詳しく比較したものです。

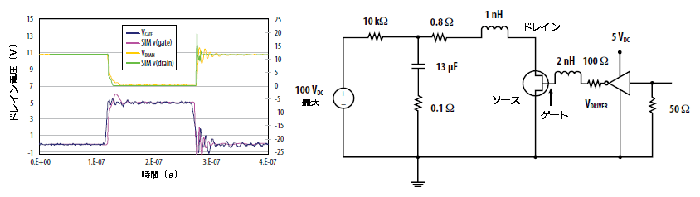

ユーザー・フレンドリーなツールも、新しいタイプのデバイスに、いかに簡単に応用できるか、で大きな違いがあります。EPCは、ユーザーがダウンロードして利用できるTSPICEデバイス・モデルの完全なセットを開発しています10)。図7は、簡単な回路、および、実際のデバイス特性とTSPICEモデル使ってシミュレーションした結果との比較です。これらのモデルを改良する多くの作業が行なわれる必要がありますが、第1世代は、エンジニアの生産性の向上、および、市場に製品を導入する時間を短縮することができる合理的で信頼性の高い回路特性の予測を提供しなければなりません。

アプリケーション・ノートと設計のヒントは、長年にわたってエンジニアが集めた経験を体系化しています。何1000本ものアプリケーション・ノートが何100ものアプリケーションで使われるパワーMOSFETについて記述され、利用可能です。GaNのユーザーがこの知識の体系に追い付くには何年もかかるでしょうが、エンハンスメント・モードGaNトランジスタとシリコン・パワーMOSFETの間の類似性によって、この作業の多くは、応用し続けられます。GaNの並外れた特性を最大限に活用するために、ユーザーに知識を与えるアプリケーション・ノートも、複数の情報源から利用可能になりつつあります11),12)。

図7:EPC1001のTSPICEシミュレーション結果と実際に測定された回路特性とを比較したオシログラムと回路図

それはユーザーにとってコスト効率が極めて高いですか?

異なる技術による製品の間のコスト比較には、注意が必要です。加えて、需要と供給の不均衡がある場合、コストが常に製品価格に反映されるわけではありません。GaNパワー・トランジスタの市場は、開発の非常に初期の段階であるため、最も意味のある情報は、シリコン・パワーMOSFETと、市場に出ている第1世代のエンハンスメント・モード・トランジスタとの間のコスト比較です。

製品コストの基本的な要素は、以下のようになります。

- 出発物質

- エピタキシャル成長

- ウエハー製造

- テストとセンブリ

歩留り、エンジニアリング・コスト、梱包、輸送コスト、および一般的な間接費などのようなコストに寄与するこの他の要素は、この分析の目的から、同じであると仮定します。

出発物質:

パワーMOSFETでは、この事業をする多くのメーカーが100 mmから200 mmの間の基板で生産していますが、GaNオン・シリコンのデバイスは一般に、150 mmの基板で生産されています(将来の製品は200 mmに移行します)。GaNデバイスは、標準的なシリコン基板を使っているので、同じような直径の出発物質で製造されたパワーMOSFETと比べて、コストでのペナルティはありません。実際には、150 mmと200 mmのシリコン・ウエハーの間の単位面積当たりのコストの差はわずかなので、出発物質に関する限り、ウエハー当たりの真のコストの差はない、と結論することができます。GaNデバイスは、同様の電流処理能力を備えたシリコン・デバイスよりもデバイス面積が小さいという事実を考慮すると、機能当たりのコストは、GaNの方が低くなります。

エピタキシャル成長:

シリコンのエピタキシャル成長は、非常に効率的で自動化された装置を作っている多くの企業では成熟した技術です。GaNのMOCVD装置は、少なくとも2つの供給元、すなわち、米ビーコ社13) と独アイクストロン社14) から入手可能です。両社とも、能力が高く信頼性の高い装置を作っており、その主な用途は、発光ダイオード(LED)の製造に使われるGaNのエピタキシャル成長です。いずれの装置も、シリコン上のGaNのエピタキシャル成長には最適化されておらず、シリコンの装置に共通する自動化レベルも備えていません。この結果、シリコン上のGaNのエピタキシャル成長は、今日のシリコンのエピタキシャル成長よりもかなり高価です。

しかし、これは、本質的ではありません。処理時間と温度、ウエハー直径、材料費、装置の生産性はすべて、シリコンの制限から遠く離れた基本的な制限はなく、改善の高速軌道に乗っています。今後数年以内に、シリコン・パワーMOSFETの代替として、GaNが広く採用されることを仮定すると、GaNのエピタキシシャル成長のコストは、シリコンのエピタキシャル成長のコストに近づくことが期待されます。

ウエハー製造:

図1に示した単純な構造を、標準的なシリコン・ウエハー工場において製造することは、複雑ではありません。処理温度は、シリコンCMOSと似ており、相互汚染は容易に管理することができます。今日、EPCは、台湾にある十分に確立されたファウンドリーであるEpisil社で、すべてのウエハーを処理しています。

GaNパワー・デバイスとパワーMOSFETのウエハー製造コストの間に大きな違いはありません。

テストとアセンブリ:

テストのコストが同等であることに対し、アセンブリ工程では、GaNオン・シリコン・デバイスのコスト構造が有利であり、大きな違いがあります。

シリコン・パワーMOSFETは、標準的には銅のリードフレーム、いくらかのアルミニウム、金、または銅のワイヤーで作られたパッケージで包み込まれ、すべてエポキシで成形され封止されなければなりません。接続は、縦型シリコン・デバイスの表面と裏面に作らなければならず、アクティブ・デバイスに侵入する湿気のためにプラスチック成形が必要で、部品から熱を取る手段が必要です。

SO-8、TO-220、D-PaKなどの伝統的なパワーMOSFETのパッケージは、コストと、電気抵抗や熱抵抗を大きくし、製品への信頼性と品質のリスクを増大させます。

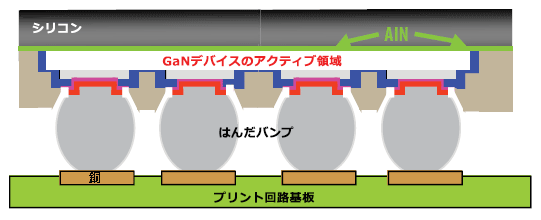

GaNオン・シリコンは、電気的、熱的、または信頼性特性を損なうことなく、「フリップ・チップ」として使用することができます。

図8:GaNオン・シリコンは、「フリップ・チップ」として使用することができます。このアクティブ・デバイスは、シリコン基板から絶縁され、チップに分離する前に完全に包み込むことができます。

図8から、アクティブ・デバイス領域がシリコン・オン・サファイアのデバイスのように、シリコン基板から絶縁されていることが分かります。この結果、アクティブGaNデバイスは、パッシベーション層によって完全に包み込むことができます。加えて、シリコン基板は、優れた熱特性を得るためにヒートシンクに直接、取り付けることができます。

要するに、GaNオン・シリコンは、パッケージが不要になり、したがって、コスト、余分な基板スペース、熱抵抗と電気抵抗の増加を排除し、パッケージに封止されたパワー・デバイスで最も一般的に悩まされる信頼性の問題も排除します。

表2

表2に、2010年の単位面積当たりのシリコン・パワー・トランジスタとGaNオン・シリコンと間のコスト差の比較と、その2015年の予測をまとめました。GaNオン・シリコン・デバイスは、同じ機能に対して小さな面積で済むので、全体としての結論は、この表が示すよりも、もっとGaNに有利になるでしょう。

GaNの信頼性は高いですか?

シリコン・パワーMOSFETで利用可能な蓄積した信頼性情報は、揺らいでいます。長年にわたる努力は、任意の電力変換システムの信頼性の高いバックボーンとして各々が区別してきた故障メカニズムの理解、制御と修正の工程、製品の設計という方向に向かっています。GaNオン・シリコンのトランジスタは、まだ、この旅を始めたばかりです。しかし、暫定的な結果は、有望です。米Nitronex社は、その品質テストからの結果を発表し15)、デバイスが多くのRFアプリケーションにうまく適用され、良い結果だったとしています。

この記事の執筆時点で、EPCは、エンハンスメント・モードGaNオン・シリコンのトランジスタの基本的な能力を確立しています。完全な信頼性レポートは、https://epc-co.com/epc/jp/設計サポート/eGaNFETの信頼性.aspxに掲載されています。

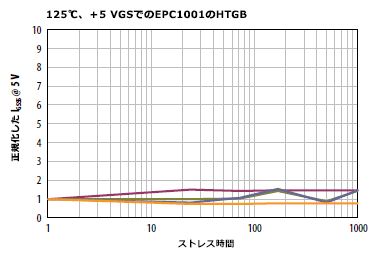

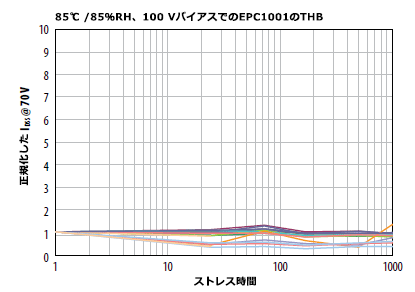

図9:125℃、+5 Vgsにおける1000時間のゲート・ストレスの能力

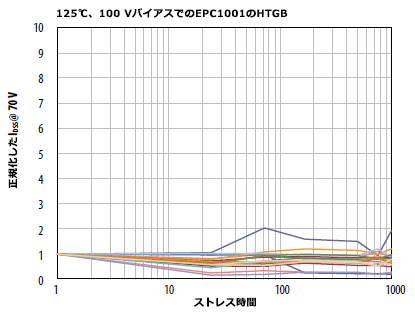

図10:125℃、100 V

DSにおける1000時間のドレイン-ソース間ストレスの能力

図11:100 V

DS、アンダーフィルなしで、85%RH、85℃における1000時間の湿度ストレスの能力

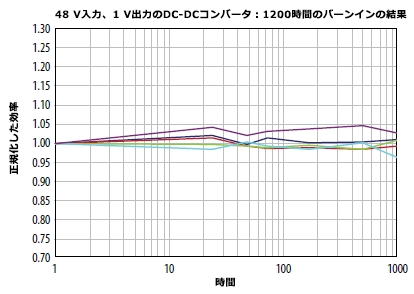

図12:周囲温度40℃、10 Aで2個のGaNトランジスタEPC1001を使ったDC-DCコンバータの1000時間バーンインの結果

デバイスの中間結果を図9、10、11に示します。図から分かるように、テストされたデバイスは、ゲート、ドレイン-ソース間に1000時間のストレスを与え、バイアスと共に高い湿度に曝された後でも安定でした。

EPCは、デバイスを48 V入力、1 V出力のDC-DCコンバータにも搭載し、1000時間の最大ストレスでそれらを動作させても、故障はありませんでした(図12)。

この新しい技術に関連するさまざまな故障メカニズムを理解するためにしなければならない多くのことがあります。この分野へのすべての参入者は、この知識体系に大きく貢献したいと思っています。それにもかかわらず、私たちが持っているデータは、これまでのところ、この技術が今日、商用アプリケーションの信頼性の許容レベルで動作可能であることを示唆しています。

将来の方向性:

GaNの旅は始まったばかりです。RQ積の性能指数FOMによって評価されたように、基本的なデバイス特性で実現できる大きな改善があります。私たちは、材料やプロセスについてもっと学ぶことによって、今後3年間で2倍の改善は当然であり、今後10年間の改善は10倍になるでしょう。

近い将来には、一段と高い耐圧のデバイスが出現することも期待できます。この分野では、他の企業は、彼らの意向をオープンに議論しています16)。間違いなくGaNトランジスタの高耐圧化は続き、より低い製造コストとより低い導通損失によって、シリコンIGBT、そしてSiCトランジスタでさえ、置き換えるでしょう2)。

おそらく、電力変換システムの特性に影響を与えるためのGaNの最高の機会は、同一基板上に、パワー・レベルと信号レベルの両方のデバイスを集積化できる固有の能力から生まれます。GaNオン・シリコン、そしてSOIのようなデバイスは、部品の間に大きな寄生の相互作用がないため、設計者は、簡単に単一チップ上にモノリシックのパワー・システムを開発することができます。

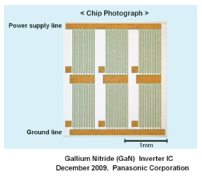

図13、14、15に、すでに製造されたさまざまな集積化したデバイスを示します。図13は、パナソニックが開発した6個のパワー・トランジスタを集積した3相モーター制御用ICで、回路基板上にICドライバなども搭載しています。図14は、EPCのフルブリッジ•パワー・デバイスで、図15は、EPCのパワー・トランジスタで、回路基板にドライバを搭載しています。

結論:

パワーMOSFET開発の1970年代後半のパイオニアは、バイポーラ・トランジスタを完全に置き換える技術を持っていると信じていました。30年後、まだ、パワーMOSFETよりもバイポーラ・トランジスタの方が有利な多くのアプリケーションがありますが、パワーMOSFETの市場規模は、画期的な技術によって可能になるすべての新しいアプリケーションや新しい市場に大きく依存するバイポーラ市場よりも何倍も大きい市場です。

図13:制御機能とエンハンスメント・モードGaNパワー・デバイスを集積したモノリシックの3相インバータIC

図14:EPCのモノリシックのフルブリッジ

図15:ドライバを統合したEPCのGaNパワー・トランジスタ、

今日、エンハンスメント・モードのGaNオン・シリコンは、それと同じしきい値にいます。1976年のパワーMOSFETのように、ほぼ毎月のように出てくる新製品や画期的な能力によって、私たちはエキサイティングな旅を始めています。

パワーMOSFETは死んでいませんが、性能とコストの大幅な改善の道は行き止まりに近づいています。GaNは、十中八九、性能とコストの両方で、その大きな利点によって今後10年間で支配的な技術になるでしょう。すなわち、学習曲線を素早く登れるので、優位性の差を広げることが約束されています18)。

参考文献:

- http://www.infineon.com/dgdl/IPB025N10N3+G_Rev2.1.pdf?folderId=db3a304313b8b5a60113cee8763b02d7&fileId=db3a30431ce5fb52011d1ab1d9d51349

- B. J. Baliga, Power Semiconductor Devices, 1996, PWS Publishing Company, p. 373

- E. Mitani, H. Haematsu, S. Yokogawa, J. Nikaido, Y. Tateno, ”Mass Production of High Voltage GaAs and GaN Devices”, CS Mantech Conference, April 24-27, 2006, Vancouver B.C., Canada

- T. Mimura, N. Tokoyama, H. Kusakawa, K. Suyama, M. Fukuta, GaAs MOSFET for low-power high-speed logic applications, the 37th Device Research Conference, 25-27 June 1979, University of Colorado, Boulder, CO

- M. Asif Khan, J. N. Kuznia, and D. T. Olson, in Applied Physics Letters, Vol. 65, No. 9, 29 August 1994

- Supratik Guha and Nestor Bojarczuk, in Applied Physics Letters, Vol. 72, No. 4, 26 January 1998

- http://www.businesswire.com/portal/site/home/permalink/?ndmViewId=news_view&newsId=20051005005600&newsLang=en

- http//www.epc-co.com. EPC 1001 data sheet.

- http://www.infineon.com/dgdl/IPD068N10N3+G_Rev2.1.pdf?folderId=db3a304313b8b5a60113cee8763b02d7&fileId=db3a30431ce5fb52011d1eb7aeb615d1

- http//www.epc-co.com

- http://www.nitronex.com/pdfs/AD-009.pdf

- http://www.irf.com/product-info/ganpowir/introganpowir.pdf

- http://www.veeco.com/mocvd-turbodisc-k465-gallium-nitride/index.aspx

- http://aixtron.com/index.php?id=700&L=1

- http://www.nitronex.com/reliability.html

- http://www.sanken-ele.co.jp/en/news/contents/20080903e.htm

- http://www.physorg.com/news179516515.html

- Graham Pitcher, “Power for Change - How GaN might revolutionize Embedded Power Device Design”, www.newelectronics.co.uk, 27 January 2009

Download pdf version

Download pdf version