Johan Strydom, David Reusch, Steve Colino, Alana Nakata

Efficient Power Conversion Corporation(EPC)の超高速エンハンスメント・モード窒化ガリウム(GaN)パワー・トランジスタは、シリコン・ベースのパワーMOSFETの領域をはるかに超えた特性の向上を実現します。パワー・コンバータの標準的な回路構成では、特性向上の大きな恩恵と、現在のMOSFETの設計では得られない特性の飛躍が期待できます。すなわち、コンバータ設計の簡単さを維持した上で、コンバータの効率を向上できます。

eGaN FETの使い方は、現在のパワーMOSFETと非常に類似しています。ただし、特性が非常に優れているので、特定のデバイスを効率的かつ信頼性高く利用するために、設計とテストの更なる考察が必要です。

パワー・マネージメント(電源管理)・デバイスにおいて、可能な限り簡単に、パワーMOSFETから新しい世代のデバイスへ移行する努力の一環として、この論文では、エンハンスメント・モードGaNデバイスの一般的な動作、ゲート駆動技術、回路レイアウトの考察、熱管理技術、およびテストの考慮事項について説明します。

eGaN FETとGaNオン・シリコン技術の概論

構造

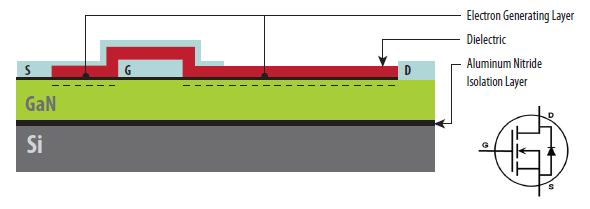

図1:EPCのGaNパワー・トランジスタの構造

デバイスの費用対効果を高めるためには、いくつかの製造工程のプロセスに対応する既存の生産インフラを活用することから始まります。減価償却された低分解能のCMOSファウンドリが、eGaN FETの製造に使われます。EPCのプロセスは、基板からデバイス構造を絶縁するために窒化アルミニウム(AlN)の薄い層を成長させたシリコン・ウエハーから始まります。この表面上に、高抵抗の窒化ガリウム層を成長させます。この層は、GaNトランジスタを構築するための基盤になります。窒化アルミニウム・ガリウム(AlGaN)が利用されます。この層は、物理的な歪みを生じ、GaNは圧電材料なので、この歪みがインタフェースに電子を引き付けます。この電子の集中は、2次元電子ガス(2DEG)と呼ばれています。さらに、ゲートの下に空乏領域を形成し、金属層が3端子、すなわち、ゲート、ドレイン、ソースを接続するために追加されます。この構造の断面が図1です。この構造は、パワー・デバイスを形成するために何度も繰り返されます。最終的な結果は、基本的に単純で洗練され、コスト効率の高いパワー・スイッチ向けのソリューションになります。このデバイスは、以下のセクションで説明されるいくつかの例外を除いて、シリコンMOSFETと同じように振る舞います。

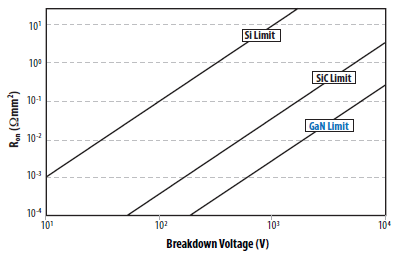

図2:オン抵抗と耐圧の関係

高耐圧デバイスを作るためには、ドレインとゲートとの間の距離を長くします。2DEGの抵抗率が非常に小さいので、ブロッキング電圧特性を増加させることによる抵抗への影響は、シリコンと比べてはるかに小さくなります。図2は、GaN、SiC、Siの各デバイスのオン抵抗とブロッキング電圧との間の理論的なトレードオフを示しています。シリコンMOSFETの開発は、30年が経って、その理論的限界に近づいてきています。シリコンの進歩は、小さな向上を得るために大きな開発コストがかかるところまで鈍化してきています。GaNは、そのライフ・サイクルの中でまだ若く、EPCの最初の4世代eGaN FETで分かるように、この技術の進歩は非常に急激に起こっています。

動作

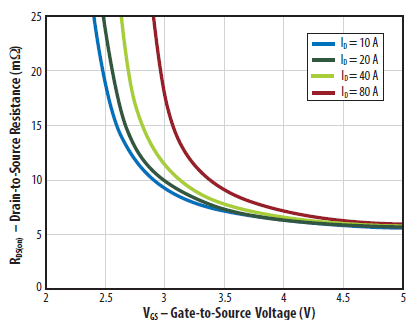

図4:EPC2001の電流を変えたときのR

DS(on) とV

GS の関係

EPCのeGaN FETは、シリコン・パワーMOSFETと同様に振る舞います。ソースを基準としてゲートに加えた正のバイアスは、ドレインとソースとの間の双方向チャネルを完成するために、電子を集めるための電界を発生させます。バイアスがゲートから除去されると、その下の電子は、GaNの中に拡散され、空乏領域を再形成し、再び、電圧を阻止する能力が与えられます。図3と図4は、それぞれ、EPC2001の伝達特性と、RDS(on) 対VGS の関係を示しています。伝達特性は、VGS の変化による電流特性を示します。RDS(on) が同等のeGaN FETは、相互コンダクタンス(did / dvgs)がはるかに大きいことを除いて、MOSFETと非常によく似ています。RDS(on) 対VGSの曲線は、VGS = 4V以上で平坦になることは当然です。

ドレイン-ソース間の最大定格電圧

ドレイン-ソース間の耐圧(BVDSS)は、EPCのGaNトランジスタのデータシートに規定されています。

誘導性負荷をスイッチングするときには、特別な注意を払わなければなりません。この種の負荷は、誘導性の「キックバック」によって、ドレイン電圧が最大定格を超える可能性があります。この現象によって、ドレイン電圧がブレークダウンを超えて大きくなり、コイルからのエネルギーがデバイス内で消費されることになります。

EPCのGaNトランジスタは、アバランシェ・モード動作に対して定格化されていませんが、BVDSSよりも20%大きなオーバーシュートが5ms以下の長さで1万サイクル繰り返したときの定格があります。もし、デバイスが、より高い電圧、より多くの繰り返しに曝されるなら、VDSの上昇を安全なレベルに制限するために、適切なアクティブまたはパッシブのクランプ/スナバ回路を使わなければなりません。回路の寄生インダクタンスを制限し、システム内の浮遊誘導エネルギーの存在を制限するために、適切なレイアウト技術が駆使されなければなりません。

ゲート駆動

eGaN FETは、スイッチング速度が非常に高速なので、シリコンの同等品とは異なります。この結果、ゲート駆動、レイアウト、熱管理のための異なる要求があり、これらはすべて相互に作用します。

ゲート駆動の最大定格を超えないこと

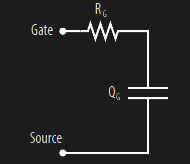

図5:EPCのGaNパワー・トランジスタのゲート等価回路

図4から分かるように、デバイスのチャネルの完全なエンハンスメントは、ゲート-ソース間の絶対最大電圧が6 Vなので、ゲートとソースとの間に4 V以上を印加することによって得られます。等価ゲート回路は、パワーMOSFETと同様に、小さなゲート抵抗と小さなゲート容量で構成されます(図5)。ハーフブリッジ構成で使う場合、ゲートが過電圧または低電圧にならないように注意しなければなりません。

dv/dt耐性

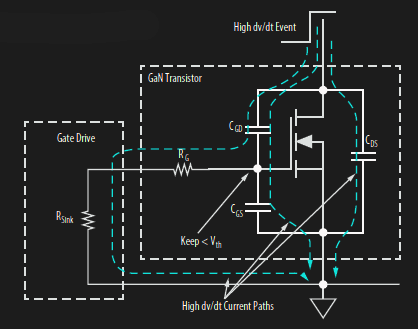

図6:オフ状態のデバイスへのdv/dtの効果と、ミラーによって誘発された貫通(シュートスルー)を防ぐことが必要

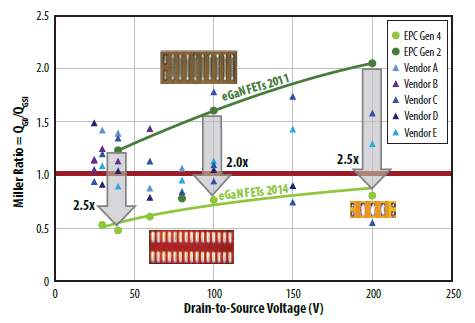

図7:それぞれの定格電圧の半分のドレイン-ソース間電圧に対する第2、第4世代のeGaN FETと、最先端のシリコンMOSFETのミラー比

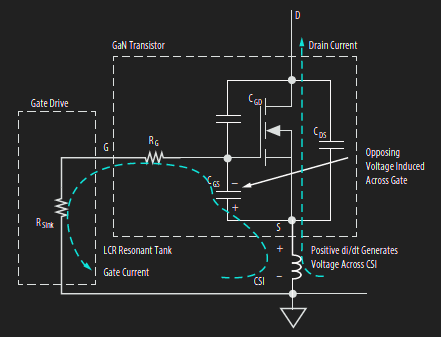

図8:コモン・ソース・インダクタンス(CSI)によるオフ状態デバイスへの正のdi/dt の影響

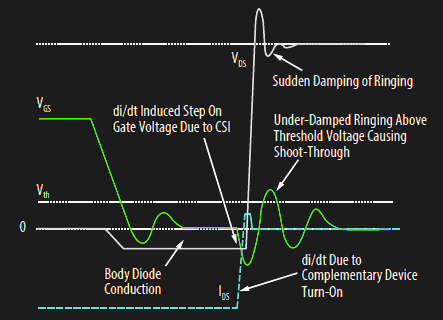

図9:アンダーダンプのゲート・ターン・オフのパワー・ループによって誘起されたdi/dtがオフ状態のデバイスをターン・オン(貫通)

オフ状態のデバイスのドレインに加わる高い正の電圧スルーレート(dv/dt)は、ハード・スイッチングとソフト・スイッチングの両方のアプリケーションで発生する可能性があり、図6に示すように、デバイス容量の急速充電によって特徴付けられます。dv/dt現象の間に、ドレイン-ソース間容量(CDS)が充電されます。同時に、直列のゲート-ドレイン間容量(CGD)とゲート-ソース間容量(CGS)も充電されます。もし対処されていないならば、CGDの充電電流が貫通し、Vthを超えてCGSを充電し、デバイスをオンさせます。この現象は、しばしば、ミラー・ターンオンと呼ばれ、MOSFETユーザーの間では、よく知られており、これは非常に散逸的な可能性があります。

パワー・デバイスのdv/dtの感度を決めるために、ミラー電荷比(QGD/ QGS1)は、ドレイン-ソース間電圧の関数として評価しなければなりません。ミラー比が1以下なら、理論的なdv/dt耐性が保証されます [1]。図7から、EPCの最新世代のeGaN FETにおけるミラー比が大幅に低減されていることが分かります。少なくとも1/2に低減されており、この結果、製品の線のすべてで、それぞれの定格電圧の半分の電圧において1を下回っています。図7で、三角形の点のプロットは、現在のシリコンMOSFETのミラー比で、一般的には、はるかに大きな値です。

di/dt耐性

図8に示すように、オフ状態のデバイスを介して上昇する電流は、コモン・ソース・インダクタンス(CSI)にかかるステップ電圧を誘起します。この正のステップ電圧は、CGSの両端にかかる逆電圧を誘起します。上昇する電流の場合、ゲート電圧を負の値にし、オフ状態のゲート・ループのLCR共振タンクの不十分な減衰によって、ゲートにかかるこの初期の負のステップ電圧が正のリンギングを引き起し、図9に示すように、意図しないオンや貫通を引き起こします。

上記のdv/dt耐性のときに説明したように、いくらかのアンダーシュートの方が好ましいかもしれませんが、ゲートのターン・オフ・ループを十分に減衰することによって、di/dtがオンするというこの種の現象を回避することができます。しかし、ゲートのプルダウン抵抗を大きくすることによってゲートのターン・オフのパワー・ループの減衰を増やすと、dv/dt耐性に負の影響を与えるでしょう。したがって、ぎりぎりのミラー電荷比を備えたデバイスに対してゲート抵抗だけを調整することは、di/dtおよび/またはdv/dtのターン・オンを回避するためには十分でないかもしれません。

より良い解決策は、パッケージの改善とデバイスのレイアウトによってCSIの大きさを制限することです。これは、可能な限りGaNデバイスの近くに配置したパワー・ループとゲートとを分離し、GaNデバイス内部のソース・インダクタンスを最小化することで実現でき、これは、両方のループに共通になるでしょう。

回路特性へのインダクタンスの影響に関する詳細な議論は、ホワイト・ペーパー(Impact of Parasitics on Performance)を参照してください。

以下は、EPCのGaNトランジスタに適したゲート・ドライバに必要な重要な特性です。eGaN FETを機能させるコントローラに対してだけでなく、そのドライバにも以下が必要になります。

- グラウンド・バウンス耐性:ゲート・ドライバの設計は、ドライバのグラウンドとコントローラのグラウンドが著しく異なる可能性があることを想定し、入力論理ピンは、雑音によって誘発される論理状態の変化に対する耐性を備えていなければなりません。

- ハイサイド・ドライバの大きなdv/dt耐性:フローティングのハイサイド・デバイスに制御論理信号を伝送するために使われるロジック・アイソレータまたはレベル・シフターは、論理状態が変わることがないように、dv/dtが大きい立ち上がり時間と降下時間に対する耐性が必要です。より高い電圧では、より大きなdv/dt耐性が必要ですが、100 V以下、50 V/nsの耐性で十分なはずです。

- 低インダクタンスの表面実装パッケージと最適化されたピン配置:ゲート駆動回路と高速GaNデバイスは、最小化された配線インピーダンスで近くに配置する必要があります。これには、GaNトランジスタを補足するピン配置とパッケージの選択が必要です。QFN/DFNパッケージまたはWLCSPパッケージを推奨します。相補型のピン配置とは、VBS/ HG/ VSWが隣同士で、VCC / LG/ PGNDが隣同士になっていることです。

- ゲートのパワー・ループのインダクタンスの最小化:ゲート・ドライバは、VDD電源のコンデンサと実際のゲート・ドライバのパワー・デバイス(電流の吸い込みと吐き出しのデバイス)との間のインダクタンスを最小化にするように設計しなければなりません。これは、ゲート・ドライバの立ち上がり時間を最小化し、ドライバのdi/dtを最大化するでしょう。入力容量が50 pF程度と小さい第3世代のデバイスを駆動するには、立ち上がり時間/降下時間が500 ps程度よりも小さいドライバが最も適しています。

- ゲート駆動能力:汎用GaNドライバの速度は、駆動されるデバイスのサイズと速度に合わせる必要があります。この柔軟性を備えるには、外付け抵抗を追加できるオプションを備えた低抵抗のゲート・ドライバが必要です。1Ωから3Ωの範囲内のプルアップ/プルダウン抵抗を駆動できるゲート駆動能力が推奨されます。

- プルアップ/プルダウン抵抗を駆動するためのゲートは、1Ωから3Ωの範囲内を駆動しなければなりません。もし、その抵抗が、大きければ、遅すぎるでしょう(または低電力用途に限定されるでしょう)。それが非常に小さいなら、リンギングの問題を引き起こす可能性があります。特に、高インダクタンスのワイヤー・ボンド・パッケージと組み合わせて使う場合は、その可能性が高くなります。

- ゲート駆動の電源電圧の安定化:ローサイド・ドライバ、および、特にハイサイド・ドライバの両方に対して、トランジスタのゲートへの過電圧状態を回避するために、ゲート駆動の電源電圧を安定化する必要があります。ゲート駆動の仕様は、最大で5 V±0.5 V 、推奨は5 V±0.25 Vです。

- デッドタイム:デッドタイムの最小化は、「ボディ・ダイオード」の順方向電圧の損失を制限します。20 ns以下のデッドタイムを推奨します。eGaN FETのデッドタイム管理の詳細については、ホワイト・ペーパー「Dead-Time Optimization for Maximum Efficiency」を参照してください。

- 高周波動作:eGaN FETは、10 MHz以上のスイッチング能力があります。高周波動作向けに最適化されたゲート・ドライバには、最小オン時間が小さいこと、ハイサイド電源とグラウンドとの間の内部容量が小さいこと、外付けショットキー・ダイオードを利用するなどで逆回復を小さくしたブートストラップ電源の利用などが必要です。ドライバの高周波動作に影響する事項の詳細については、Hard Switching Converters at High Frequencyを参照してください。

詳しくは、eGaN® FET Drivers and Layout Considerationsをご覧ください。

エンハンスメント・モードGaNと互換性のあるICの現在のリストについては、www.epc-co.com/epc/jp/製品/eGaNドライバとコントローラ.aspxを参照してください。

レイアウトの考察

これらのデバイスを利用したプリント回路基板を設計するとき、EPCのGaNトランジスタは、高速スイッチング能力と高い電流供給能力があるので、特別な配慮をしなければなりません。これを説明するために、バック・コンバータの例を見てみましょう。

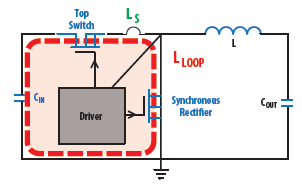

図10:同期整流型バック・コンバータの寄生インダクタンス

実際のバック・コンバータでは、図10に示されているような2つの主な寄生インダクタンスがあり、これがコンバータの特性に大きな影響を与えます。

1. 共通ソース・インダクタンスLSは、ドレインからソースへのパワー電流経路と、ゲート・ドライバのループによって生じるインダクタンスです。

2. 高周波パワー・ループ・インダクタンスLLOOPは、パワーの転流ループで、入力容量の正の端子から、上側のデバイス、同期整流器、グラウンド・ループ、入力容量を通る寄生インダクタンスで構成されます。

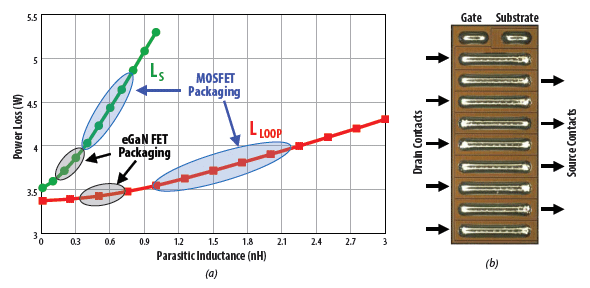

図11:(a) 電力損失に影響する寄生インダクタンス(V

IN = 12 V、V

OUT = 1.2 V、I

OUT = 20 A、F

SW = 1 MHz)

上側のスイッチ:

EPC2015、同期整流器:EPC2015、(b) eGaN FETのLGAパッケージ

共通ソース・インダクタンスLSは、デバイスの駆動速度に直接影響するので、特性に対して重要であることが示されています [2] ~ [4]。共通ソース・インダクタンスは主に、パッケージごとに異なるパッケージ・インダクタンスが支配的です [5]、[6]。eGaN FETでは、図11aに示すように、LGAパッケージ(図11b)の共通ソース・インダクタンスが小さいので、損失を低減できます。

高周波ループ・インダクタンスLLOOPは、スイッチングの転流時間と、デバイスのドレイン-ソース間のスパイク電圧のピーク値に影響します。高周波ループ・インダクタンスは、プリント回路基板のレイアウトとパッケージのインダクタンスが支配的です。eGaN FETのLGAのようにパッケージの寄生成分が小さいことを利用する用途では、プリント回路基板のレイアウトが高周波ループ・インダクタンスで支配的になります [7] ~ [10]。

eGaN FETによって提供されるパッケージ関連インダクタンスの大幅な削減によって、共通ソース・インダクタンスが最小化され、もはや寄生の損失の主な原因ではなくなります。プリント回路基板のレイアウトが損失の大きな要因になった高周波ループ・インダクタンスでは、eGaN FETを使うレイアウトが高周波特性に対して重要になります。

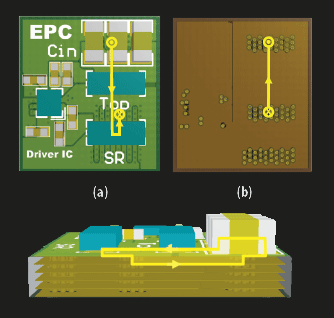

低減された寄生成分に対するeGaN FETの最適レイアウト

図12:eGaN FET向けに提案された最適パワー・ループの表面の図(a)、内部の第1層の図(b)、側面図(c)

eGaN FETの高速スイッチング能力を活用するために、このデバイスは、内部のインダクタンスが小さいだけでなく、ユーザーの回路基板を超低インダクタンスで設計することを可能にするランド・グリッド・アレイ(LGA)パッケージで開発されました。ループ・サイズの縮小、磁界自己キャンセル、基板の厚さに独立な一定のインダクタンス、片面基板設計、多層構造に対して高効率といった利点を提供するために、eGaN FET向けの最適なレイアウトが提案されています。この設計は、パワー・ループの戻り経路として、図12bに示される内部の第1層を利用します。この戻り経路は、図12aのように表面の層のパワー・ループの直下に位置し、磁界自己キャンセルと組み合わせて、物理的に最も小さなループ・サイズを可能にします。側面図(図12c)は、多層のプリント回路基板において、低プロファイルの自己キャンセル・ループを構成するときの概念を示します。

改善されたレイアウトでは、上側のeGaN FETのドレイン接続の隣に位置した正の入力電圧端子において、上側のデバイスの近くに入力コンデンサを配置します。eGaN FETは、横方向および縦方向のパワー・ループの場合と同じ位置に配置されます。2つの eGaN FETの間には、同期整流用eGaN FETのLGAフィンガに一致するように並べられ、インタリーブされたスイッチング・ノードとグラウンド・ビアが配置されます。インタリーブされたスイッチング・ノードとグラウンド・ビアは、同期整流器の底部側に複製されます。これらのインタリーブされたビアには、3つの利点があります。

(1)2つのeGaN FETの間に配置されたビアの列によって、高周波ループ・インダクタンスの経路の長さが短くなるので、寄生インダクタンスの低減につながります。

(2)同期整流用eGaN FETの下に配置したビアの列は、同期整流用eGaN FETのフリーホイール期間中に抵抗を低減するための追加のビアとなり、導通損失を低減します。

(3)逆方向に電流を流すと共にインタリーブしたビアの列は、渦効果と近接効果の低減を可能にし、交流の導通損失を低減します。

熱の考察

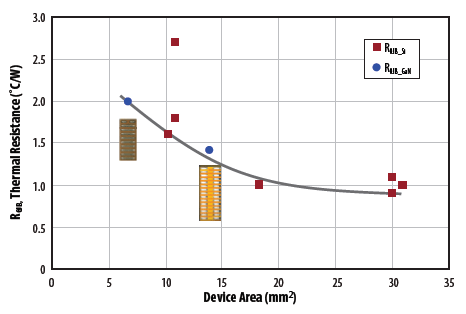

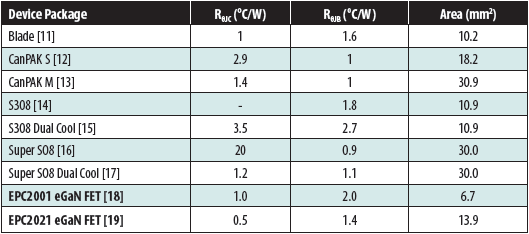

大電力密度のパワー・デバイスは、熱の発生を小さくすることによって電気的により効率的にするだけでなく、優れた熱伝導特性にしなければなりません。パッケージの熱効率は、パッケージ面積で正規化した2つのパラメータRɵJCとRɵJBを比較することによって決めることができます。RɵJCは、接合部からパッケージへの熱抵抗で、側壁を含めて、シリコン基板の上のeGaN FETのアクティブ領域からの熱抵抗です。RɵJBは接合部からプリント回路基板への熱抵抗で、eGaN FETのアクティブ領域から回路基板への熱抵抗です。この経路の熱は、はんだバーを介して回路基板上の銅トレースに伝わらなければなりません。表1に、いくつかの一般的な表面実装用MOSFETパッケージと、2つの一般的なeGaN FETの熱に関連した特性をまとめました。

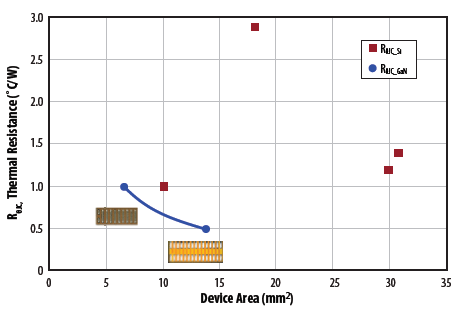

図13:表1に記載されている各パッケージ形状のR

ƟJB(接合部から回路基板への熱抵抗)。eGaN FETは青色の丸い点、シリコンMOSFETは赤色の四角の点で示しました。

図13は、表1の各パッケージに対する接合部から回路基板への熱抵抗RƟJBのプロットです。赤色の四角い点はMOSFETパッケージ、青色の丸い点はeGaN FETを表しています。選んだパッケージの大部分は、この熱抵抗成分の特性が、技術ではなく、主にパッケージ・サイズによって決まっていることを示す単一のトレンド線に乗っています。対照的に、図14に、接合部からパッケージへの熱抵抗RƟJCのプロットを示します。CanPAKと両面放熱可能なSO8パッケージは、パッケージ表面からの放熱において、BladeパッケージやeGaN FETよりもはるかに効率的ではありません。ただし、同じ面積に規格化すると、eGaN FETは、Bladeよりも30%以上低くなっています [11]。これによって、eGaN FETは、両面放熱に対して最も熱効率が高いパッケージであり、高い電力密度の設計に最適なデバイスであることが分かります。

表1:パッケージ面積、および熱抵抗成分R

ƟJCとR

ƟJBの比較

図14:表1に記載されている各パッケージ形状のR

ƟJC(接合部からパッケージへの熱抵抗)。eGaN FETは青色の丸い点、シリコンMOSFETは赤色の四角の点で示しました。

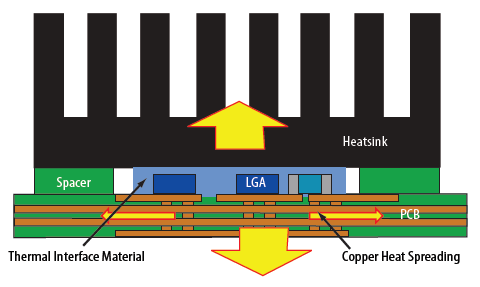

図15に示すように、EPCのGaNトランジスタの更なる利点は、両方の熱の経路に対する熱抵抗を改善できることです。まず第1に、プリント回路基板から周囲への熱抵抗は、サーマル・ビアを追加することによって低減できます。サーマル・ビアを使って、内部と外部の銅の層を接続し、熱を横方向に拡散できます。第2に、熱伝導材料(TIM)の抵抗は、2つの方法で低減することができます。

図15:表面のヒートシンクとプリント回路基板を介して熱を拡散するサーマル・ビアを示した両面放熱可能な回路基板に実装されたLGA封止のGaNトランジスタの熱の流れ

1)デバイスとヒートシンクのインタフェースの厚さを薄くする:クラックが生じないように、ヒートシンクに加えられた任意の実装の力がデバイスに伝わらないようにするために、通常、ヒートシンクとデバイスの間に、TIMと一緒にスペーサを配置する必要があります。このスペーサは、ヒートシンクとGaNデバイスの間の最小距離を決めます。

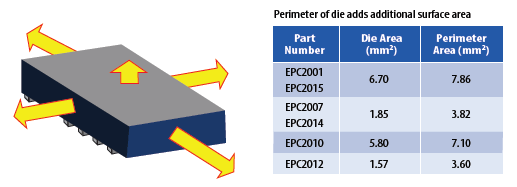

2)(パッケージの)表面だけでなく、デバイスのすべての側面に熱伝導材料を配置する:デバイス周囲の側壁の表面積は表面よりも広くなっています。これを図16に示しました。

図16:LGA封止のGaNトランジスタのチップの表面の面積と周囲の側面面積

更なる改良は、両面のヒートシンクや強制空冷の利用、および、DBC(セラミック基板上に銅回路版を共晶反応で接合)またはIMS(絶縁金属基板)などエキゾチックなプリント回路基板材料の利用によって可能になります [20]。

回路動作のシミュレーションにデバイス・モデルを使う

エンハンスメント・モードのデバイスは、シリコンMOSFETと同じように動作するように作られていますが、GaNトランジスタの物理が大きく異なるように、それらは、従来の物理に基づくMOSFETモデルで直ちにモデル化することはできません。EPCのエンハンスメント・モードGaNトランジスタ向けに開発されたモデル [21] は、許容できるシミュレーションと収束特性を備えたコンパクトなSPICEモデルを実現するために、物理に基づく関数と現象論の関数との混成です。温度の影響も、導電性としきい値パラメータに含まれています。エンハンスメント・モードGaNトランジスタのための基本的な等価回路を図17に示します。主な構成要素は、電圧制御型電流源ID、コンデンサCGD、CGS、CDS、終端抵抗 RS、RD、RGです。

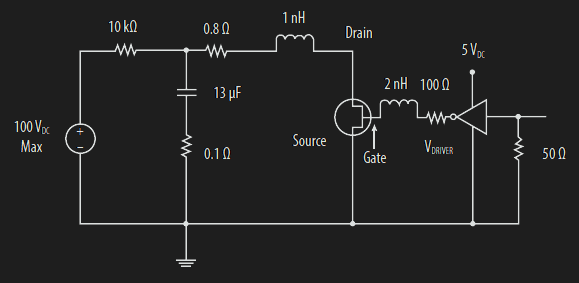

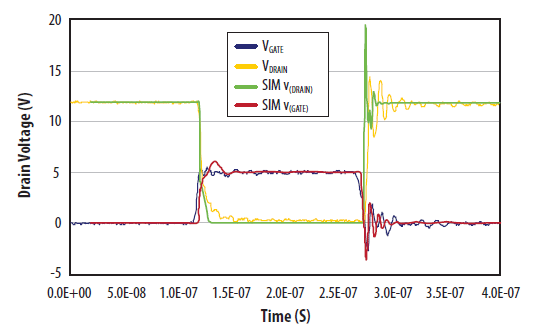

デバイス・モデルと回路の考察のデモンストレーションとして、簡単な回路を構成し、モデルによって予測されたデバイスの特性と比較するテストを行いました(図18)。

図18:基本的なデモ回路の回路図

図19:デモ回路のシミュレーション結果と実測との比較

この回路は、被試験デバイスから電圧源を絶縁するために使われた10 kΩの抵抗を介して13 µFのコンデンサを充電する電圧源で構成されます。GaNトランジスタは、5 Vのパルスで駆動され、コンデンサは、0.8Ωの抵抗と、0.1Ωの浮遊抵抗があるデバイスを介して放電されます。デモ回路のシミュレーション結果を実測値と比較すると、合理的な相関を示します。完璧ではありませんが、オーバーシュートやリンギングが定性的に再現されています。図19は、測定した回路とシミュレーションした回路に対するゲート電圧およびドレイン電圧対時間の重ね書きです。

EPCによって開発されたモデルは、回路の動作条件の下で、デバイスの基本的な応答を正確に再現します。 EPCのデバイス・モデルは、EPCのウエブサイト(www.epc-co.com/epc/jp/設計サポート/デバイスモデル)からダウンロードできます。

カーブ・トレーサと自動テストの考察

EPCのエンハンスメント・モードGaNトランジスタは、一般的には、nチャネル・パワーMOSFETのように振る舞います。nチャネル・パワーMOSFETに使われる一般的なカーブ・トレーサ、パラメトリック・アナライザ、ディスクリート・デバイスの自動パラメトリック・テスターは、GaNトランジスタの特性評価に適用できるでしょう。米テクトロニクス社の576カーブ・トレーサ、米ケースレー社の238パラメトリック・アナライザ、またはテセックの881-TT/Aディスクリート・デバイス・テスト・システムを使って直流パラメータを測定するための一般的なガイドラインをいくつか以下にまとめました。

図20:100 VのeGaN FETで、ゲート抵抗がある/なしのときのV

TH 曲線の比較

注意:GaNトランジスタは静電気に敏感です。GaNトランジスタは、容量が非常に小さく、許容されるゲート電圧の最大値が小さくなっています。リスト・ストラップ、接地マット、および、他のESD予防策は、デバイスの最大定格を超えないようにしなければなりません。

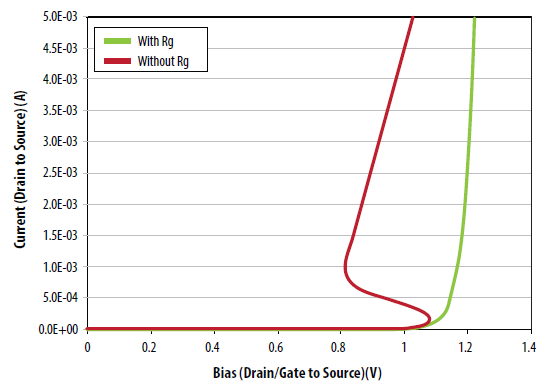

VTHの測定

VTH は、データシートに規定されたドレイン電流が流れるゲート-ソース間電圧(VDS = VGS)です。このテストは一般的に、ドレインとゲートを短絡して実施されます。

VTH カーブ・トレーサ試験の注意:VTH 測定中に、ゲートに直列ゲート抵抗(RG)がない場合、図20に示すような典型的なS字曲線になるようなゲートでの発振を観測することがあります。この発振電圧が、入力電圧の何倍にもなることがあります。この発振によって、デバイスが損傷したり、破壊したりすることがあります。

IGSS の測定

IGSS は、ドレインをソースと短絡したときのゲート-ソース間の漏れ電流です。

その電圧がデバイスのゲートの最大定格であるとして、ゲートで、正の方向に6 V、負の方向に4 Vを超えないようにしてください。

正確にIGSS を測定するためには、ドレインとソース間の短絡時の抵抗が非常に低いことが重要です。テスト中のレンジ変更は、ゲートを破壊するおそれがあるスパイク電圧につながる可能性があるので、テセックの881-TT/Aのような自動テスト装置では、IGSS テスト中にオートレンジ機能を使わない方が良いでしょう。

RDS(on) 測定

RDS(on) は、VGS = 5 Vのときのドレインからソースへの抵抗です。RDS(on) は温度に対する感度が高いので、テスト中に接合部の発熱を最小限にすることが重要です。したがって、ドレイン・パルス試験がRDS(on) の測定に使われます。RDS(on)の正確な測定には、ドレインとソースの両方にケルビン検出を使う必要があります。検出点の位置は、RDS(on)の読みに強く影響します。テスト中のレンジ変更は、ゲートを破壊するおそれがあるスパイク電圧につながる可能性があるので、テセックの881-TT/Aのような自動テスト装置では、RDS(on)テスト中はオートレンジ機能を使わない方が良いでしょう。

RDS(on) を測定するために裸のチップ上に針を使うことは推奨できません。プローブ針/はんだバンプ・コンタクトでの電流密度が高すぎると、デバイスを損傷するおそれがあります。

IDSS / BVDSS 測定

BVDSS は、VGS = 0 Vでのデバイスの定格電圧です。IDSS は、VGS = 0 Vにおいて、デバイスの定格電圧以下で指定されたドレイン-ソース間電圧におけるドレイン電流です。

EPCのGaNデバイスの真の降伏電圧は、一般に、デバイスのドレイン-ソース間電圧の最大定格よりも十分大きくなっています。VDSS の最大定格を超えてしまうので、BVDSS テストは、デバイス上で行うべきではありません。もし最大定格を超えると、デバイスのRDS(on) が劣化するかもしれません。ソースに対してゲートがフローティングになり、誤ってデバイスがオンすることを避けるために、ゲートとソースの短絡も非常に重要です。これが発生すると、デバイスは、IDSS テスト中に破損するかもしれません。

IGSS やRDS(on) の測定と同様に、テスト中のレンジ変更は、ゲートを破壊するおそれがあるスパイク電圧につながる可能性があるので、テセックの881-TT/Aのような自動テスト装置では、IDSS テスト中はオートレンジ機能を使わない方が良いでしょう。固定のドレイン電流でのドレイン-ソース間電圧の測定は、デバイスのVDS の最大定格を超える可能性があるため、「BVDSS 機能」の使用も避けるべきです。

IDSS 測定中にテストの設定電圧を超えるスパイクが発生しないことを、最初に確認する必要があります。電圧オーバーシュートの回避のために、制御された電圧ランプを使うことを勧めます。

ソースに対してゲートがフローティングになり、誤ってデバイスがオンすることを避けるために、ゲートとソースの短絡も非常に重要です。これが発生すると、デバイスは、IDSS テスト中に破損するおそれがあります。これは、ゲートを0 Vに設定するだけでは十分ではありません。すなわち、ゲートからソースへの短絡時の抵抗を十分に低くしなければなりません。

最後の注意

デバイスをいかに簡単に使うかは、ユーザーのスキル、開発中の回路の難易度、ユーザーの経験の範囲内のデバイスと比べて、このデバイスがどのように異なるか、ユーザーが利用するデバイスに役立つ利用可能なツールがあるか、に依存します。

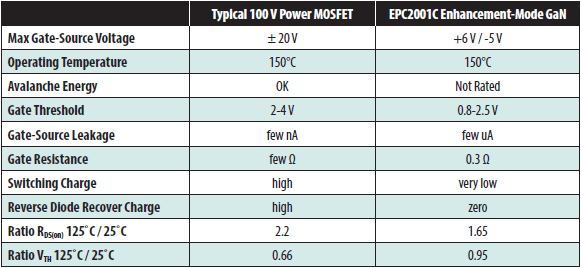

エンハンスメント・モードGaNトランジスタの新しい世代は、その振る舞いが既存のパワーMOSFETと非常に類似していますが、はるかに高速です。ユーザーは、過去の設計経験を有効に活用でき、新たなレベルの特性の製品を実現することができます。eGaN FETの比較的高い周波数応答によって、ステップ関数は従来のいかなるシリコン・デバイスをも上回って改善され、回路をレイアウトするときの追加された考察も有効です。

一方で、これらのデバイスの能力を、前任者であるシリコンよりも簡単に発揮させるいくつかの特性があります。例えば、しきい電圧が広い範囲にわたって実質的に温度と独立であることや、オン抵抗の温度係数がシリコンよりも著しく低いことです。

表2は、シリコン・パワーMOSFETと、GaNトランジスタのEPC2001Cの基本特性の比較をまとめたものです。

表2:100 Vのシリコン・パワーMOSFETと100 VのeGaN FET との比較の概要

新しいタイプのデバイスを適用することをいかに簡単にするかにおいて、ユーザー・フレンドリなツールも大きな違いを生み出します。EPCは、ユーザーがダウンロード可能なデバイス・モデルの完全なセットを開発しています。これらのモデルは、エンジニアの生産性の改善と、製品を市場に出すまでにかかる時間の短縮を可能にする合理的で信頼性の高い回路特性の予測を提供します。

アプリケーション・ノートとデザイン・チップスは、長年にわたるエンジニアの経験を集めて成文化したものです。EPCのGaNのライブラリ(www.epc-co.com/epc/jp/ganライブラリ.aspx)には、アプリケーション・ノート、ホワイト・ペーパー、学術雑誌の豊富なコレクションがあります。さらに、書籍「GaN Transistors for Efficient Power Conversion」[22] の第2版は、GaN技術とその応用を明確にしたテキストです。

パワーMOSFETは死んでいませんが、性能とコストの大幅な改善への道は終わりに近づいています。GaNは、性能とコストの両方で、その大きな利点のために今後10年間をかけて主要な技術になる位置につけています。すなわち、学習曲線を一気に滑り落ちるように、利点の差を広げることが約束されています。

参考文献

- Wu, T. “Cdv/dt Induced Turn-On In Synchronous Buck Regulators”, white paper, International Rectifier Corporation

- A. Elbanhawy, “Effects of parasitic inductances on switching performance,” in Proc. PCIM Eur., May 2003, pp. 251–255.

- G. Nobauer, D. Ahlers, J. Sevillano-Ruiz, “A method to determine parasitic inductances in buck converter topologies,” in Proc. PCIM Eur., May 2004, pp. 37–41.

- B. Yang, J. Zhang, “Effect and utilization of common source inductance in synchronous rectification,” in Proc. IEEE APEC’05, Mar. 2005, vol. 3, pp. 1407–1411.

- M. Pavier, A. Woodworth, A. Sawle, R. Monteiro, C. Blake, and J. Chiu, “Understanding the effect of power MOSFET package parasitic on VRM circuit efficiency at frequencies above 1 MHz,” in Proc. PCIM Eur., May 2003, pp. 279–284.

- D. Reusch, D. Gilham, Y. Su and F.C. Lee, “Gallium nitride based multi-megahertz high density 3D point of load module,” APEC 2012. pp.38-45. Feb. 2012.

- T. Hashimoto, T. Kawashima, T. Uno, Y. Satou, N. Matsuura, “System in package with mounted capacitor for reduced parasitic inductance in voltage regulators,” Applied Power Electronics Conference and Exposition, 2008. APEC 2008. Twenty-Third Annual IEEE, pp.187-191, 24-28 Feb. 2008.

- Y. Kawaguchi, T. Kawano, H. Takei, S. Ono, A. Nakagawa, “Multi Chip Module with Minimum Parasitic Inductance for New Generation Voltage Regulator,” Power Semiconductor Devices and ICs, 2005.

- A. Ball, M. Lim, D. Gilham, F.C Lee, “System design of a 3D integrated non-isolated Point Of Load converter,” Applied Power Electronics Conference and Exposition, 2008. Twenty-Third Annual IEEE, pp.181- 186, 24-28 Feb. 2008.

- D. Reusch, F.C. Lee, Y. Su, D. Gilham, “Optimization of a High Density Gallium Nitride Based Non- Isolated Point of Load Module,” Energy Conversion Congress and Exposition (ECCE), IEEE, Sept. 2012.

- Infineon Blade BSN012N03LS datasheet, www. infineon.com

- Infineon CanPAK S-size BSF134N10NJ3 G datasheet, www.infineon.com

- Infineon CanPAK M-size BSB012N03LX3 G datasheet, www.infineon.com

- Infineon S3O8 BSZ075N08NS5 datasheet, www.infineon.com

- Texas Instruments S308 Dual Cool SON 3.3x3.3mm CSD16323Q3C datasheet, www.TI.com

- Super SO8 BSC010N04LS datasheet, www.infineon. com

- Texas Instruments Super SO8 Dual Cool SON 5x6mm CSD16321Q5C datasheet, www.TI.com

- Efficient Power Conversion EPC2001 datasheet

- Efficient Power Conversion EPC2021 datasheet

- D. Reusch, “High Frequency, High Power Density Integrated Point of Load and Bus Converters,” Ph.D. dissertation, Virginia Tech, http://scholar.lib. vt.edu/theses/available/etd-04162012-151740/ 2012.

- R. Beach, A.Babakhani, R. Strittmatter, “Circuit simulation using EPC device models,” epc-co.com/ epc/documents/product-training/Circuit_Simulations_ Using_Device_Models.pdf

- A. Lidow, J. Strydom, M. de Rooij, D. Reusch “GaN Transistors for Efficient Power Conversion,” Second Edition, Wiley, ISBN 978-1-118-84476-2.

Download pdf version

Download pdf version