高い信頼性を確保し、eGaNデバイスから最大の性能を引き出すためには、これらのシンプルなプリント回路基板の設計とアセンブリのガイドラインに従うことが重要です。一般に、デバイスには以下が必要です:

1. きれいなプリント回路基板の表面に、はんだが適切に収容されるように、各はんだバンプにプリント回路基板のはんだマスク定義(SMD)の正しいフットプリントを用意します。

2. ランド間からのはんだフラックスを適切に洗い流すための十分な高さを確保するために、適切なはんだ量とリフロー・ プロセスを実行します。ただし、リフロー中に接合部が不安定になり、傾いたり崩れたりする過剰なはんだは避けてください。

3. 電源を投入する前に、ランド間からフラックスをすべて洗い流し、乾燥させてください。

4. アンダーフィルの使用はオプションですが、特に大型デバイスの場合、温度サイクル性能を大幅に向上させることができます。詳細については、信頼性レポート:フェーズ15のセクション6を参照してください。

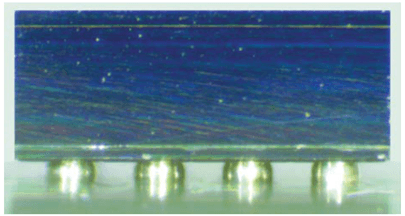

図1:適切に実装されたeGaNデバイス(側面図)

図1:適切に実装されたeGaNデバイス(側面図)

これらのガイドラインの詳細は、eGaN FETと集積回路のアセンブリ.

QFNパッケージのアセンブリに関する詳細については、EPCにお問い合わせください。