eGaN FETベースのパワー段を最適なレイアウトで設計する方法

GaNの話 – Rick Pierson

10 24, 2018

動機

eGaN® FETは、Si MOSFETよりもはるかに高速にスイッチングできるので、寄生インダクタンスを最小限に抑えるために、プリント回路基板のレイアウト設計に細心の注意を払わなければなりません。寄生インダクタンスによって、オーバーシュート電圧が大きくなり、スイッチングの遷移が遅くなります。このアプリケーション・ノートでは、これらの不要な影響を避け、コンバータの特性を最大限に引き出すために、eGaN FETを使って最適なパワー段のレイアウトを設計するための鍵となるステップについて検討します。

スイッチング動作への寄生インダクタンスの影響

図1に示すように、3つの寄生インダクタンス、すなわち、1)パワー・ループのインダクタンス(Lloop)、2)ゲート・ループのインダクタンス(Lg)、3)共通ソースのインダクタンス(Ls)によって、スイッチング特性が制限されます。eGaN FETのチップスケール・パッケージは、トランジスタ内部のインダクタンスをかなり排除しているので、主な制限要因としてプリント回路基板が残ります。各寄生インダクタンスは、動的電流経路とその戻りループによって囲まれる領域全体にあります(WP009:特性への寄生容量の影響を参照)。

図1:寄生インダクタンスと動的電流ループを強調したeGaN FETベースのパワー段の等価回路

図1:寄生インダクタンスと動的電流ループを強調したeGaN FETベースのパワー段の等価回路eGaN FETベースのパワー段の最適レイアウト

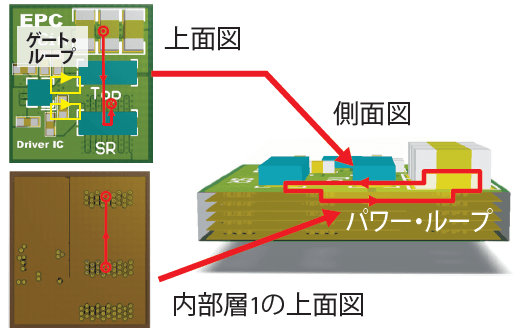

パワー・ループとゲート・ループのインダクタンスの最小化は、最適な戻り経路を形成するためにプリント回路基板内部の層を利用することで実現できます。デカップリング・コンデンサは、ハイサイド・トランジスタのドレインの近くに配置されています。プリント回路基板のビアは、インダクタンスを低く保つために、誘電体の厚さを意図的に薄く保った内部の1層目を経由して、コンデンサの接地端子をローサイドのソースに接続するために使われます。この最適なレイアウト手法の例が図2です。

図2:動的電流ループ経路を強調したeGaN FETベースのパワー段の最適レイアウト

図2:動的電流ループ経路を強調したeGaN FETベースのパワー段の最適レイアウトゲート・ドライバは、各トランジスタ、または、それ駆動するトランジスタのゲート端子とソース端子に、できる限り近くに配置し、バイパス/ブートストラップのコンデンサとゲート抵抗は、ゲート電流の方向がパワー・ループに対して直交するように配置しなければなりません。共通ソース・インダクタンスを最小化するには、ゲートの戻り電流経路をソース端子のパワー・ループと分離することが重要です(WP010:プリント回路基板レイアウトの最適化およびWP008:eGaN FETのドライバとレイアウトの考察を参照)。

最適なレイアウトがコンバータ特性にどのように役立つか

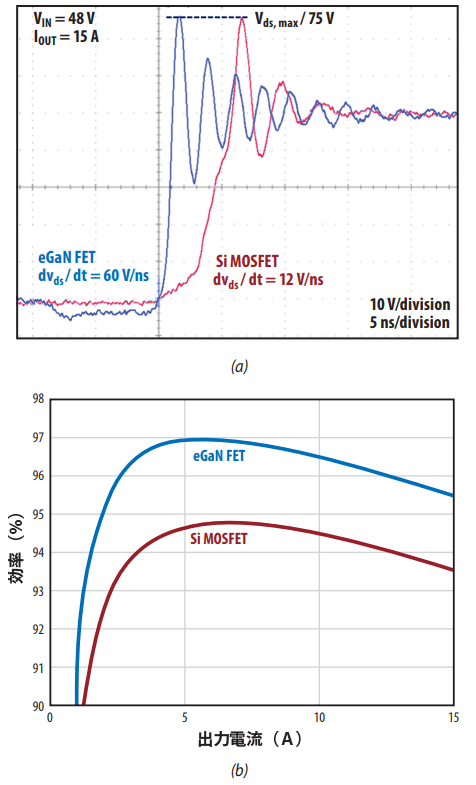

eGaN FETを搭載したコンバータ・システムは本質的に、同等のSiベースの設計よりも優れており、最適なレイアウト技術によって、これらの利点が一段と強化されます。図3は、500 kHzで動作する48 V入力、12 V出力のバック・コンバータにおけるeGaNの利点を示しています。S3O8パッケージの100 VのSi MOSFETと100 VのeGaN FETであるEPC2045とを比較しています。どちらのコンバータも最適なレイアウト技術を採用していますが、超小型チップスケールのEPC2045は、大きなSi MOSFETよりもループ・インダクタンスがかなり小さくなります。図3(a)は、GaNの高速スイッチング能力とループ・インダクタンスが小さいことの組み合わせによって、Si版と同じピーク・オーバーシュート電圧を維持しながら、eGaN版は電圧のスルーレートが5倍に達していることを示しています。図3(b)からピーク効率が2%以上高いことが分かるように、スイッチング・エッジの高速化は、システム特性に驚くほど大きな影響を与えます。

図3:100 VのSi MOSFETの例に対するeGaN FET(EPC2045)を使った最適レイアウトの48 V入力、12 V出力のバック・コンバータの比較、(a)スイッチ・ノードの波形、(b)システム効率

図3:100 VのSi MOSFETの例に対するeGaN FET(EPC2045)を使った最適レイアウトの48 V入力、12 V出力のバック・コンバータの比較、(a)スイッチ・ノードの波形、(b)システム効率モノリシックのeGaNハーフブリッジIC

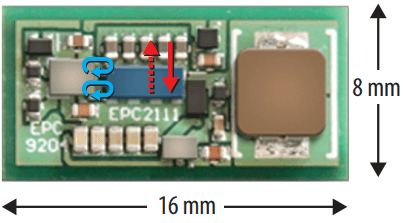

eGaNハーフブリッジICのモノリシック化によって、ループ・インダクタンスがさらに改善されます。例えば、12 V入力、1 V出力のPOL(負荷点)コンバータを集積化すると、ディスクリートのソリューションと比べて、パワー・ループのインダクタンスが40%減少します。図4は、モノリシック・ハーフブリッジのeGaN ICであるEPC9204を使ったPOLパワー・モジュール EPC2111です。集積化によって実現可能な超高密度のパワー・ループとゲート・ループを強調して示してあります。詳細は、AN018:DC–DCの効率と電力密度を向上するためのGaNの統合を参照してください。

図4:モノリシックのeGaNハーフブリッジICであるEPC9204を使った20 V、10 Aのパワー・モジュールEPC2111、パワー・ループとゲート・ループを強調

図4:モノリシックのeGaNハーフブリッジICであるEPC9204を使った20 V、10 Aのパワー・モジュールEPC2111、パワー・ループとゲート・ループを強調 結論

eGaN FETはスイッチング速度が速いので、寄生インダクタンスを最小限に抑え、これらの高度なデバイスを十分に活用するために、パッケージとレイアウトの技術を改善しなければなりません。チップスケールのeGaN FETは、パッケージのインダクタンスをほぼゼロに低減すると同時に、プリント回路基板のパワー・ループを超低インダクタンスにできます。プリント回路基板のレイアウトを最適化することは、eGaN FETベースの設計の特性を最大化するための重要なステップです。