Johan Strydom、David Reusch、Steve Colino及Alana Nakata

宜普電源轉換公司(EPC)的增強型氮化鎵(GaN)功率電晶體具備超快速開關特性,在性能方面的改進是矽基功率MOSFET所無法實現的。高效氮化鎵元件有利於標準功率轉換器的拓撲並增強其性能至目前採用MOSFET的設計所不可能達到的水平,在提高轉換器的效率之同時也能夠維持轉換器的設計的簡潔性。

使用氮化鎵場效應電晶體(eGaN FET)與使用先進功率MOSFET是非常相似的。但是,由於氮化鎵元件具備明顯更高的性能,因此我們需要考慮額外的設計和測試因素,從而確保元件可以高效及可靠地工作。

爲了幫助用戶容易從功率MOSFET轉用新一代的電源管理元件,本應用筆記將闡述增强型氮化鎵元件的一般工作原理、閘極驅動器技術、電路的佈局、散熱管理技術和測試産品時所需要考慮的各項因素。

氮化鎵場效應電晶體和矽基氮化鎵技術的一般說明

結構

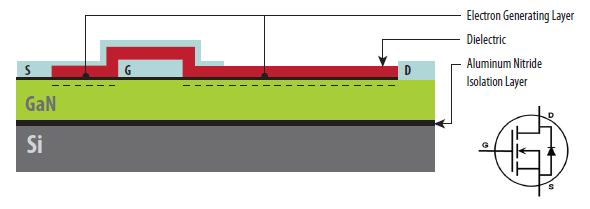

圖 1:宜普電源轉換公司的氮化鎵功率電晶體的結構。

要實現一個元件的成本效益可以從使用目前的生產基礎設施及使用較少生產步驟的製程開始。我們在較低成本的低分辨率CMOS代工廠生產氮化鎵場效應電晶體(eGaN FET)。宜普電源轉換公司的產品的製程始於在矽晶圓上增加一層非常薄的氮化鋁(AlN)層,從而把元件的結構和基板隔離。在這層上面增加一層具有非常高阻抗性的氮化鎵層,我們就是在這氮化鎵層上構建氮化鎵電晶體。再在氮化鎵層上增加一層氮化鎵鋁(AlGaN)層,它會對氮化鎵層產生擠壓。由於氮化鎵具備壓電特性,因此被擠壓時會將電子吸附到氮化鎵的表面。集中在一起的電子被稱爲二維電子氣(2DEG)。進一步的製程是在閘極下方形成一個耗盡區域,然後增加數層金屬層,從而將三個端子——閘極、汲極和源極連接起來。圖1展示了氮化鎵元件的結構的截面圖。這種結構被重複多次而構建成一個功率元件。結果是爲功率開關提供了一個簡單易用、精巧及具備成本效益的解決方案。除了一些差異外,氮化鎵元件的行爲與矽MOSFET相似,我們將稍後討論這些差異。

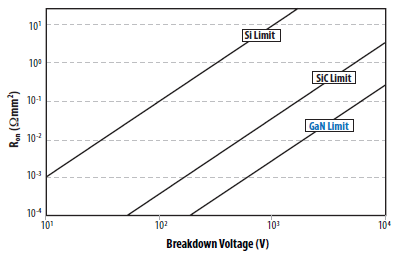

圖 2:電阻與崩潰電壓的關係。

要構建一個較高壓的元件,需要增加汲極和閘極之間的距離。由於二維電子氣的阻抗性很低,因此與矽元件相比,增加阻斷電壓能力對阻抗的影響要小很多。圖2顯示了氮化鎵、碳化矽和矽元件的導通電阻和阻斷電壓的折衷。矽MOSFET技術在經歷了30年的發展後已經接近它的理論極限,其進程減慢至在性能上要取得很小的增益也需要投放很高的開發成本。反觀年輕的氮化鎵技術,從宜普電源轉換公司推出的第一代至第四代eGaN FET可以看到,這種技術的發展非常迅速。

工作原理

宜普電源轉換公司的eGaN FET的行爲與矽功率MOSFET非常相似。在閘極上施加一個相對於源極的正向偏置會産生一個吸附電子的場效應,從而在汲極與源極之間構成一個雙向的通道。當從閘極除去偏置時,閘極下方的電子將擴散進氮化鎵層,從而重新構成一個耗盡區域,使元件再次具備阻斷電壓的能力。圖3和圖4分別顯示了EPC2001的轉換特性,以及RDS(ON)與VGS之間的關係。轉換特性顯示出隨VGS變化的電流能力。這是與MOSFET非常相似的地方,除了具備相同RDS(ON)的氮化鎵場效應電晶體的跨導(did/dvgs)高出很多外。RDS(ON) 與VGS的關係曲綫表明,當VGS在4 V以上時,RDS(ON)的變化不大,即是該曲綫變得相當平坦。

汲極至源極的最大額定電壓

汲極至源極的最大崩潰電壓(BVDSS)可以在宜普電源轉換公司的氮化鎵電晶體數據表內找到。

當具備電感性的負載在開關時,必需留意這類負載有可能因爲具備電感性“kickback”而使汲極電壓超過最大的額定值。這種現象將引致汲極電壓增加至超過崩潰電壓及從元件的電感器散熱。宜普電源轉換公司的氮化鎵電晶體的額定值不是針對雪崩模式操作,但在5 ms或以下的周期、10,000次循環下,氮化鎵元件的過衝是元件的BVDSS 的20%。如果元件被置於較高壓或更多次重複循環條件下,就必需使用合適的有源或無源鉗位/緩衝器來限制VDS上升至一個安全的水平。另外,必需使用合適的佈局技術來限制電路的寄生電感,從而限制系統中所含有的雜散電感性能量。

閘極驅動器

氮化鎵場效應電晶體與矽元件不同的是它具備明顯更快速的開關特性,從而對閘極驅動器、佈局和散熱管理的要求有所不同,而這些因素都相互影響。

不要超過閘極驅動器的最大額定值

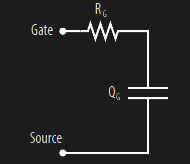

圖5:宜普電源轉換公司的氮化鎵功率電晶體的閘極結構。

從圖4可以看到,要全面增强元件的通道,在閘極和源極之間可以施加4 V或以上的電壓,同時在閘極至源極電壓的絕對最大值爲6 V。與功率MOSFET一樣,等效的閘極電路具備低閘極電阻和小閘極電容(如圖5所示)。如果使用半橋配置,要注意不要讓閘極發生過壓或欠壓。

dv/dt抗擾度

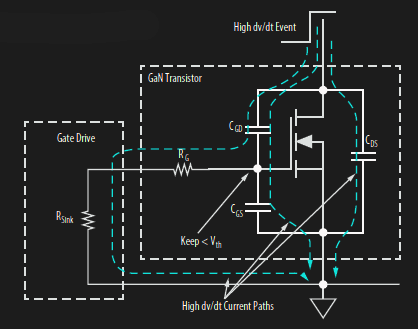

圖6:在關斷時,發生dv/dt的情况時對元件的影響,以及爲了避免由米勒所引致的擊穿(shoot-through)的要求。

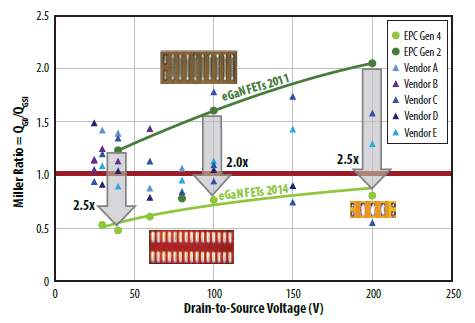

圖7:當元件的汲極至源極額定電壓是一半時,第二及第四代eGaN FET與先進矽MOSFET的米勒比的比較。

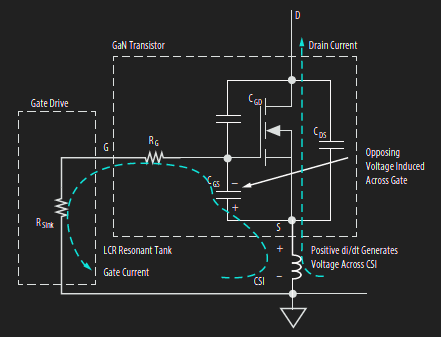

圖8:具有CSI並處於關斷狀態的元件的positive di/dt的影響

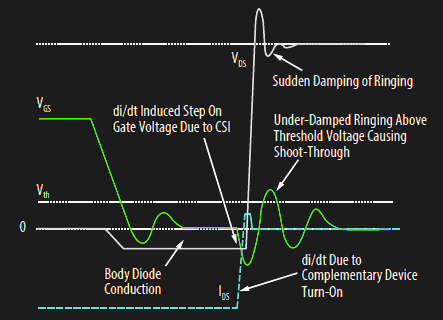

圖9:使用欠阻尼(under-damped)的閘極關斷電源迴路、處於關斷狀態的元件並由di/dt所引致的導通(擊穿)情况。

在硬開關和軟開關的應用中,在關斷狀態的元件的汲極有可能產生很高的正壓轉換速率 (dv/dt),元件的各個電容會被快速充電,如圖6所示。當發生dv/dt的情况時,汲極至源極電容(CDS)會被充電。同時,串聯的閘極至汲極(CGD)和閘極至源極(CGS)的電容也會被充電。如果不解决這個問題,經過CGD電容的電流將流過CGS,並在超過Vth電壓時對CGS充電,使元件會發生導通。這種事件有時被稱爲米勒導通,MOSFET用戶很清楚知道這會引致很大的耗損。

爲了確定一個功率元件是否容易發生dv/dt的情况,我們需要評估作爲汲極至源極電壓函數的米勒電荷比(QGD/QGS1)。小於1的米勒比理論上可以確保元件具備dv/dt抗擾能力[1]。從圖7我們可以看到,最新一代的氮化鎵場效應電晶體具備大幅减小了的米勒比,至少减小了兩倍,因此整個産品綫的米勒比在一半額定電壓時都是小於1。圖7中的三角形點顯示出目前矽MOSFET的米勒比,它們大致上都要比氮化鎵元件的米勒比高出很多。

di/dt抗擾度

如圖8所示,當處於關斷狀態的元件的電流上升時,在共源電感(CSI)會產生一個電壓階數。這種正向電壓階數會在CGS產生反向電壓。如果電流正在上升,這將導致閘極電壓變成一個負電壓。如果處於關斷狀態的閘極迴路LCR諧振電路的阻尼(damping)並不足够,這個在閘極上初步形成的負電壓階數將引致正向振鈴現象並導致不想發生的導通和擊穿,如圖9所示。

如果阻尼足够,閘極關斷迴路有可能避免這類di/dt導通,雖然最好有一定程度的欠激,就像之前所提及的dv/dt抗擾度那樣。然而,透過增加閘極下拉電阻來增加閘極關斷電源迴路阻尼可能會對dv/dt抗擾性產生負面的影響。因此,如果我們只是對具備臨界米勒電荷比的元件調整閘極電阻,這樣可能不足以避免di/dt和/或dv/dt導通。

要獲得更多關於電感對電路特性的影響的資訊,請參看「寄生電感對元件性能的影響」的文章。

下面是我們建議針對宜普公司的氮化鎵電晶體的閘極驅動器的主要特性。要控制器與氮化鎵場效應電晶體互相配合,它的驅動器也需要具備以下的特性:

- 接地反彈抗擾性能:閘極驅動器的設計應該假設驅動器接地和控制器接地可以顯著不同,而輸入邏輯引脚必需在邏輯狀態下不受由噪聲引致的變化所影響。

- 針對高側驅動器的高dv/dt抗擾度:用來將控制邏輯信號傳送到浮動高側元件的邏輯隔離器或電平移位器需要對高dv/dt上升和下降時間具備抗擾能力,從而不會改變邏輯狀態。在100 V或以下,元件具備50 V/ns的抗擾性能應該是足够的,而在較高電壓下,元件需要具備較高的dv/dt抗擾特性。

- 具備低電感的表面貼裝封裝和最佳的pin-out閘極驅動器需要靠近高速氮化鎵元件並互相連接,從而把互連阻抗降至最低。這需要與氮化鎵電晶體配合的pin-out和封裝。與傳統使用焊綫接合的封裝相比,我們推薦使用倒裝晶片的WLCSP封裝或DFN/QFN封裝。與氮化鎵電晶體配合的pin-out把VBS/HG/VSW相互放置在旁邊,及把VCC/LG/PGND也相互放置在旁邊。

- 把閘極電源回路電感减至最低:我們在設計閘極驅動器時,應該把在VDD電源電容和實際閘極驅動器的功率元件(sink和source元件)之間的電感减至最低。這樣可以把閘極驅動器的上升時間减至最短,以及實現驅動器di/dt最大值。要驅動具備50pF範圍內的輸入電容的小型第三代氮化鎵元件,我們最好使用具備上升和下降時間都在500ps範圍或以下的驅動器。

- 閘極驅動强度:對於作一般用途的氮化鎵驅動器,驅動器的速度需要與被驅動的元件的尺寸和速度配合。這種靈活性的要求需要一個具備低阻抗的閘極驅動器並配合可選的外部電阻。我們推薦的閘極驅動强度是具備1Ω至3Ω的上拉/下拉阻抗。如果阻抗高於這個範圍的話,元件的速度會變得太慢(或限於在較低功率的應用);如果阻抗比這個範圍低出很多的話,有可能出現振鈴的問題——特別是當元件使用具備高電感和焊綫接合式的封裝時。

- 調整閘極驅動的電源電壓:低側驅動器和尤其是高側驅動器必需調整閘極驅動的電源電壓以避免在電晶體管的閘極上發生過壓的情况。閘極驅動的最大值應該是5 V±0.5 V,而我們推薦5 V±0.25 V。

- 死區時間:把死區時間減至最短可以減低‘體二極體’正向電壓的損耗。死區時間最好在20 ns或以下。要獲得更多關於eGaN FET的死區時間的管理資訊,請參看「最佳死區時間以取得最佳效率」的文章。

- 元件工作在高頻下:eGaN FET可以在10 MHz頻率以上開關。工作在高頻的最佳閘極驅動器需要具備最短的導通時間、接地和高側電源之間具備最小的內部電容,以及具備最小的反向恢復的自舉電源,例如使用一個外部的肖特基二極體。要獲得更多關於驅動器對元件在高頻工作時的影響,請參看「在高頻工作的硬開關轉換器」的文章。

更詳細的討論請參看「eGaN® FET 的驅動器及版圖的考慮因素」的文章。與增强型氮化鎵元件兼容的IC的列表,請瀏覽我們的網站,網址是www.epc-co.com/epc/tw/產品/給eGaN的驅動器及控制器.aspx。

佈局的考慮因素

由於宜普電源轉換公司的氮化鎵電晶體具備快速開關和大電流承載能力的特性,因此在設計印刷電路板並使用這些元件時需要考慮一些額外的因素。讓我們看看一個降壓轉換器的例子來說明一下。

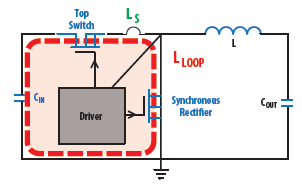

圖10:具有寄生電感的同步降壓轉換器。

在一個實際的降壓轉換器中,有兩種主要的寄生電感會對轉換器的性能構成重大的影響(如圖10所示):

1. 共源電感(Common Source Inductance - LS)是指汲極至源極電流路徑和閘極驅動迴路重叠所産生的電感。

2.高頻迴路電感(LLOOP)是一種功率轉換迴路電感,它由多種寄生電感組成,包括來自輸入電容的正極並經過頂部元件、同步整流器、接地迴路和輸入電容。

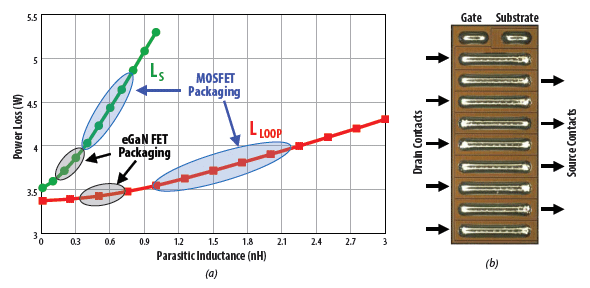

圖11:a)寄生電感對功率損耗的影響(V

IN = 12 V、 V

OUT = 1.2 V、I

OUT = 20 A、 F

SW = 1 MHz) 上面開關元件:

EPC2015、同步整流器 EPC2015 。b)使用LGA封裝的eGaN FET 。

共源電感(LS)已經被表明爲影響元件性能的關鍵參數,因爲它直接影響元件的驅動速度([2]-[4])。共源電感主要受元件的封裝電感所控制,而不同的封裝具有不同的電感([5]、[6])。eGaN FET所使用的LGA封裝(如圖11b所示)具有低共源電感,從而可以減少損耗,如圖11a所示。

高頻迴路電感(LLOOP)影響開關轉換時間和元件的汲極至源極的峰值電壓。印刷電路板的佈局和元件封裝的電感控制了高頻迴路電感。如果在應用中使用具備低封裝寄生電感的元件,例如採用LGA封裝的eGaN FET,印刷電路板的佈局將成爲影響高頻迴路電感的主要因素([7]-[10])。

由於eGaN FET大幅降低來自封裝的電感,因此可以把CSI降至最低而它不再是構成寄生損耗的主要因素。由印刷電路板的佈局所控制的高頻迴路電感則成爲構成寄生損耗的主要因素,使得採用eGaN FET的印刷電路板的佈局對元件在高頻時的性能的影響至關重要。

eGaN FET使用最佳佈局以减小寄生電感

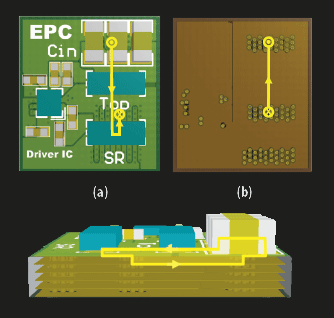

圖12:我們推薦採用eGaN FET的最佳電源廻路a)頂視圖 b)第一層內層的頂視圖 c)側視圖。

爲了使eGaN FET具備高速開關的特性,它們採用LGA封裝,這種封裝不只是具備較低內部電感,而且能够幫助用戶設計具備超低電感的電路板。針對eGaN FET我們推薦的最佳佈局非常優越,包括可實現減小了的迴路面積、自動抵消電場、不受電路板的厚度所影響的電感、單面印刷電路板設計,以及高效多層結構。這種設計將第一層內層用作大電流迴路路徑,如圖12 b所示。這個迴路路徑位於頂層的功率廻路的下方,如圖12a所示,從而可以使用最小的迴路面積並具備自動抵消電場特性。圖12c的側視圖所展示出的概念是在使用多層結構的印刷電路板上構建出纖薄型的自動抵消迴路。

改善了的佈局把輸入電容靠近上方的元件,而正輸入電壓端子則處於上方的eGaN FET的汲極連接的旁邊。eGaN FET處於與橫向及垂直功率迴路案例的相同位置。在兩個eGaN FET之間是一連串交錯式開關節點和接地過孔,它們的排列方式與用作同步整流器的eGaN FET的LGA脚片匹配。交錯式的開關節點和接地過孔重複地排列在同步整流器的底部。

這些交錯式過孔提供了三大優勢:

1)位於兩個eGaN FET之間的一組過孔,可以縮短高頻廻路電感路徑,從而實現較低的寄生電感。

2)位於同步整流器eGaN FET的下方有一組過孔旨在提供額外過孔,使同步整流器eGaN FET可以降低電阻及導通損耗。

3)另外的交錯式的過孔組具有反向電流,減低渦流及近接效應,並且降低交流的導通損耗。

散熱考慮

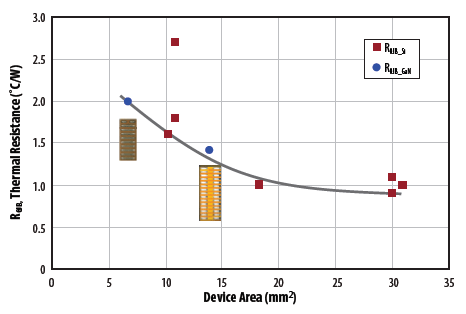

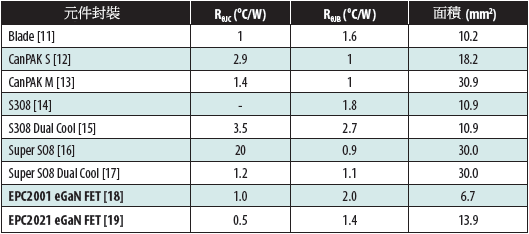

具備高功率密度的元件必需不只是因爲能够產生更少的熱量而變得高效,而是可以實現優越的導熱性能。封裝的散熱效率可以從比較RɵJC和RɵJB這兩個參數來確定,該參數並與封裝面積作出比較。RɵJC是從結點至外殼的熱阻值,這是從eGaN FET的有源部份至矽基板的頂部(包括側邊)的熱阻值。RɵJB是結點至電路板的熱阻值,這是從eGaN FET的有源部份至印刷電路板的熱阻值。對於這個路徑來說,熱量必需通過錫條散至電路板的銅綫。表1比較了數個受歡迎的表面貼裝MOSFET封裝和兩個受歡迎的eGaN FET封裝的散熱特性。

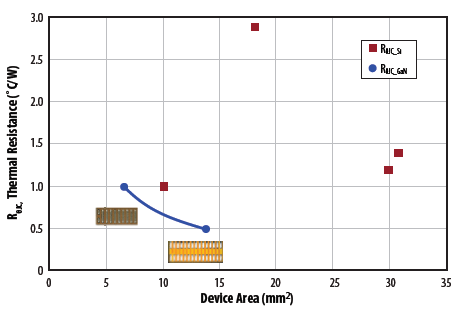

圖13:從表1所列出的不同封裝的結點至電路板的熱阻值(R

ƟJB)。藍色圓點代表eGaN FET的熱阻值。紅色方型點代表矽MOSFET的熱阻值。

圖13顯示了表1所列出的每種封裝的結點至電路板的熱阻值(RƟJB)。紅色方型點代表MOSFET封裝的熱阻值,藍色圓點代表eGaN FET封裝的熱阻值。我們可以看到,大多數的封裝範例都落在單條趨勢綫上,這表明熱阻主要取決於封裝尺寸而不是封裝技術。相反地,圖14顯示了從結點至外殼的熱阻值(RƟJC)。與Blade封裝或eGaN FET封裝相比,CanPAK和用雙面散熱方式的SO8封裝從封裝頂部散熱的效率都低很多。當標準化至相同面積後,eGaN FET的電阻值要比Blade[11]還要低出30%以上。因此,eGaN FET的雙面散熱封裝成爲最高效的散熱封裝,而且最適合用於高功率密度的電源設計。

表1:封裝面積與R

ɵJC、R

ɵJB熱阻值的比較

圖14:從表1所列出的不同封裝的結點至外殼的熱阻值(R

ƟJC)。藍色圓點代表eGaN FET的熱阻值。紅色方型點代表矽MOSFET的熱阻值。

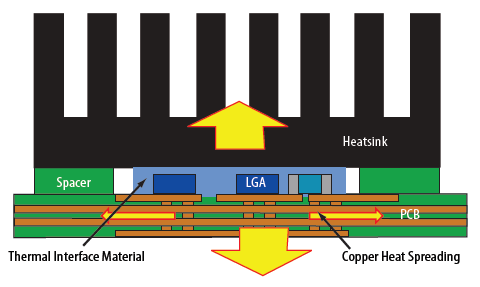

宜普電源轉換公司的氮化鎵電晶體的另外一個優勢是在兩個散熱路徑都可以改善熱阻,如圖15所示。首先,通過額外的散熱過孔可以減小電路板至環境的熱阻,但連接內部和外部銅層的散熱過孔是以橫向方式散熱。此外,可以利用以下兩種方法減小散熱接面材料(TIM)的阻抗:

圖15:表面貼裝在印刷電路板上、用LGA封裝的氮化鎵電晶體的雙面散熱示意圖展示出頂部散熱器及散熱過孔,熱量經電路板散出。

1) 減小元件至散熱器接面的厚度:一般來說除了散熱接面材料外,在散熱器和元件之間還要同時使用某種墊片,因爲焊接散熱器時的力度不能按壓到元件,以免元件發生破裂的情况。這種墊片形成了散熱器和氮化鎵元件之間所需要的最短距離。

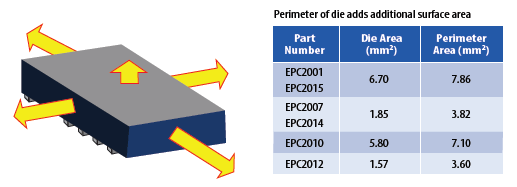

2) 使用散熱接面材料包圍整個元件而不只是它的頂部(外殼):這樣可以減小熱阻,因爲元件周邊的總面積比它的頂部面積還要大,如圖16所示。

圖16: 用LGA封裝的氮化鎵電晶體的晶片面積及晶片的周邊面積。

使用雙面散熱方式、强制空氣散熱和使用獨特的印刷電路板材料,例如DBC(直接結合的銅金屬) [20]或絕緣金屬基板(IMS)都有可能進一步改善元件的散熱性能。

使用元件模型來模擬電路行爲

雖然增强型元件的工作原理與矽MOSFET非常相似,但是我們不能使用基於物理特性的傳統MOSFET模型來構建氮化鎵元件模型,因爲氮化鎵電晶體的物理特性與MOSFET的分別很大。宜普電源轉換公司開發的增强型氮化鎵電晶體的模型[21]混合了物理特性和現象學功能,構建出緊凑型的spice模型,它具備可接受的模擬和聚合特性,其傳導和臨界參數已包括溫度的影響。圖17展示了增强型氮化鎵電晶體的基本等效電路。主要元素包括由電壓控制的電流電源ID、電容CGD、CGS和CDS,以及終端電阻RS、RD和RG。

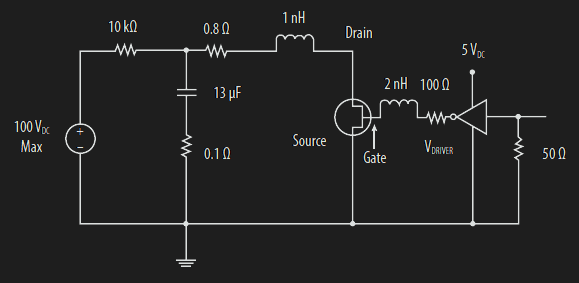

爲了演示元件模型和電路的考慮因素,我們搭建並測試了一種簡單的電路來對元件的性能與模型所預測的性能作出比較(見圖18)。

圖18:基本演示電路的原理圖。

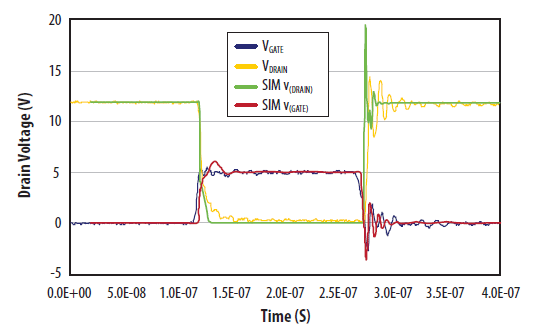

圖19:模擬與測量所得的演示電路的比較。

電路中包含一個電壓電源,它使用一個10 k Ω電阻對一個13μF的電容充電。該電阻將電壓電源和測試元件隔離。氮化鎵電晶體由一個5 V脉衝進行驅動,電容則通過一個0.8 Ω的電阻和具有0.1 Ω的雜散電阻的元件進行放電。比較演示電路的不同模擬結果表明與測量值合理地相對應。雖然不是完美,高精度的模型複製了過衝和振鈴現象。圖19顯示了叠加閘極和汲極電壓與測量電路和模擬電路的時間的關係。

宜普電源轉換公司開發的模型準確地複製了元件工作時電路的基本反應。該些元件模型可以在網站下載,網址是(www.epc-co.com/epc/tw/設計支援/器件型號.aspx)。

曲綫追蹤儀和自動測試的考慮因素

宜普電源轉換公司的增强型氮化鎵電晶體的行爲一般很像N通道功率MOSFET。用於N通道功率MOSFET的常用曲綫追蹤儀、參數分析儀及自動化分立式元件的參數測試儀都可以用來找出氮化鎵電晶體的特性。下面是針對表徵DC參數的通用指南,它使用了Tektronix 576曲綫追蹤儀、Keithley 238參數分析儀或TESEC 881-TT/A分立式元件測試系統。

圖20: 100 V eGaN FET在使用閘極電容和沒有使用閘極電容時的V

TH曲綫的比較。

注意:氮化鎵電晶體易受靜態參數影響。氮化鎵電晶體具有很小的電容和低的最大閘極電壓。必須使用腕帶、接地墊和其他ESD預防措施,從而避免超過元件的最大額定值。

測量VTH值

VTH 值是指閘極至源極的電壓(VDS = VGS),它產生數據手册上所刊載的特定汲極電流。該測試通常是在汲極和閘極短路時進行。

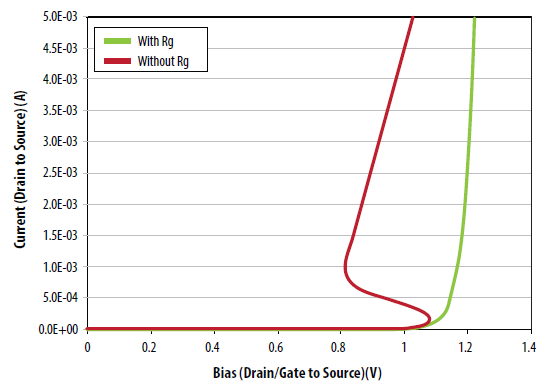

進行VTH曲綫追蹤儀測試要注意的事項:

如果在測量VTH期間的閘極沒有串聯電阻(RG),你可能會在閘極上看到振蕩現象,從而形成圖20所示的那種典型S曲綫。振蕩電壓有可能變成比輸入電壓高出很多倍。這些振蕩現象可以破壞或毀掉元件。

測量IGSS值

IGSS值代表汲極短路至源極時,閘極至源極的漏電流。閘極上的正向電壓不要超過6V,或者負向電壓不要超過4 V,因爲這是元件的閘極的最大額定值。爲了精確地測量出IGSS值,在汲極和源極之間具有非常低的短路阻抗是非常重要的。我們不建議利用自動測試儀對IGSS進行測試時使用Autorange的功能,例如使用 TESEC 881-TT/A,因爲在測試期間改變範圍可能導致峰值電壓,從而有可能毀掉閘極。

測量RDS(ON)值

RDS(ON)是指VGS爲5 V時汲極至源極的阻抗。由於RDS(ON)易受溫度影響,因此在測試時必需把結點的熱量減至最小。所以我們通常使用汲極脉衝的測試方法來測量出RDS(ON)值。精確的RDS(ON)測量需要在汲極和源極使用Kelvin Sense。檢測點的位置對RDS(ON)的讀數的影響很大。我們不建議利用自動測試儀對RDS(ON)進行測試時使用Autorange的功能,例如使用 TESEC 881-TT/A,因爲在測試期間改變範圍可能導致峰值電壓,從而可能毀掉閘極。

我們不建議在裸片上使用探針測量RDS(ON)。如果在探針/焊球接觸點具有太高的電流密度,可能會破壞元件。

測量IDSS / BVDSS值

BVDSS是VGS = 0 V時元件的額定電壓。IDSS是在特定的汲極至源極電壓的汲極電流,相等於或低於元件在V = 0 V時的額定電壓。宜普公司的氮化鎵元件的真正擊穿電壓通常遠高於元件的最大汲極至源極的額定電壓值。所以最好不要對元件進行BVDSS測試,因爲會超過BVDSS的最大額定值。如果超過了最大額定值,元件的RDS(ON)會劣化。此外,很重要的是要將閘極和源極短路以避免閘極相對於源極懸浮而使元件意外地導通。如果在IDSS測試過程中發生這種情况,有可能破壞元件。

就像與測量IGSS和RDS(ON)一樣,我們不建議利用自動測試儀對IDSS進行測試時使用Autorange的功能,例如使用 TESEC 881-TT/A,因爲在測試期間改變範圍可能導致電壓尖峰,從而可能毀掉閘極。也必需避免使用「Function BVDSS」,因爲在固定的汲極電流下,測量所得的汲極至源極電壓有可能超過元件的VDS的最大額定值。用戶在測量IDSS時應首先確定以上提及的電壓測試裝置沒有尖峰。我們建議使用受控的電壓斜坡來幫助避免發生電壓過沖。

最後要注意的事項

一個元件如何可以簡單易用取决于用戶的技巧、開發中的電路的困難程度、新元件與用戶使用過的元件的差異,以及有沒有可以幫助用戶使用新元件的工具。

新一代增强型氮化鎵電晶體的行爲與現有的功率MOSFET是非常相似的,只是前者的速度更快,因此用戶可以充分利用他們的設計經驗來使用氮化鎵元件,設計出具備更高性能的産品。與矽MOSFET相比,eGaN FET具備相對地較高的頻率響應,不僅在性能上得以躍升,它是用戶在設計電路版圖時的另一個可考慮的高效元件。

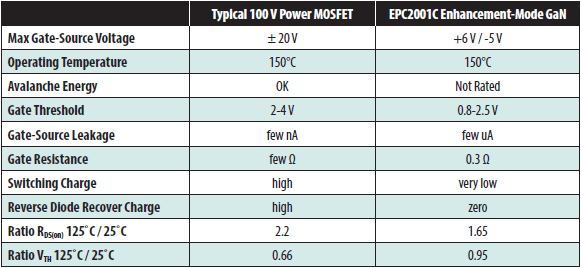

另一方面,氮化鎵元件還具備多個特性使得它比以前的矽元件更爲簡單易用。舉例來說,它的臨界值電壓幾乎在寬闊範圍的溫度下不會産生變化,而導通電阻的溫度係數也要比矽元件低出很多。

表2: 總結100 V 矽功率 MOSFET 與100 V eGaN FET的比較。

我們在上面的列表總結了矽功率MOSFET與EPC2001C氮化鎵電晶體的基本特性的比較。簡單易用的工具也可以使全新元件易於使用。宜普電源轉換公司開發了全套元件模型,可供用戶下載使用。這些模型相當可靠地預測電路的性能,從而可以提高工程師的生産力並可以快速地把産品推出市場。

我們的應用筆記和設計提示匯集了工程師們多年以來的集體經驗和智慧。我們的網上圖書庫收集了豐富的應用筆記、白皮書及學術期刊(www.epc-co.com/epc/cn/氮化鎵技術圖書館.aspx)。此外,「氮化鎵晶體管-高效功率轉換器件」(第二版)現已出版[22],它是一本對氮化鎵技術及其應用作詳盡的闡釋及分析的教科書。

功率MOSFET還沒有出局,但它在性能和成本方面的改進已經走到盡頭。在未來的十年內,由於氮化鎵電晶體在性能和成本方面極具優勢,因此它將成爲主導技術,並且隨著我們進一步縮短氮化鎵技術的學習曲綫,氮化鎵與MOSFET技術的績效差距將逐漸擴大。

參考資料

- Wu, T. “Cdv/dt Induced Turn-On In Synchronous Buck Regulators”, white paper, International Rectifier Corporation

- A. Elbanhawy, “Effects of parasitic inductances on switching performance,” in Proc. PCIM Eur., May 2003, pp. 251–255.

- G. Nobauer, D. Ahlers, J. Sevillano-Ruiz, “A method to determine parasitic inductances in buck converter topologies,” in Proc. PCIM Eur., May 2004, pp. 37–41.

- B. Yang, J. Zhang, “Effect and utilization of common source inductance in synchronous rectification,” in Proc. IEEE APEC’05, Mar. 2005, vol. 3, pp. 1407–1411.

- M. Pavier, A. Woodworth, A. Sawle, R. Monteiro, C. Blake, and J. Chiu, “Understanding the effect of power MOSFET package parasitic on VRM circuit efficiency at frequencies above 1 MHz,” in Proc. PCIM Eur., May 2003, pp. 279–284.

- D. Reusch, D. Gilham, Y. Su and F.C. Lee, “Gallium nitride based multi-megahertz high density 3D point of load module,” APEC 2012. pp.38-45. Feb. 2012.

- T. Hashimoto, T. Kawashima, T. Uno, Y. Satou, N. Matsuura, “System in package with mounted capacitor for reduced parasitic inductance in voltage regulators,” Applied Power Electronics Conference and Exposition, 2008. APEC 2008. Twenty-Third Annual IEEE, pp.187-191, 24-28 Feb. 2008.

- Y. Kawaguchi, T. Kawano, H. Takei, S. Ono, A. Nakagawa, “Multi Chip Module with Minimum Parasitic Inductance for New Generation Voltage Regulator,” Power Semiconductor Devices and ICs, 2005.

- A. Ball, M. Lim, D. Gilham, F.C Lee, “System design of a 3D integrated non-isolated Point Of Load converter,” Applied Power Electronics Conference and Exposition, 2008. Twenty-Third Annual IEEE, pp.181- 186, 24-28 Feb. 2008.

- D. Reusch, F.C. Lee, Y. Su, D. Gilham, “Optimization of a High Density Gallium Nitride Based Non- Isolated Point of Load Module,” Energy Conversion Congress and Exposition (ECCE), IEEE, Sept. 2012.

- Infineon Blade BSN012N03LS datasheet, www. infineon.com

- Infineon CanPAK S-size BSF134N10NJ3 G datasheet, www.infineon.com

- Infineon CanPAK M-size BSB012N03LX3 G datasheet, www.infineon.com

- Infineon S3O8 BSZ075N08NS5 datasheet, www.infineon.com

- Texas Instruments S308 Dual Cool SON 3.3x3.3mm CSD16323Q3C datasheet, www.TI.com

- Super SO8 BSC010N04LS datasheet, www.infineon. com

- Texas Instruments Super SO8 Dual Cool SON 5x6mm CSD16321Q5C datasheet, www.TI.com

- Efficient Power Conversion EPC2001 datasheet

- Efficient Power Conversion EPC2021 datasheet

- D. Reusch, “High Frequency, High Power Density Integrated Point of Load and Bus Converters,” Ph.D. dissertation, Virginia Tech, http://scholar.lib. vt.edu/theses/available/etd-04162012-151740/ 2012.

- R. Beach, A.Babakhani, R. Strittmatter, “Circuit simulation using EPC device models,” epc-co.com/epc/documents/product-training/Circuit_Simulations_ Using_Device_Models.pdf

- A. Lidow, J. Strydom, M. de Rooij, D. Reusch “GaN Transistors for Efficient Power Conversion,” Second Edition, Wiley, ISBN 978-1-118-84476-2.

Download pdf version

Download pdf version