より良いパワー・パッケージ

GaNトランジスタは、シリコンの対応品よりも、はるかに小型です。サイズに関するこの利点は、生産者には追加のコスト・メリットになり、ユーザーにも追加のコスト・メリットになります。プリント回路基板の土地は非常に高価です。より小型のデバイスは、より小さな面積で済みます。GaNの小さな実装面積と優れた特性が、より大きなシリコン部品では実現不可能な新しい最終製品を可能にする例がいくつかあります。

高耐圧GaNトランジスタは横型構造なので、すべての電気接続はチップの同じ側に配置され、複雑さを軽減できます。縦型のSiパワーMOSFETで一般的な両面パッケージでは、特性が制限されます。チップスケール・パッケージは、抵抗、インダクタンス、大きさ、熱インピーダンス、およびパワー・トランジスタのコストを低減させるためのより効率的なパッケージの形です。これによって、回路内での比類のない特性を実現できます。

より良い特性、熱効率、そして信頼性

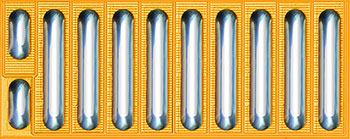

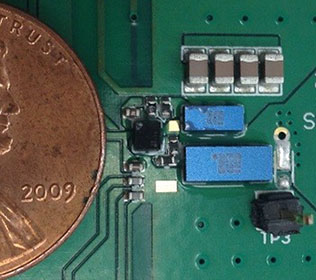

図1:eGaN® FETのEPC1001EPC1001(図1)は、2010年3月に初めて製品化され、チップスケール・パッケージの革命が始まりました。このデバイスは、標準的なシリコン基板の上に成長させた窒化ガリウム(GaN)の薄い層を形成しています。当社は、第1世代のディスクリート・トランジスタをGaNの中に形成し、このデバイスは、用途によりますが、最高のシリコンMOSFETよりも5~50倍も優れた特性が得られました。そして、プラスチック成形パッケージの代わりに、デバイスの表面に直接「はんだ付け可能なバー」を配置しました。この面をひっくり返して、プリント回路基板上に直接実装することができます(図2参照)。

図2:EPCの2個のeGaN FETがプリント回路基板にはんだ付けされています。裏面はシリコンです。

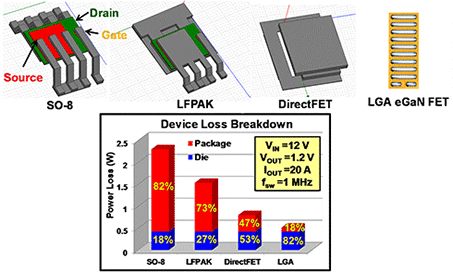

図3:SO-8、LFPAK、DirectFETなどの一般的なパワー・パッケージは、電力変換回路に、考慮すべき寄生インダクタンスを追加することになります。このインダクタンスは、パッケージ内部のトランジスタにおいて大きな損失を生じます。

図3は、一般的な電源において、一般的なシリコンMOSFETパッケージの内部インダクタンスが及ぼす電力損失への影響を示しています。この場合、パッケージの内部インダクタンスがデバイスのオンとオフを遅くするので、トランジスタは、より大きなスイッチング損失を生じます。一般的なSO8パッケージでは、デバイスで発生する全損失の80%を占めます。最も効率的なパッケージであるDirectFETでさえ、デバイスの損失を2倍にします。チップスケールのデバイスEPC2001Cでは、デバイスの下のプリント回路基板上のトレースのインダクタンスによる20%未満の損失が追加されます。より低損失、より少ない発熱、より高い電力変換効率。そう、チップスケール・パッケージは、デバイスに対して、いかなる不要な抵抗も追加しません。パッケージの抵抗は、最先端の低耐圧シリコンMOSFETの抵抗を20%~50%増加させます。純粋な損失です。

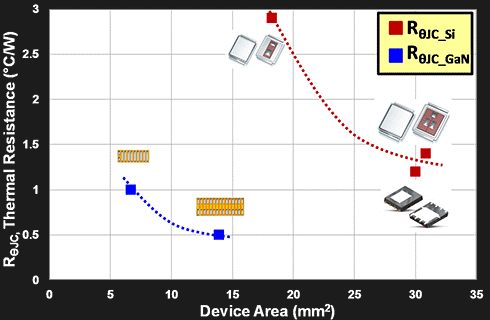

図4は、eGaN FET、両面QFN、DirectFETの比較です。図中、縦軸はデバイスから周囲への熱抵抗で、横軸はデバイスのサイズです。抵抗が低いほど良く、チップスケール・「パッケージ」に収めたeGaN FETは、はるかに優れています。これは、驚きではありません。なぜなら、動作中のデバイスと周囲環境との間のすべての壁を排除することは、外の世界への最も直接的な経路を加熱することになるからです。

図4:チップスケール・パッケージは、シリコンの最も効率的なパワー・パッケージよりも熱抵抗が小さくなっています。

14年で2380億デバイス時間にわたって、EPCのeGaN FETとICは、たった3回の故障であり、フィールドで前例のない信頼性の記録を示しました。トラックのヘッドランプ、自動運転車への搭載、4G / LTE基地局内、DC-DC電源内のいずれにおいても、eGaN FETは、1FIT(10億デバイス時間ごとの故障)以下の合計フィールド故障率を示しています。