A Better Power Package

GaN transistors are much smaller than their silicon counterparts. This size advantage translates into additional cost benefits to the producers, translating into additional cost benefits to the user. PCB real estate is very expensive. Smaller devices mean less real estate. In some cases, the smaller footprint and greater performance of GaN enables a new end product not possible with larger silicon parts.

For high voltage lateral GaN transistors, all of the electrical connections are located on the same side of the die, allowing for the elimination of complex, performance limiting two sided packaging common in vertical Si power MOSFETs. Chip-scale packaging is a more efficient form of packaging that reduces the resistance, inductance, size, thermal impedance, and cost of power transistors, enabling unmatched in-circuit performance.

Better Performance, Thermal Efficiency and Reliability

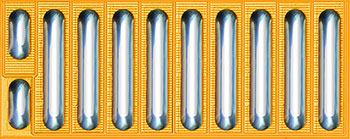

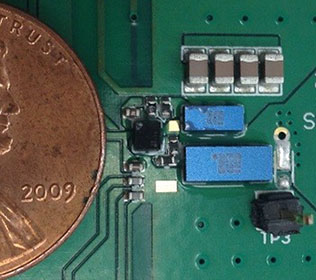

Figure 1: EPC1001 eGaN® FETThe EPC1001 (figure 1) was first introduced in March 2010 and began the chip-scale packaging revolution. This device has a thin layer of gallium nitride (GaN) grown on top of a standard silicon substrate. Inside the GaN we fabricated a first-generation discrete transistor that performed 5 – 50 times better than the best silicon MOSFETs, depending upon the application. And, instead of a plastic molded package, we put “solderable bars” directly on the surface of the device. Flip this part over and it can be mounted it directly onto a PCB (See figure 2).

Figure 2: Two EPC eGaN FETs are soldered to a PCB. The back surface is silicon.

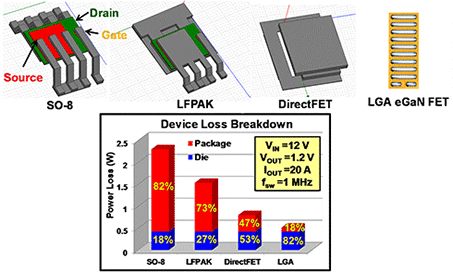

Figure 3: Popular power packages such as the SO-8, LFPAK, and DirectFET add considerable parasitic inductance to a power conversion circuit. This inductance induces large losses in the transistor inside the package.

Figure 3 shows the impact of just the inductance inside the common silicon MOSFET packages on the power losses in a common power supply. In this case, the internal package inductance causes the devices to turn on and off slower and therefore the transistor generates higher switching losses. The popular SO8 package induces losses that amount to 80% of the total losses incurred in the device. Even the most efficient package – the DirectFET – doubles the losses in the device. The EPC2001C chip-scale device has less than 20% losses added due to inductance in the traces on the PCB under the device. Lower losses, less heat, higher power conversion efficiency. Oh, and the chip-scale package also doesn’t add any unwanted resistance to the device. Package resistance can add 20-50% to the resistance of a low voltage state-of-the-art silicon MOSFET. Pure loss.

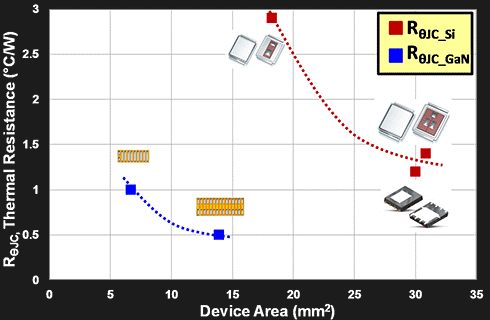

Figure 4 is a comparison between eGaN FETs, double-sided QFNs, and DirectFETs. In the figure, the vertical axis is the thermal resistance from the device to the ambient and the horizontal axis is the device size. The lower the resistance the better, and eGaN FETs in chip-scale “packages” are much better. It is not a surprise, because eliminating all barriers between the active device and the ambient environment gives heat the most direct path to the outside world.

Figure 4: Chip-scale packages have lower thermal resistance than the most efficient silicon power packages.

Over 14 years and 238 billion device hours, eGaN FETs and ICs from EPC have demonstrated an unprecedented record of reliability in the field with only three failed failures. Whether in truck headlamps, onboard autonomous vehicles, inside 4G/LTE base stations, or within DC-DC power supplies, eGaN FETs have demonstrated a total field failure rate of under 1 FIT (Failures every billion device hours).

Application Notes and White Papers

Chip-Scale Package Reference Material

Chip-Scale Package Related Web Sites